FPGA布线拥塞主要原因及解决方法

judy 在 周一, 08/22/2022 - 10:00 提交

在FPGA开发设计中,我们可能会经历由于资源占用过高的情况,例如BRAM、LUT和URAM等关键资源利用率达到或超过80%

在FPGA开发设计中,我们可能会经历由于资源占用过高的情况,例如BRAM、LUT和URAM等关键资源利用率达到或超过80%

自适应计算,这一创新理念可以给行业带来什么?加入AMD之后,赛灵思(Xilinx)给出了更丰富的答案。

在光纤通信开发中,ibert ip会经常用到,它不但可以用来测试误码,测试眼图,还可以通过调整参数使眼图达到比较理想的状态。

该项目基于AMD Xilinx Varium C1100 FPGA加速卡,为 Filecoin 区块链应用中的Poseidon哈希算法提供了一套完整的硬件加速方案。

hsSynth打破对大规模设计进行完整综合的执行惯性,对用户RTL级设计进行模块级拆分定义

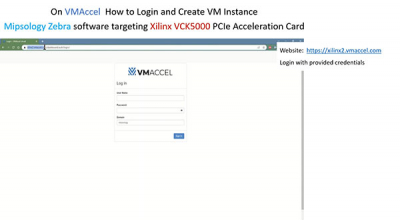

参阅分步说明,登录并创建面向 Xilinx VCK5000 PCIe 加速卡的 Mispology Zebra AI 软件实例。

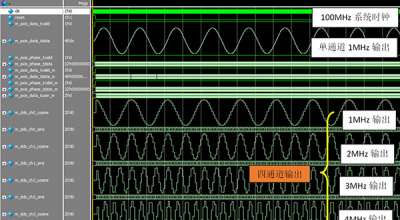

本文我们通过例化Xilinx公司的DDS IP核来产生混频器本振输入频率,并给出Modelsim仿真测试结果。

本文介绍Xilinx® UltraScale FPGA实现LVDS 1:7接收数据解串

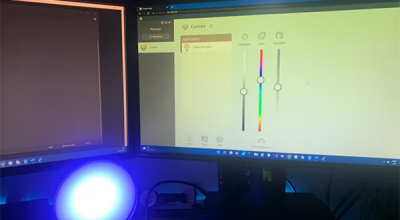

使用 PYNQ 和 Zigbee 创建一个简单且可扩展的家庭自动化系统。

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制