百度大脑EdgeBoard边缘AI计算盒带你领略人体分析的魅力

judy 在 周三, 04/07/2021 - 10:37 提交

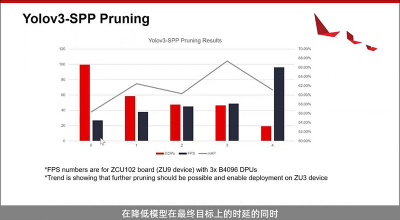

百度大脑EdgeBoard AI计算盒/计算卡系百度与米尔联合推出的一款高性能,高可靠性的AI计算盒/计算卡。该产品基于Xilinx Zynq UltraScale+ MPSoC 系列 FPGA可伸缩计算架构,可支持二次开发,支持高精度模型/多模型部署

百度大脑EdgeBoard AI计算盒/计算卡系百度与米尔联合推出的一款高性能,高可靠性的AI计算盒/计算卡。该产品基于Xilinx Zynq UltraScale+ MPSoC 系列 FPGA可伸缩计算架构,可支持二次开发,支持高精度模型/多模型部署

作为自适应计算的领导者,赛灵思技术日活动将于4月22日来到深圳。届时,赛灵思技术专家将到场分享 FPGA/SoC 领域的创新可能。同时,丰富的干货课程有助于 AI 与软件领域从业者迅速掌握赛灵思全新的 Vitis/Vitis AI 统一软件平台。

本次大会,赛灵思将以“驶向未来,自适应计算赋能智能驾驶”为主题,通过3场主题演讲、10场案例演示及2场现场直播,为观众展示赛灵思及其生态合作伙伴们面向智能驾驶场景而研发的前沿产品、技术和解决方案。

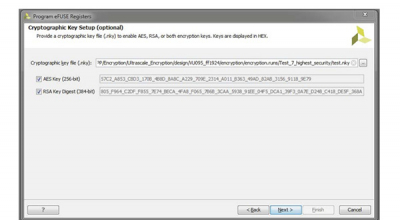

本文描述了使用 Vivado® 设计套件生成加密位流和加密密钥的分步过程。

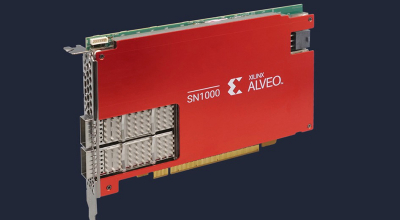

数字化经济和数字化转型离不开数据中心,数据中心的建设未来该如何进行?如何满足不同企业对于数据中心的需求?在这一背景下,赛灵思召开了数据中心春季媒体沟通会,介绍了赛灵思在数据中心领域的相关创新和现状。

前段时间看到Xilinx发布了新的差异化ZYNQ Ultrascale+ MPSoC ZU1和Artix Ultrascale+FPGA,熊猫君趁着国家假日有点时间,随便瞎聊一下。本次发布的新产品均采用16nm的工艺,可选封装有0.5mm焊盘间距紧凑型的InFo,最小封装尺寸只有15mm*9.5mm,这种封装类型可以缩短信号互联,有利于提高信号完整性

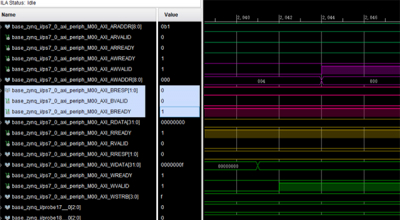

AXI4、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手机制进行通信。信息传输的发起者使用Valid 信号指示数据何时有效,接收端产生 Ready 信号来表明已经准备好接收数据,当两者均为高时,启动传输。

Xilinx 基于 CNN 网络的 ICMS 演示

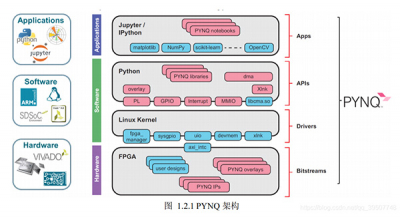

PYNQ 是 Xilinx 推出的一个开源项目,目的是使用 Python 开发 Xilinx 平台更加容易。使用 Python 语言和库,设计人员可以利用 Xilinx SOC 器件如 ZYNQ 的可编程逻辑 PL 和微处理器 PS 的优势来构建功能更强大的电子系统。

本文介绍了一种基于VPX架构的高速宽带数据通信平台,平台的核心是机载和地面收发信机,收发信机内各功能板卡的主要控制器是FPGA。发射端对信息序列进行打包、信道编码、交织和调制;接收端对信号进行解调、解交织、解码、同步等操作。还原后的信息上传至上位机进行分析。