# Zynq-7000 Platform Software Development Using the ARM® DS-5 Toolchain

Author: Simon George and Prushothaman Palanichamy

#### **Summary**

This document provides guidance on using the ARM Development Studio 5 (DS-5) design suite for the development, build, and debug of bare metal software for the Xilinx Zynq-7000 All Programmable SoC, which is based on the ARM Cortex<sup>™</sup>-A9 processor. This process is described in the following steps:

- 1. Xilinx SDK: Board Support Package (BSP) creation for custom hardware design

- 2. DS-5 tools: BSP import and build

- 3. DS-5 tools: Application build

- 4. Xilinx SDK and DS-5 tools: Zynq device FSBL Changes for ARMCC build

- 5. DS-5 tools: Debugger target configuration for Zynq device custom design

#### Introduction

This document assumes that you have a basic understanding of the architecture, boot flow, and associated Xilinx design tools for the Zynq-7000 product family as well as a basic understanding of the ARM DS-5 toolchain. It also assumes that the development host operating system is Windows. To complete the procedure in this application note, you must have installed the following host-based software tools:

- Xilinx Software Development Kit (SDK) 2013.3, which you can download at this link.

- ARM Development Studio 5 (DS-5) tool suite, which you can download at this <u>link</u>.

Note: A 30-day evaluation is available for the DS-5 tool suite.

Currently Xilinx only supports the ARM commercial C and C++ compiler, not the Linaro GCC that is also distributed with the DS-5 tool suite.

#### **Associated Design Files**

You need to customize the 2013.3 Standalone Board Support Package and First Stage Boot Loader (FSBL) template distributed by Xilinx. The design files for this application note (available at this <u>link</u>) provide these customizations as well as updated repositories. The design files also include a target initialization file and linker script example for use in the DS-5 tools, as described by this document. The Standalone BSP included in the design files is similar to the standalone\_v3\_11\_a available from 2013.3 with a few changes to inline assembly functions.

Download and unzip the design files. Note the directory name and location where you save the files.

# Tools Configuration

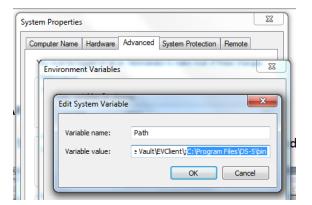

The procedure in this application note requires that you use the ARM compiler toolchain from within the Xilinx SDK environment, which necessitates that the corresponding ARM executables need to be visible outside of the DS-5 tool environment and its command prompt. To achieve this visibility, you need to modify the Windows system environment variables as shown in Figure 1.

© Copyright 2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners.

Ensure that the appended path (shown highlighted in the illustration) matches your actual install location.

Figure 1: Edit Windows System Environment Variable

Step 1 - Xilinx SDK: Standalone Board Support Package Creation

Xilinx SDK dynamically assembles a customized BSP based on the selected hardware design, whether that is a customized design imported from Vivado® design suite or a preconfigured platform. This assembled BSP includes a collection of CPU complex-specific configuration and startup code along with platform address and configuration information for both hardened processing system and soft, programmable logic peripherals, which is effectively everything needed to link against when creating an application project.

You complete the physical process of creating this data-driven BSP through a Library Generator (libgen) utility, which is an integral part of the Xilinx SDK environment. Therefore, development in the ARM DS-5 tools must also baseline from this BSP. However, there is GCC-specific assembler code included in the default start-up files, which therefore require customization. Part of this process is automated. The design files included with this application note patch the files for this release.

Use the following steps to build the patched Standalone BSP repository from Xilinx SDK.

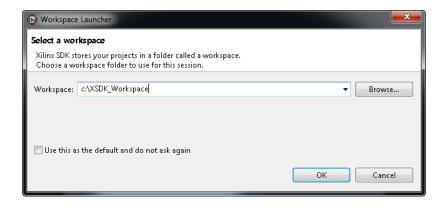

- 1. Invoke Xilinx SDK, then create and configure the workspace.

- a. Open Xilinx SDK and create a new workspace (suggested name: XSDK\_Workspace).

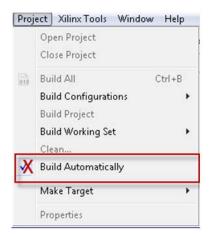

b. In Xilinx SDK, click **Project** and disable the **Build Automatically** option. This setting allows you to change the compiler option before building a project.

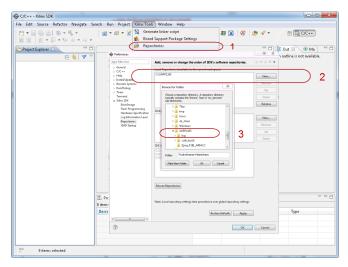

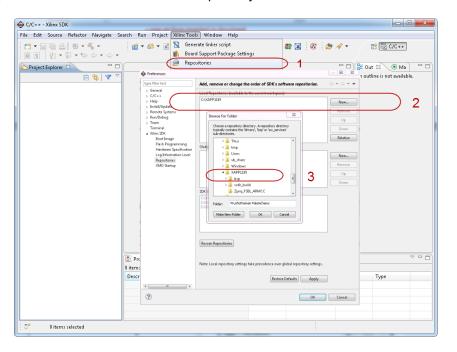

c. Click Xilinx Tools > Repositories and click New on the Local Repositories box. Browse to the XAPP1185 folder in the application note design files and add the patched Standalone BSP as new repository.

2. Create a new Standalone application project and Standalone BSP (ARMCC version).

XSDK provides a New Project creation wizard, which guides you through the process of creating a new project in a coordinated way. This wizard is used in the following illustrations. Project settings may deviate from what is shown based on individual needs.

This application note uses the Hello World application example created in Xilinx SDK as the first 'C' application to run on the target built through the DS-5 tools. If you do not need to create a sample application project, you can either individually create a BSP against a previously imported hardware platform or manually create a hardware platform and then create a BSP against it.

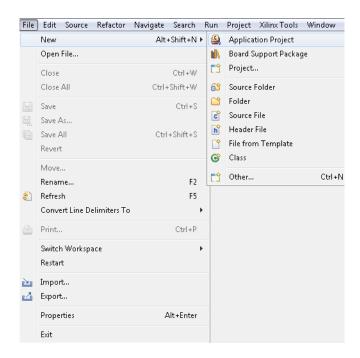

a. In Xilinx SDK, click File > New > Application Project.

- b. In the Application Project screen make the following settings.

- Hardware Platform

Select either predefined or custom (Create New) in the pull-down menu. If you select **Create New**, SDK prompts you to navigate to the location of the <HardwareDesign.xml> provided by your hardware development team, a directory that also includes ps7\_init .c/.h and .tcl.

Software Platform

Target Software: Board Support Package. The suggested name for the Board Support Package is BSP\_Standalone\_ARMCC, as shown in the following illustration. (Xilinx SDK uses the Xilinx-distributed GCC to build the BSP source by default, but you modify the toolchain options later in this procedure.)

- Click Next.

- Set the application template.

You can use any of the application templates to validate the build flow before undertaking your application. This application note uses the "Hello World" application.

• Click Finish.

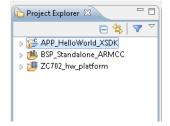

The tools create the files shown in the following illustration:

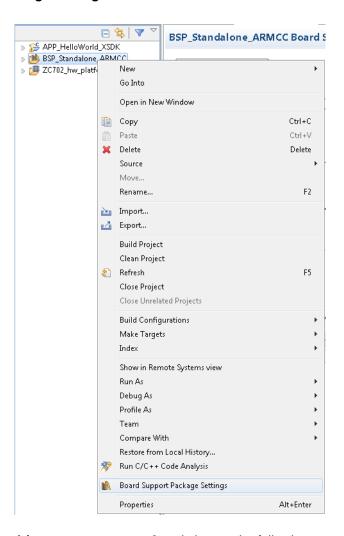

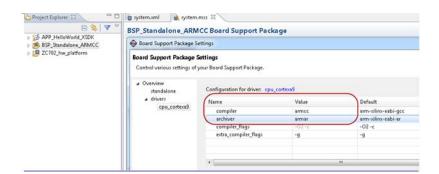

Right-click the BSP project, BSP\_Standalone\_ARMCC, and then select Board Support Package Settings.

d. Navigate to **drivers** > **cpu\_cortexa9** and change the following parameters.

compiler: armccarchiver: armar

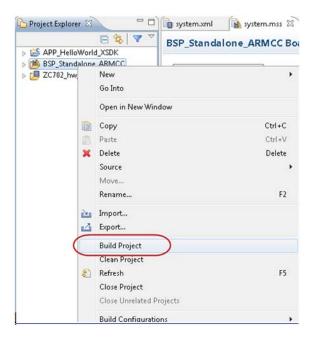

e. Right-click the BSP project and select Build Project.

f. The patched BSP source repository is now built against the ZC702\_hw\_platform (pre-defined using the ARMCC toolchains).

**Note:** You don't need to set additional compiler options. You could use the archived library. However, in the next steps you will import the customized BSP source tree into the DS-5 tools where many options are exposed as build options.

## Step 2 - DS-5 Tools: BSP Import and Build

1. Invoke **Eclipse for DS-5** to create a new workspace. The example in this document creates a new workspace in C: \DS5\_Workspace.

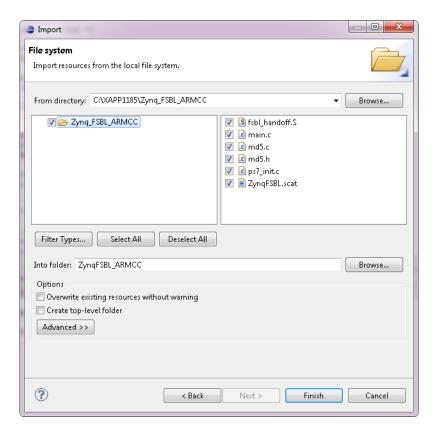

- 2. Import the Standalone BSP

- a. In the DS-5 tool, click File > New > C Project > Bare metal Library > Empty Project.

b. Name the project (suggested name: "ZynqBSP"). Click Next.

- c. Click Finish.

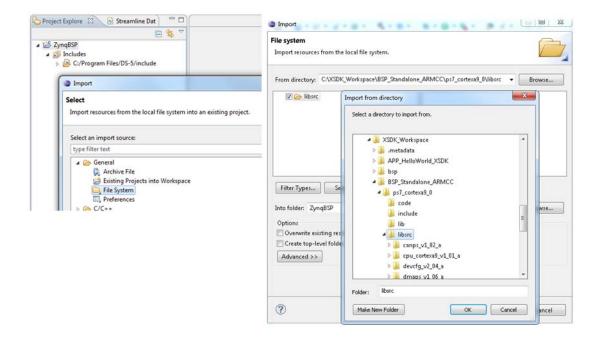

- d. Right-click the Library project and import the Xilinx-SDK-generated (ARMCC) BSP source tree, specifically the directory tree below "libsrc." Browse to the folder BSP\_Standalone\_ARMCC\ps7\_cortexa9\_0\libsrc, then click **OK**.

e. In the Import window, Click Finish.

**Note:** By using links to the original sources, reference file updates will propagate into the DS-5 tools.

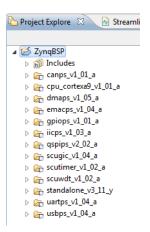

f. The folders shown in the following illustration are now included in the ZynqBSP project.

- 3. Change the build settings to suit the Zynq architecture.

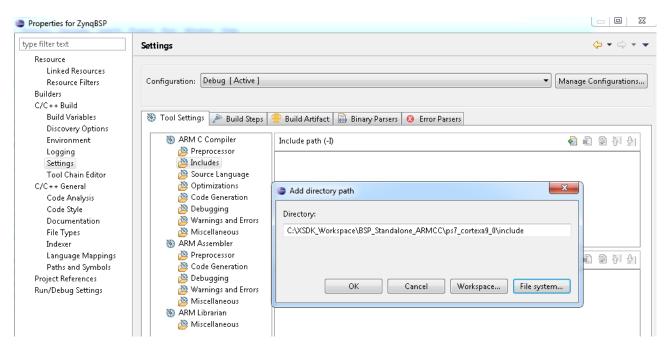

- a. Right-click on the project (**ZynqBSP**), then click **Properties**.

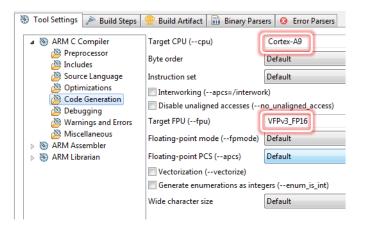

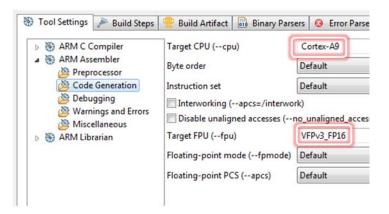

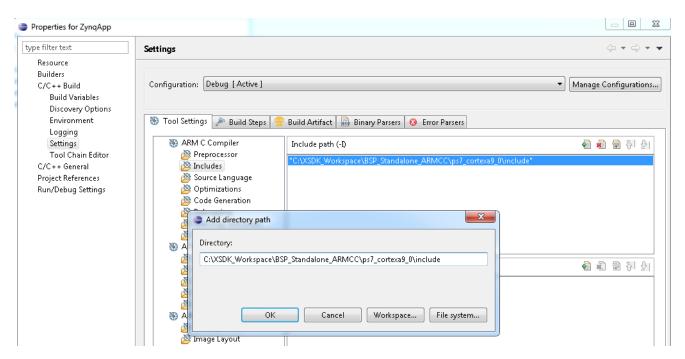

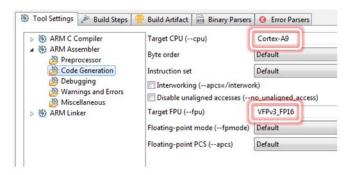

- b. In the Properties wizard, navigate to **C/C++ Build > Settings**, then modify the following settings of the ARM Compiler and ARM Assembler.

- In the ARM C Compiler, set the include paths for the referenced header files generated by the Xilinx SDK libgen process, customized to the hardware configuration:

- -I <XSDK\_workspace>\BSP\_Standalone\_ARMCC\ps7\_cortexa9\_[0]\include

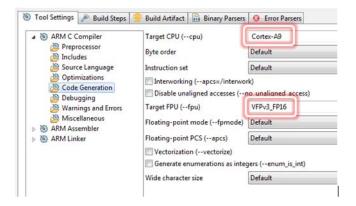

- In the ARM C Compiler, set the Code Generation parameters specific to the Zynq device:

- --cpu Cortex-A9

- --fpu VFPv3 FP16

- In the ARM Assembler, set the Code Generation parameters specific to the Zynq device:

- --cpu Cortex-A9

- --fpu VFPv3\_FP16

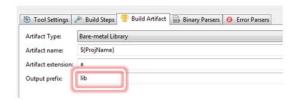

- c. Click the **Build Artifacts** tab and make the following settings:

- Artifact extension: a

- Output Prefix: lib

```

'Finished building target: libZynqBSP.a'

' '

**** Build Finished ****

```

You have now completed this step.

## Step 3 - DS-5 Tools: Application Build

Use this procedure to create a DS-5 application project for the Zynq device.

- 1. Import and create a software application:

- a. In the DS-5 tool, click File > New > C Project > Bare metal Executable > Empty Project.

b. Name the Project (suggested name: "ZynqAPP").

c. Click Next.

- d. Click **Finish** to close the C Project wizard.

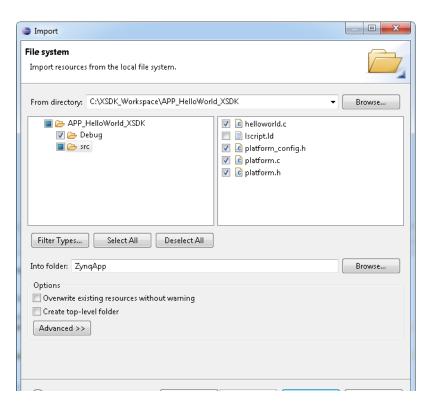

- e. Right-click the application project, select **Import**, and navigate to the "Hello World" application project (App\_HelloWorld\_XSDK) created in Step 1 of this application note.

f. Include all the C Source and Header files (\*.c, \*.h, \*.S).

- 2. Change the build settings to suit the Zynq architecture.

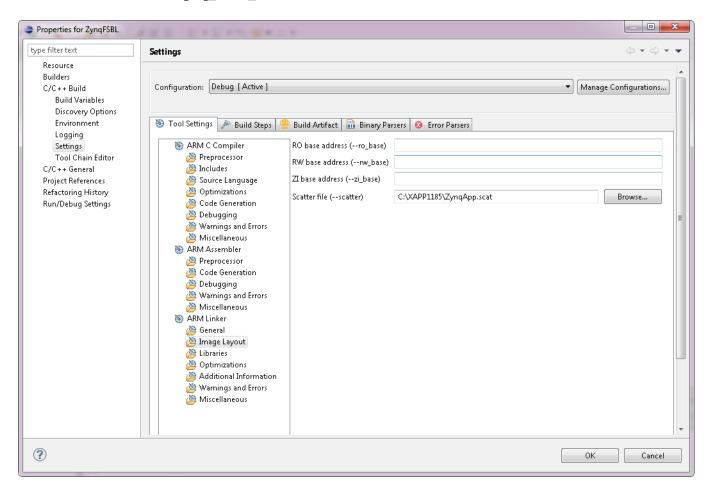

- a. Right-click the project (ZynqApp) and select **Properties**. In the Properties wizard, navigate to **C/C++ Build > Settings** and modify the following settings of the ARM Compiler, ARM Assembler, and ARM Linker:

In the ARM C Compiler, set the Include paths for referenced header files generated by the Xilinx SDK libgen process, customized to the hardware configuration:

../.../XSDK\_Workspace/BSP\_Standalone\_ARMCC/ps7\_cortexa9\_0/include

- b. In the ARM C Compiler, set the Code Generation parameters specific to Zynq architecture:

- --cpu Cortex-A9

- --fpu VFPv3 FP16

- c. In the ARM Assembler, set the Code Generation parameters specific to Zynq architecture:

- --cpu Cortex-A9

- --fpu VFPv3\_FP16

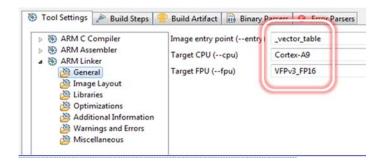

- d. In the ARM Linker, set the General parameters specific to Zynq architecture:

- --entry vector\_table

- --cpu Cortex-A9

- --fpu VFPv3\_FP16

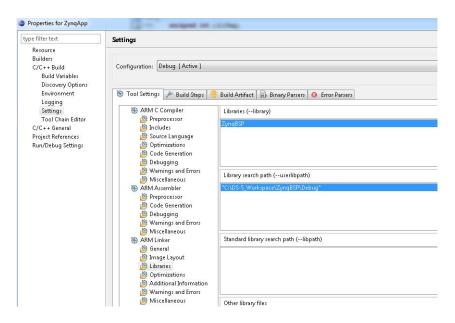

- e. In the ARM Linker > Libraries, add the reference BSP build created in Step 2 of this application note:

- Libraries (--library): ZyngBSP

- Library Search Path (--userlibpath): \${workspace\_loc:/ZyngBSP/Debug}

**Note:** The entry point matches the start of memory against which the program is linked in the scatter file. The definition of "\_vector\_table" can be found in asm\_vector.s, which resides in the "standalone" code of the BSP source tree.

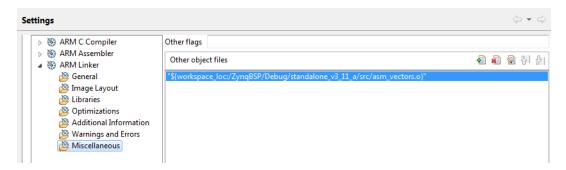

- f. In the ARM Linker, select **Miscellaneous > Other objects files**.

- g. In the Other object files tab, Click the Add button and navigate to \$workspace\_loc:\ZynqBSP\Debug\ps7\_cortexa9\_0\libsrc\stand alone\_v3\_11\_a\src" and select asm\_vectors.o file

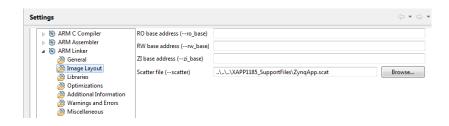

In the ARM Linker, select Image Layout and define the Linker Script, referred to here as a scatter file.

i. A Sample ZynqApp.scat file Image Layout is shown in the figure below. This file can be found in the XAPP1185 reference files.

```

4

50 DDR_LOAD 0x100000 {

60 DDR_TEXT 0x100000

7 {

8 asm_vectors.o (.vectors, +First)

9 * (+RO, +RW, +ZI)

10 }

11 ARM_LIB_HEAP +0 ALIGN 0x08 EMPTY 0x2000 {}

12 ARM_LIB_STACK +0 ALIGN 0x10 EMPTY 0x2000 {}

13 IRQ_STACK +0 ALIGN 0x10 EMPTY 0x1000 {}

14 SPV_STACK +0 ALIGN 0x10 EMPTY 0x2000 {}

15 ABORT_STACK +0 ALIGN 0x10 EMPTY 0x2000 {}

16 }

```

j. Compile the application. As a reference, the following illustration shows the compiled size in the example flow.

You have now completed this step.

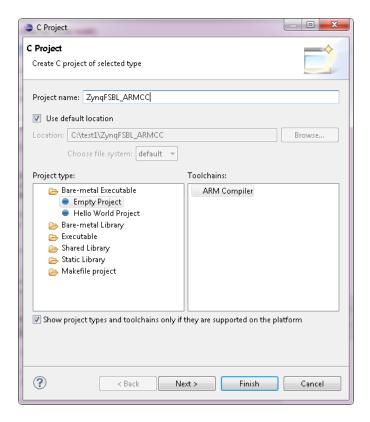

Step 4 - Xilinx SDK and DS-5 Tools: Zynq Device FSBL Changes for ARMCC Build

Use the following steps to build the First Stage Boot Loader (FSBL) with ARMCC.

- 1. Open Xilinx SDK, and use the existing workspace, "XSDK\_Workspace."

- 2. Click File > New Application Project.

Name the project (suggested name: "ZynqFSBL\_XSDK"). Use the existing BSP (BSP\_Standalone\_ARMCC).

4. Choose **Zynq\_FSBL** as the application template.

- 5. Click Finish.

- 6. Open Eclipse for DS-5.

- 7. Use the existing workspace, "DS5\_Workspace."

- 8. Create a **Bare-metal Executable** > **Empty** application project named "ZynqFSBL." For more information, see the procedure in Step 3 DS-5 Tools: Application Build.

9. Click Finish.

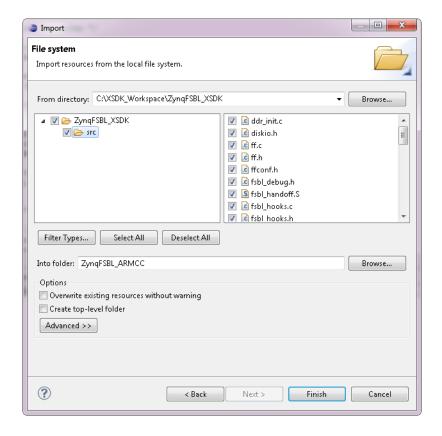

10. Import the files from "ZynqFSBL\_XSDK" into this project.

11. Import the patched FSBL files from the support files location, specifically the files located in the <code>Zynq\_FSBL\_ARMCC</code> subfolder.

12. Set the Compiler and Linker options as described in Step 3 - DS-5 Tools: Application Build.

13. Set the image layout file to ZynqFSBL.scat. This file is located at ..\XAPP1185\Zynq\_FSBL\_ARMCC.

14. Build the project "ZyngFSBL\_ARMCC."

The following illustration shows a sample, post-build log for reference.

```

______

Code (inc. data)

RO Data

RW Data

ZI Data

Debug

72082

17986

11248

38620

124417

Grand Totals

72082

17986

1796

ELF Image Totals (compressed)

38620

124417

72082

17986

1796

ROM Totals

______

Total RO Size (Code + RO Data)

72532

70.83kB)

Total RW Size (RW Data + ZI Data)

Total ROM Size (Code + RO Data + RW Data)

49868 (

48.70kB)

74328

72.59kB)

'Finished building target: ZynqFSBL.axf'

**** Build Finished ****

```

You have now completed this step.

**Note:** The ps7\_init.c file provide in ..\XAPP1185\ Zynq\_FSBL\_ARMCC works only for ZC702\_hw\_platform. For other hardware platforms, you must manually edit this file to compile with ARMCC.

# Step 5 - DS-5 Tools: Debugger Target Configuration for Zynq Device Custom Design

You can use the FSBL application created in Step 4 to initialize the target hardware. The following init script shows an example of using the  ${\tt ZynqFSBL.axf}$  to initialize the target.

```

zynq_init.ds

loadfile {Workspace_loc:}\Zynq_FSBL_ARMCC\Debug\ZynqFSBL.axf

run

pause 1000

stop

```

Use the following steps to initialize the target hardware for a debug session:

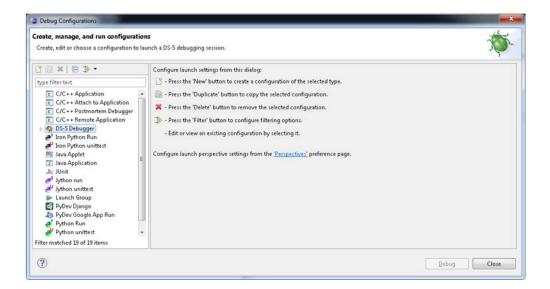

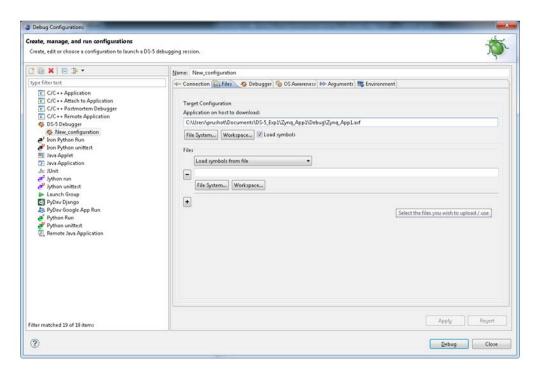

- 1. Right-click on the application that you want to debug and select **Debug Configurations**.

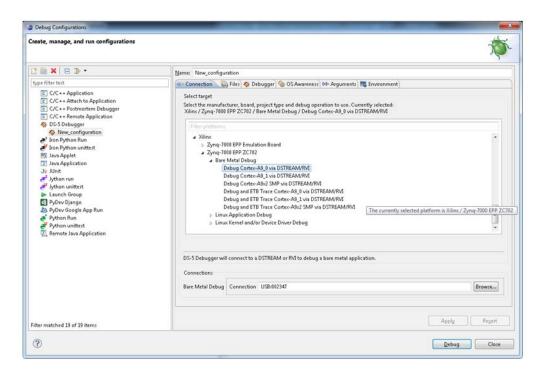

- In the Debug Configurations window, double-click on DS-5 Debugger to create a new Debug Configuration.

On the Connection tab, find "Zynq-7000 EPP ZC702" and select Bare Metal Debug > Debug Cortex-A9 via DStream/RVI.

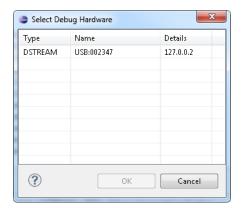

4. In the Connections area at the bottom of the dialog box, click the **Browse** button to the right of the Bare Metal Debug, Connection field. The application auto-detects the Dstream connection to the host machine. Select the appropriate connection (USB in this example), then click **OK**.

5. On the Files tab, select the application that you need to debug (for example, zynq\_app.axf).

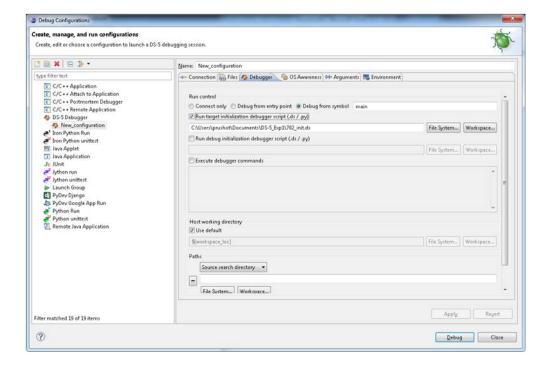

6. On the Debugger tab, select the **Run target initialization debugger script (.ds/.py)** checkbox and select the <code>zynq\_init.ds script</code> (example provided above).

- 7. Make sure the DStream cable is connected to the board. Power on DStream and the target.

- 8. Click the **Debug** button.

**Note:** The debugger loads FSBL in OCM and runs it. The FSBL then initializes the target hardware. The debugger waits one second for FSBL to complete initialization of the target and stops the target to load the application with a breakpoint at main().

```

702_init.ds

le helloworld.c 🔀

17 */

19/*

20 * helloworld.c: simple test application

21 * This application configures UART 16550 to baud rate 9600.

23 * PS7 UART (Zyng) is not initialized by this application, since

24 * bootrom/bsp configures it to baud rate 115200

27 * | UART TYPE BAUD RATE

29 *

uartns550 9600

Configurable only in HW design

31

ps7_uart

115200 (configured by bootrom/bsp)

34#include <stdio.h>

35 #include "platform.h"

37 void print(char *str);

init_platform();

print("Hello World\n\r");

return 0:

```

This concludes the steps necessary to set up a debug session. For successive debug sessions, click the **Debug** button.

## Automating Step 1 Using Scripts

Advanced users can automate Step 1 of this application note with the included script files. The batch file to automate step 1, build\_bsp\_fsbl\_app.bat, is located at ..\XAPP1185\xsdk\_build\build\_bsp\_fsbl\_app.bat.

The location of the system.xml file has to be passed as an argument to run this batch file, as shown in the following example, which generates the ARMCC version of BSP and FSBL for the ZC702 board. The command assumes the design files XAPP1185.zip is unzipped to C:\.

```

C:\XAPP1185\xsdk_build>build_bsp_fsbl_app.bat ZC702_hw_platform

```

This command takes the <code>system.xml</code> file from ZC702\_hw\_platfrom, which is available as part of this document. The batch file produces three folders:  $Zynq_FSBL$ ,  $ps7_cortex_a9$ , and the  $hello_world$  project folder. You can import these files directly into the ARM DS-5 project as described in Step 2 - DS-5 Tools: BSP Import and Build.

#### References

- Zynq-7000 All Programmable SoC: Concepts, Tools, and Techniques (UG873)

- 2. Xilinx video tutorial, "Zyng Bare Metal Application Development using Xilinx SDK"

- 3. Xilinx video tutorial, "Heterogeneous Multicore Debugging with Xilinx SDK"

# Revision History

The following table shows the revision history for this document.

| Date     | Version | Description of Revisions |

|----------|---------|--------------------------|

| 11/18/13 | 1.0     | Initial Xilinx release.  |

### Notice of Disclaimer

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: http://www.xilinx.com/warranty.htm#critapps.