作者:电子创新网编辑部

2025年8月6日——PCI-SIG协会今日宣布,正在开发的PCI Express® (PCIe®) 8.0规范将把数据速率提升至256.0 GT/s,相较PCIe 7.0再度实现翻倍,并计划于2028年向会员发布。通过x16通道配置,PCIe 8.0的双向带宽将达到1 TB/s,为高带宽计算场景带来前所未有的性能空间。

PCIe 8.0的设计目标

根据PCI-SIG的说明,PCIe 8.0规范在性能提升的同时,将继续保持向后兼容性并满足低延迟、可靠性和功耗优化的设计目标。关键特性包括:

l 256.0 GT/s原始比特率,x16配置实现1 TB/s双向传输速率

l 引入新的连接器技术,满足更高信号完整性需求

l 优化延迟与FEC(前向纠错)机制,确保可靠性

l 增强协议功能以提升有效带宽利用率

l 持续降低功耗,满足绿色数据中心与移动计算需求

满足新兴计算的带宽挑战

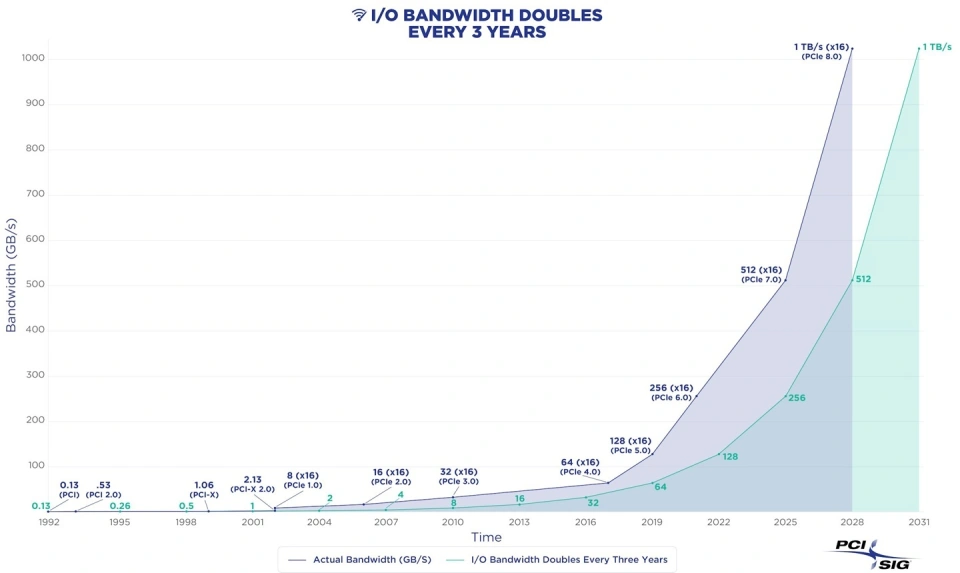

过去二十余年,PCIe已成为业界高带宽互连的事实标准。从1.0的2.5 GT/s到7.0的128 GT/s,再到8.0的256 GT/s,PCIe几乎每一代都将速率翻倍。这一趋势的背后,是计算需求的持续爆发:

l AI/ML训练与推理:大模型训练已突破数千亿参数规模,GPU、AI加速卡和存储系统的互连需求激增。

l 高速网络与边缘计算:低延迟传输和海量数据处理要求更高的I/O带宽支持。

l 量子计算与HPC:需要高吞吐、低延迟的系统级互连架构。

l 汽车与国防领域:自动驾驶和航空电子对实时性和可靠性的要求使高速总线标准成为关键组件。

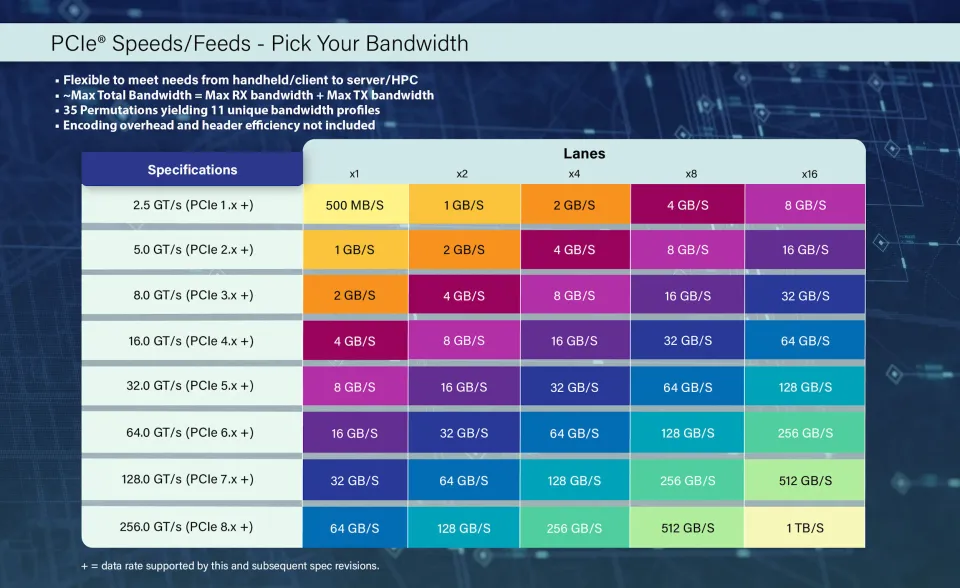

PCIe1.0~8.0的带宽对比表格

I/O速率演进趋势与未来展望

根据PCI-SIG公布的速率发展趋势图,PCIe标准平均每三到四年完成一次速度翻倍迭代。在7.0到8.0的跃迁中,通道信号质量、走线设计和封装材料都将面临新的挑战。

未来,PCIe 8.0可能推动以下技术发展方向:

1. 先进封装与芯片间互连:协同设计将成为高性能计算平台的核心竞争力。

2. 光互连技术:在更高传输速率下,电信号完整性受限,光互连或将在PCIe 9.0甚至更早的扩展中引入。

3. 系统功耗优化:数据中心对能效的严苛要求将促使PCIe协议持续迭代低功耗特性。

对FPGA生态的影响

PCIe 一直是 FPGA 与外部系统通信的核心接口之一,广泛用于加速卡、网络处理、数据采集、AI推理等领域。PCIe 8.0 的到来将对 FPGA 产业带来多方面影响:

1. 硬件接口设计升级:256 GT/s 的速率需要更先进的收发器架构(PAM4、均衡技术)和高性能封装设计。

2. 加速卡设计空间扩大:x16 1 TB/s 的带宽极大缓解了 FPGA 与 CPU/GPU 之间的数据瓶颈。

3. 系统级互连与Chiplet趋势:8.0将促进异构封装和短距互连方案的发展。

4. IP与生态竞争:支持 PCIe 8.0 的FPGA IP核和工具链将成为高性能加速市场的准入门槛。

总结来看,PCIe 8.0 既是技术挑战,也是FPGA加速卡向更高性能、更广应用领域渗透的重要机遇。

* 本文为原创文章,转载需注明作者、出处及原文链接,否则,本网站将保留追究其法律责任的权利