HDL Verifier 通过 UVM 支持加快 FPGA/ASIC 验证速度

judy 在 周四, 03/12/2020 - 09:47 提交

HDL Verifier 能够让开发 FPGA 和 ASIC 设计的设计验证工程师直接从 Simulink 模型生成 UVM 组件和测试平台,并在支持 UVM 的仿真器(比如来自 Synopsys、Cadence 和 Mentor 的仿真器)中使用这些组件和测试平台

HDL Verifier 能够让开发 FPGA 和 ASIC 设计的设计验证工程师直接从 Simulink 模型生成 UVM 组件和测试平台,并在支持 UVM 的仿真器(比如来自 Synopsys、Cadence 和 Mentor 的仿真器)中使用这些组件和测试平台

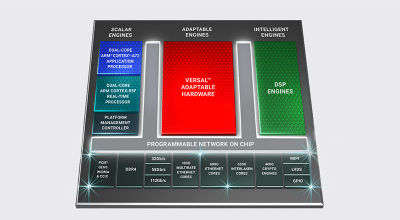

今天上午,FPGA发领头羊赛灵思公司以在线发布形式宣布推出 Versal ACAP 产品组合第三大产品系列—— Versal™ Premium,这款FPGA堪称是史上最强大FPGA,它有高度集成且功耗优化的网络硬核,是业界带宽最高、计算密度最高的自适应平台

赛灵思今天宣布推出 Versal ACAP 产品组合第三大产品系列—— Versal™ Premium。Versal Premium 系列具备高度集成且功耗优化的网络硬核,是业界带宽最高、计算密度最高的自适应平台。Versal Premium 专为在散热条件和空间受限的环境下运行最高带宽网络,以及那些需要可扩展、灵活应变应用加速的云提供商而设计

实现了技术方面的突破,那么要如何与生产环境集成呢?如何在实际的业务体系中实现对FPGA优势更好的应用?实际部署是其中最值得探讨与研究的方向。对此,深维科技进行了一系列的探索与尝试,形成了以下几种方案

EdgeBoard是基于FPGA打造的嵌入式AI解决方案,能够提供强大的算力,并支持定制化模型,适配各种不同的场景,并大幅提高设备的AI推理能力,具有高性能、高通用、易集成等特点

我很有幸从第一届亚太地区设计自动化会议(ASP-DAC)起就参与到ASP-DAC这个大家庭。我的第一篇ASP-DAC论文是1995年在日本千叶的首届会议发表的”Exploiting Signal Flow and Logic Dependency in Standard Cell Placement”[3]。这篇文章讨论了如何利用逻辑综合的信息来提高标准单元布局的结果

今天,赛灵思宣布推出业界首款 “一体化 SmartNIC 平台”— Alveo™ U25,在业界首次真正在单卡上实现了网络、存储和计算加速功能的完美融合。U25 专门针对当前那些在不断增长的联网需求和不断上涨的成本之中苦苦挣扎的云服务提供商、电信公司和私有云数据中心运营商而设计

每年二月,阿姆斯特丹都会举办世界上规模最大的音视频与系统集成展会 - 欧洲集成系统展(ISE)。在这里,全球音视频行业齐聚一堂,共同分享业界领先的音视频项目以及尖端技术、产品与解决方案。AI/ML 相关的话题依然是各个行业的焦点所在,人工智能领域日益扮演领导角色的赛灵思,在 ISE2020 上有什么亮点和表现呢?

2 月中旬,国产手机品牌小米发布新款旗舰小米 10 系列,其主打卖点之一便是支持一亿像素 8K AI 视频拍摄。而在此之前率先面世的三星 Galaxy S20,更可以原生拍摄 8K 视频。从体型庞大的摄像机到如今一手可握的智能手机,技术的日益革新推动设备不断变化衍进,但 8K 却从未改变。

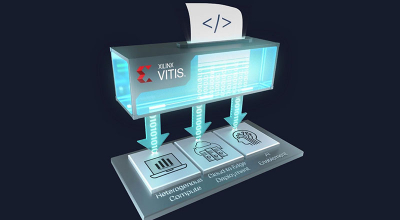

Vitis 平台将19.1之前的SDK、SDSoC、SDAccel整合在一起的基础上,加入了Vitis AI开发环境。让软件工程师也能够基于Vitis平台完成Xilinx器件的项目设计。然而对于习惯了传统的开发方式的工程师来说,最基本的嵌入式开发都要转移到Vitis上进行。本次我们就来看看从基础的SDK到Vitis有多少异同