什么是64b/66b 编码技术?

64b/66b编码技术是IEEE 802.3 工作组为10G 以太网提出的,目的是减少编码开销,降低硬件的复杂性,并作为8b/10b编码的另一种选择,以支持新的程序和数据。当前,64b/66b编码主要应用于Fiber Channel 10GFC和16GFC、10G 以太网、100G 以太网、10G EPON、InfiniBand、Thunderbolt 和 Xilinx 的 Aurora 协议。

64b/66b 编码基础知识

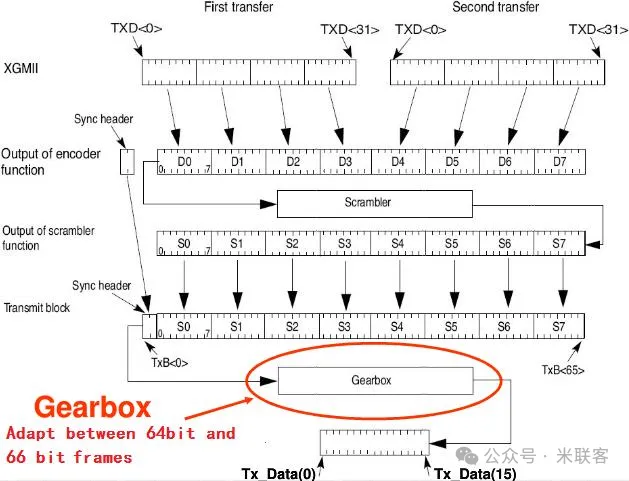

64b/66b 编码将 64bit 数据或控制信息编码成 66bit 块传输,66bit 块的前两位表示同步头,主要由于接收端的数据对齐和接收数据位流的同步。同步头有“01”和“10”两种,“01“表示后面的 64bit 都是数据,“10”表示后面的 64bit 是数据和控制信息的混合,其中紧挨着同步头的 8b 是类型域,后面的 56bit 是控制信息或者数据或者两者的混合。64b/66b 编码格式图如下图所示,其中 D 表示数据编码,每个数据码 8bit;Z 表示控制码,每个控制码7bit;S 表示包的开始,T 表示包的结束。S 只会出现在 8 字节中的第 0 和第 4 字节,T 能够出现在任意的字节。除同步码外,64bit 的数据必须经过扰码以后才能进行传输。10G 以太网的 64b/66b 编码所使用的扰码器为 X58+X39+1。

注:此外还有 Block Type 为 0x2d,0x66,0x55,0x4b 等情况没有列出。不同的协议的格式可能不尽相同,具体应以协议的 Spec 为准。

64b/66b 编码过程如下图所示:

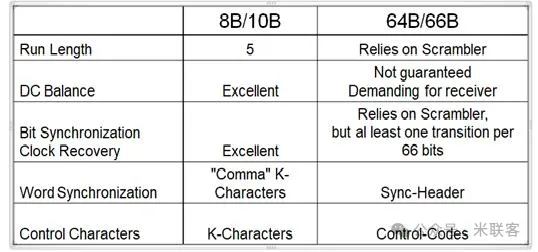

64b/66b 与 8b/10b 的简单比较如下图所示:

需要注意的是,64b/66b 编码没有办法限制 Run Length(即数据流中的连续的 0 或者连续的 1 长度)到一个比较小的值,只能通过选择合适的多项式来取得相对最优的 DC Balance 和相对较低的较大值得 Run Length 的概率。显然,采用 64b/66b 编码,对串行收发器的 CDR 提出了非常高的要求。

Xilinx Aurora 协议

TX 同步齿轮箱位和字节排序

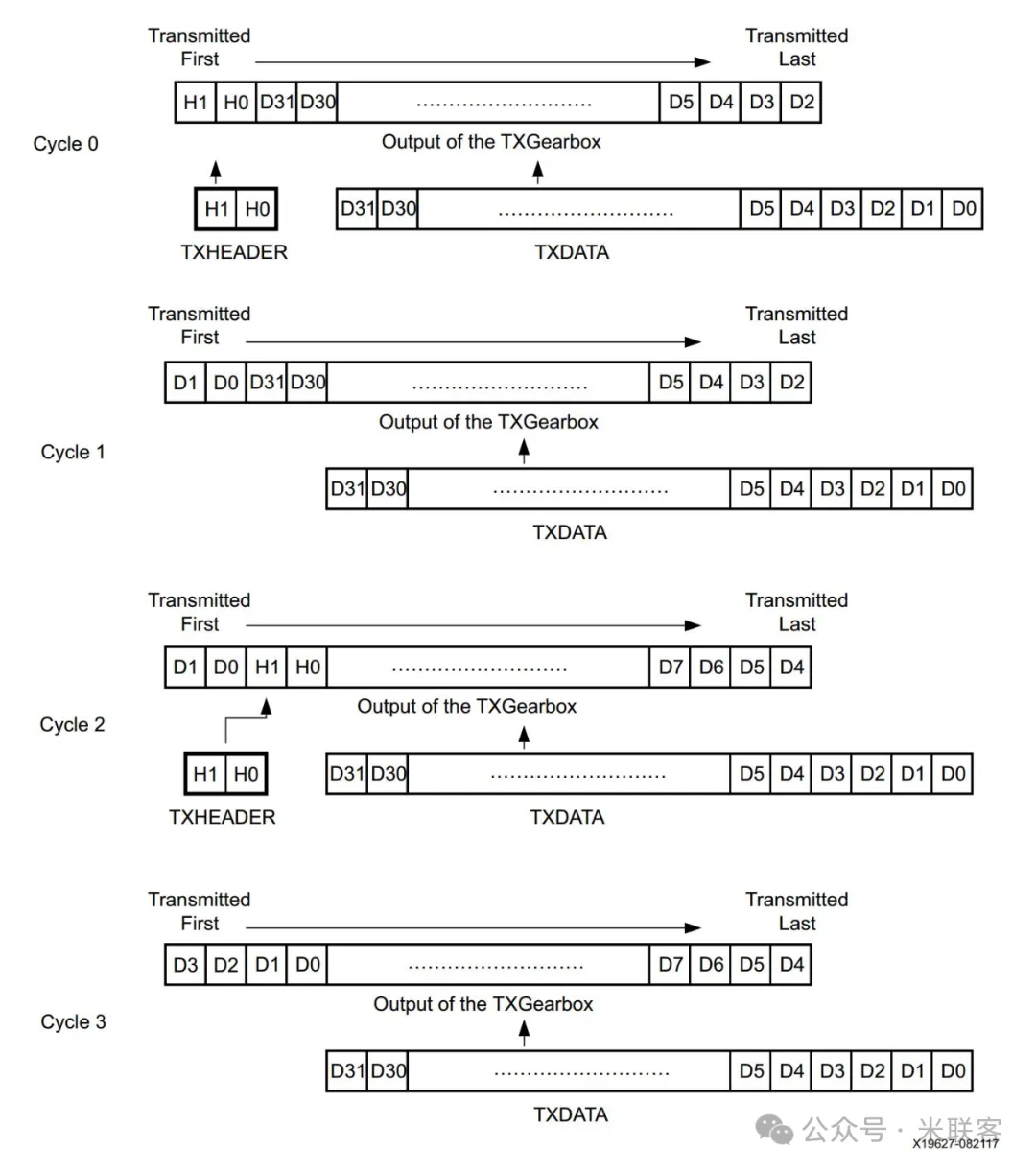

下图显示了使用 4 字节逻辑接口(TX_DATA_WIDTH=32(4 字节)、TX_INT_DATAWIDTH=1(4 字节)时,用于64B/66B 编码的数据进入和退出 TX 齿轮箱的前四个周期的示例))在正常模式下(GEARBOX_MODE[2]=1'b0)。输入由 2 位标头和 32 位数据组成。

在第一个周期,标头和 30 位数据退出 TX 变速箱。在第二个周期,来自前一个周期的 TXDATA 输入的剩余两个数据位以及来自当前 TXDATA 输入的 30 个数据位退出 TX 齿轮箱。在第三个周期,TX 变速箱的输出包含来自第一个 66 位块的两个剩余数据位、第二个 66 位块的标头以及来自第二个 66 位块的 28 个数据位。

TX 同步齿轮箱位

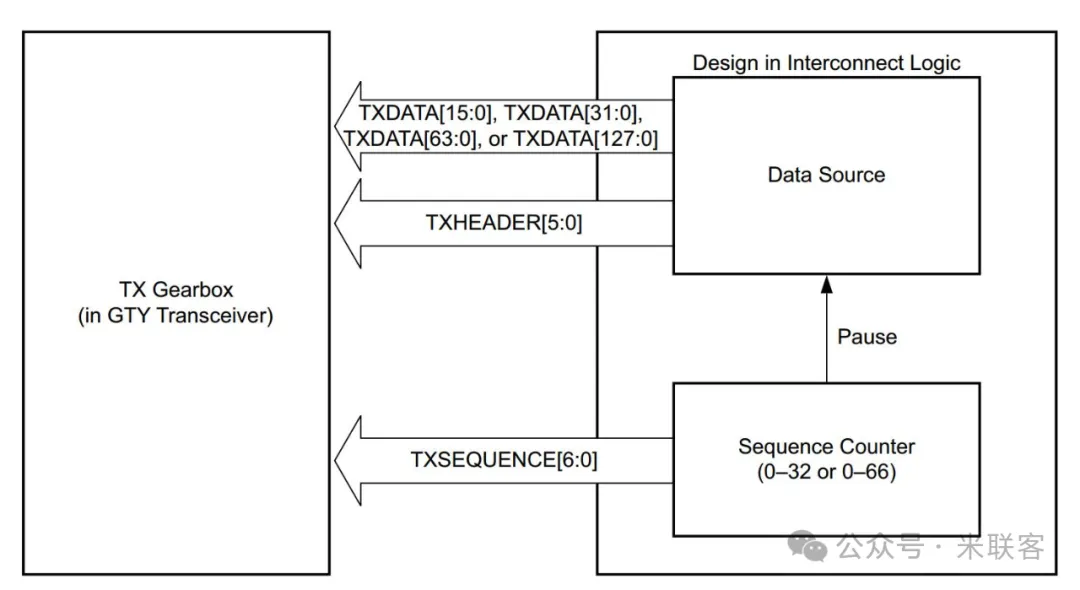

TX 同步齿轮箱需要使用必须在互连逻辑中实现的外部序列计数器。TX 变速箱支持互连逻辑的 2 字节、4 字节、8 字节和 16 字节接口。

如图所示,在正常模式下(GEARBOX_MODE[2]=1),外部序列计数器操作模式使用 TXSEQUENCE[6:0]、TXDATA[127:0] 和 TXHEADER[5:0] 输 入 。当 使 用 CAUI 接 口 时 (GEARBOX_MODE[2]=1'b1) ,也会使用TXHEADER[5:3]。用户逻辑中必须存在二进制计数器才能驱动 TXSEQUENCE 端口。对于 64B/66B 编码,计数器从 0 递增到 32,并从 0 重复。对于 64B/67B 编码,计数器从 0 递增到 66,并从 0 重复。

使用64B/66B 编码时,将TXSQUENCE[6]连接至逻辑0,并将未使用的 TXHEADER 位连接至逻辑0。当使用CAUI 接口并选择64B/66B编码 (GEARBOX_MODE) 时,TXHEADER[5]必须连接至逻辑0[2]=1'b1,GEARBOX_MODE[0]=1'b1)。

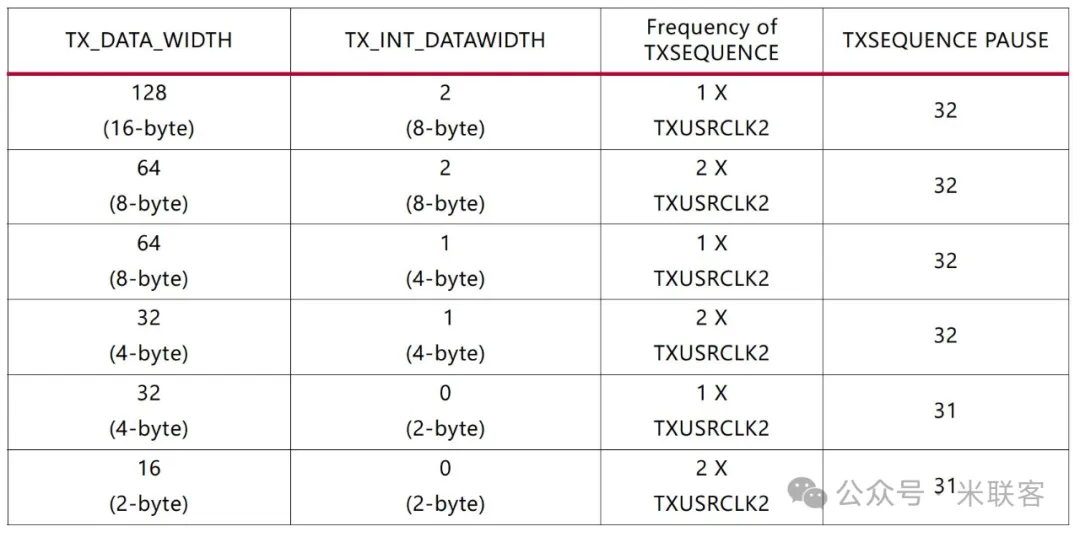

对于2字节、4字节、8字节和 16字节接口,序列计数器增量范围({0到32}、{0到66})相同。然而,当使用TX_DATA_WIDTH 与 TX_INT_DATAWIDTH 相同的模式时,计数器必须每两个 TXUSRCLK2 周期递增一次(例如,4 字节互连逻辑接口(TX_DATA_WIDTH=32)和 4 字节内部数据宽度(TX_INT_DATAWIDTH=1))。

由于 64B/66B 和 64B/67B 编码方案以及 TX 同步变速箱的性质,用户数据在各种序列计数器值期间被保留(暂停)。在 TX_DATA_WIDTH 和 TX_INT_DATAWIDTH 相同的模式下,数据暂停两个 TXUSRCLK2 周期;在TX_DATA_WIDTH 是 TX_INT_DATAWIDTH 两倍的模式下,数据暂停 1 个 TXUSRCLK2 周期。有效数据传输在下一个 TXUSRCLK2 周期恢复。下表描述了各种模式的 TXSEQUENCE 暂停位置(仅 64B66B)。

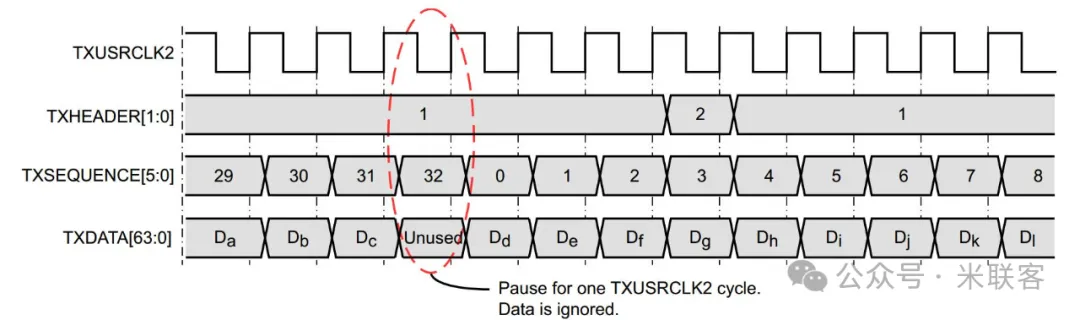

如下图所示,当在外部序列计数器模式下使用 8 字节互连逻辑接口和 4 字节内部数据路径并在正常模式下使用64B/66B 编码时,计数器值 32 处发生暂停。该要求仅仅是对同步编码模式有要求,异步编码器并没有这个要求。

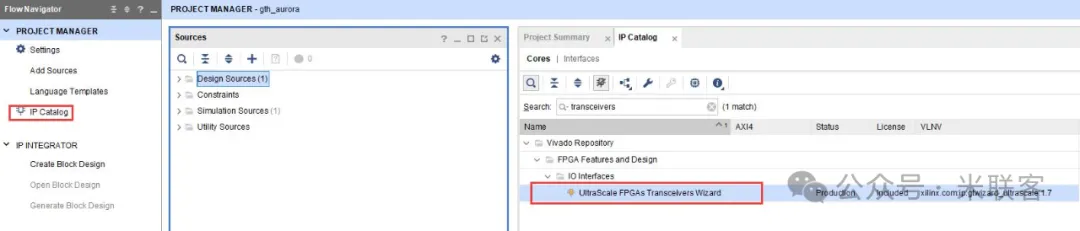

UltraScale FPGAs Transceivers Wizard IP 核设置

首先创建一个工程,添加 UltraScale FPGAs Transceivers Wizard IP

Transceiver 配置

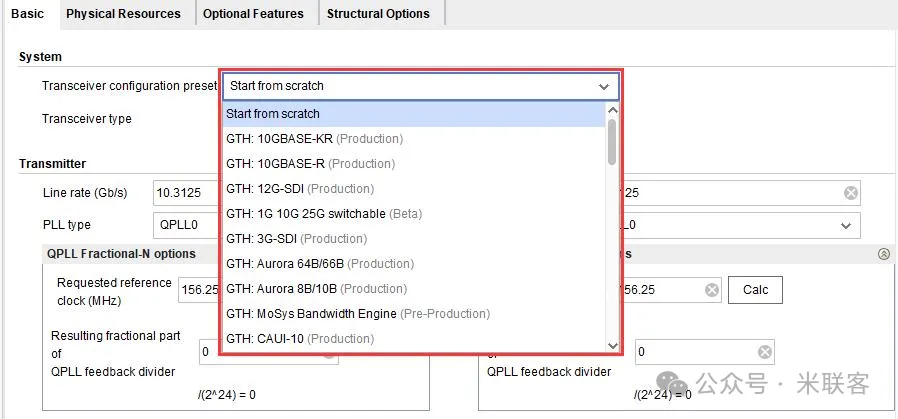

Transceiver 配置预设:UltraScale FPGAs Transceivers Wizard IP 提供了一些标准的预设配置可供选择,比如 aurora8B/10B、aurora 64B/66B、3G-SDI、12G_SDI 等配置,在应用预设后,还可以根据特定系统的需求进行进一步的修改。如果需要全部进行自定义配置,可以将这个选项设置为“Start from scratch”。

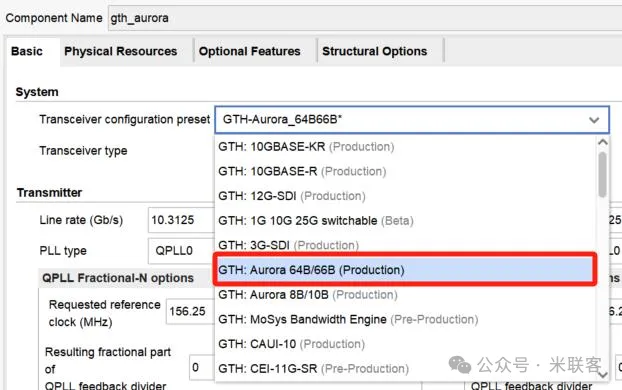

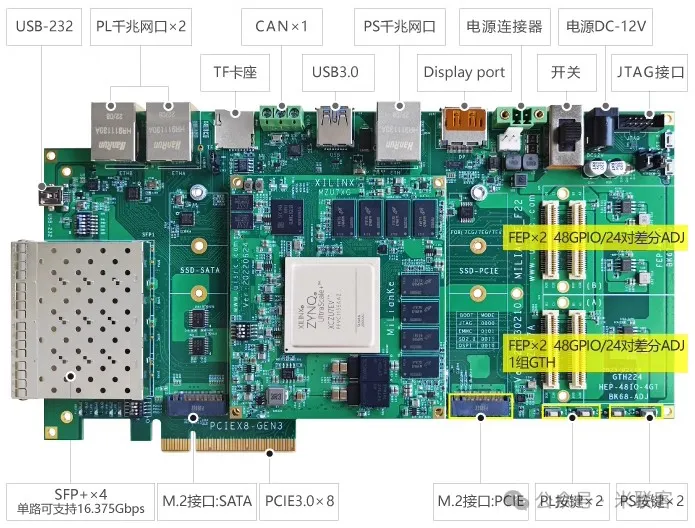

这里的预设配置选择 GTH-Aurora_64B66B 即可。串行收发器类型取决于使用的具体设备,以 MZU07A 板卡为例,它的 SFP+仅支持 GTH 类型。

载入预设的配置

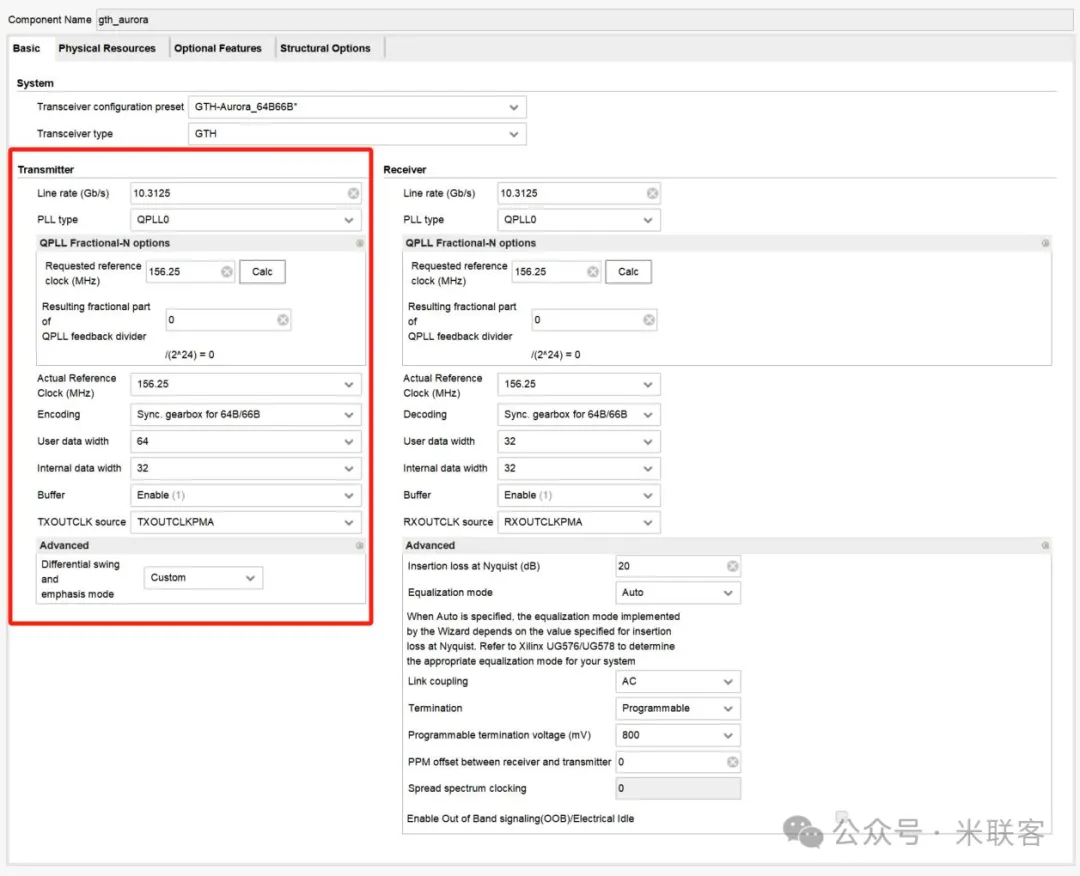

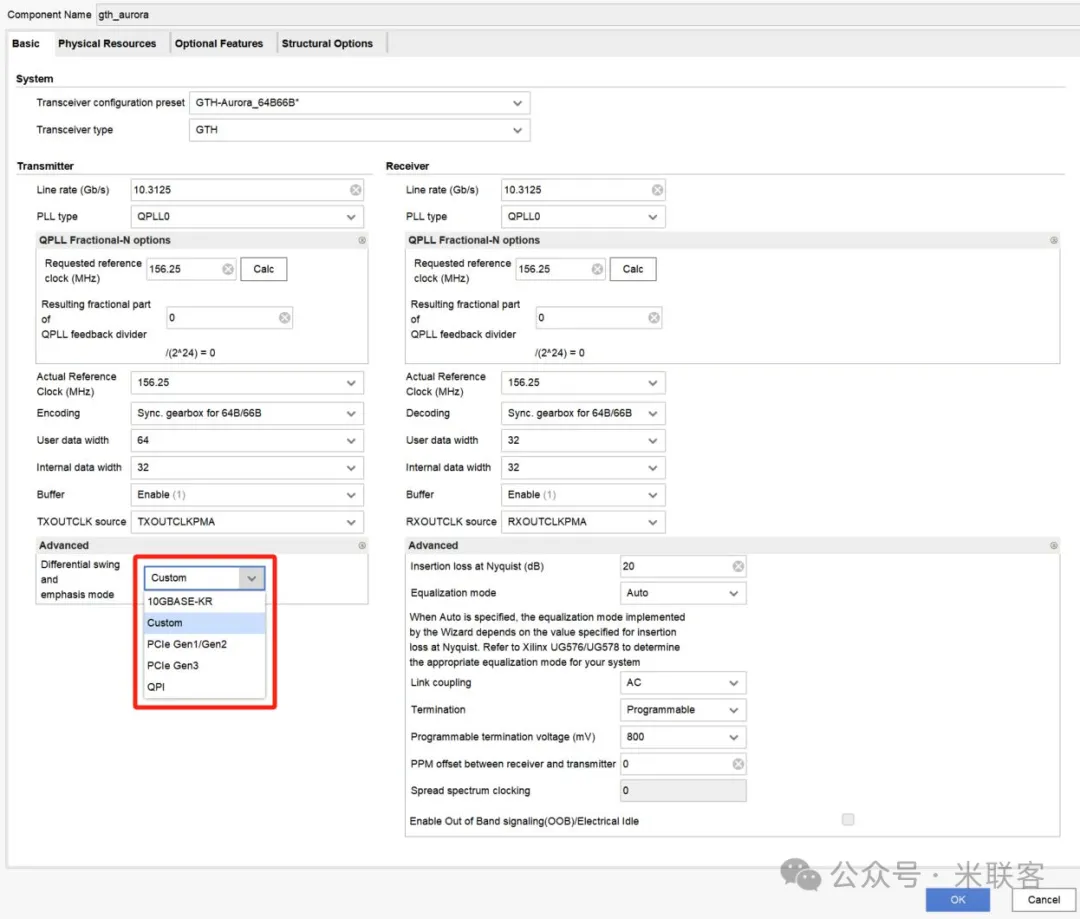

Transmitter 框架

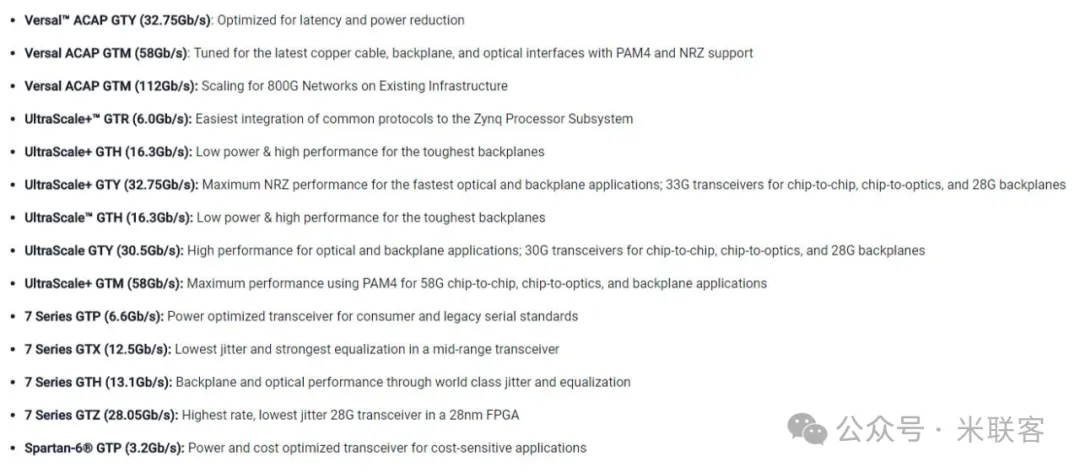

• Line rate (Gb/s):设置发送端的线路速率为 10.3125Gbps,可用范围取决于收发器类型。7 series 系列的 GTP 最高支持 6.6Gbps,GTX 最高支持 12.5Gbps,ultrascale+系列的 GTH 收发器最高支持 16.3Gbps(这边要特别注意一下,sfvc784封装的芯片 GTH 最高支持 12.5Gbps),GTY 最高支持 32.75Gbps。

• PLL type:

用于为启用的串行收发器通道的发送器提供时钟的所需 PLL 类型。可以看到选择 QPLL0,QPLL1 和 CPLL,针对于 ultrascale 系列的 GTH 收发器,他们的标称的工作范围如下:CPLL(2.0~6.25Gbps)、QPLL0(9.8~16.375Gbps)、QPLL1(8~13Gbps)。

• QPLL Fractional-N options:

针对 QPLL 的设备中去支持分数 N 反馈分频器的配置,可选值为 0 到 16777215,其中 0 禁用小数 N 进制运算。

• Actual reference clock(MHz):

选择实际的频率作为参考时钟,提供给选定的 PLL,以满足 line_rate 的需求。

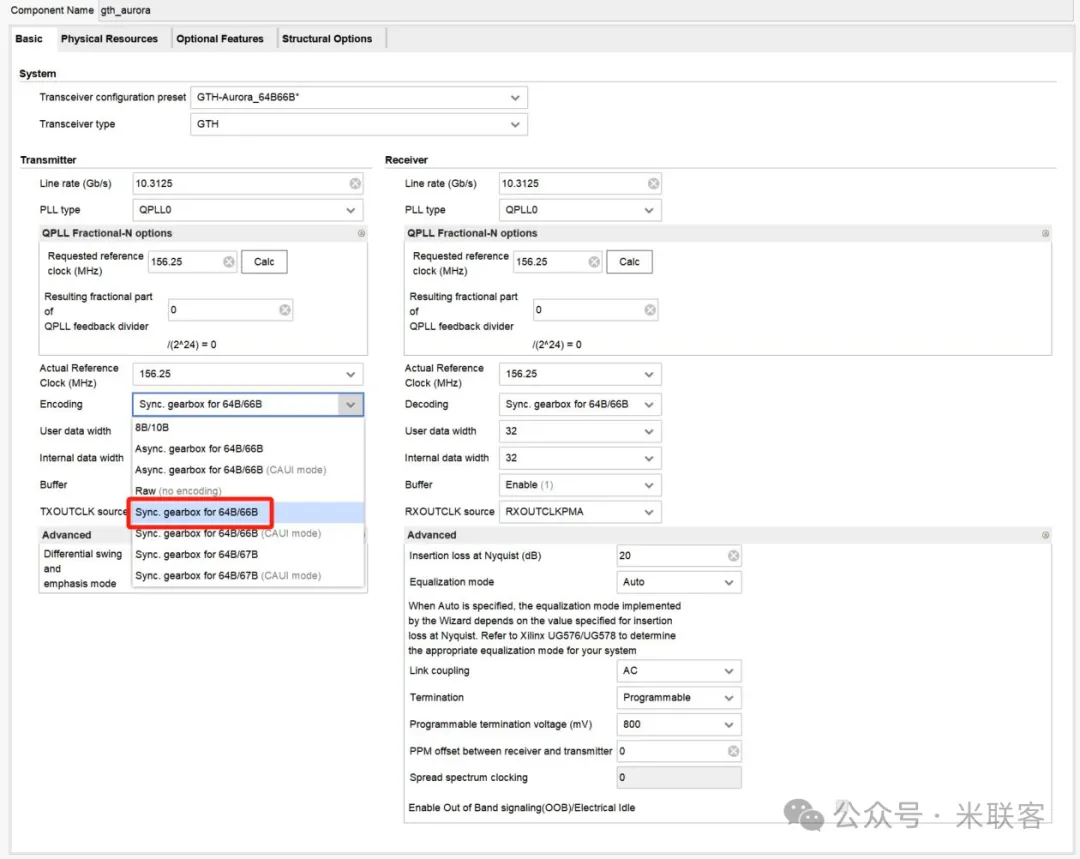

• Encoding:

选择收发器在传输数据时应用的编码类型或数据格式处理方式,这里选择 sync:gearbox 64B/66B 的编码格式,sync 为同步编码模式,async 为异步编码模式,我们以介绍同步编码模式为主,但是也提供异步编码模式的 demo,有需要的可以自行去学习。

• User data width:

设置每个串行收发器通道的外部用户数据宽度为 64。

• Internal data width:

设置每个串行收发器通道内部发送端的数据路径位宽为 32。

• Buffer:

这边官方默认推荐启用 buffer。

• TXOUTCLK source:

选择 TXOUTCLKPMA 即可,TXOUTCLKPMA 是 TX 相位插值器后的分频锁相环时钟,由 TX PCS 模块使用,当锁相环被一个相关的复位信号复位时,该时钟被中断。不建议使用 TXOUTCLKPCS,因为它会引起 PCS 模块的额外延迟。

更多关于 高速串行通信光口通信方案的资料(附带源码),在下方链接中:

https://pan.baidu.com/s/1i1Sw-QCEjR4E6lkrnju-OA?pwd=1nqz

本方案使用到的应用平台为:MLK-F22-CM03-7EV

本文转载自:米联客