Vivado Design Suite 用户指南: 设计分析与收敛技巧

judy 在 周六, 05/11/2024 - 09:40 提交

本文档涵盖了如何驱动 AMD Vivado™ Design Suite 来分析和改善您的设计

本文档涵盖了如何驱动 AMD Vivado™ Design Suite 来分析和改善您的设计

本文可让开发者们看懂 AMD Vivado™ Design Tool 2023.2 中的“AMD Versal™ Adaptive SoC CPM PCIE PIO EP 设计”CED 示例。

AMD 提供了支持不同速度的多种以太网 IP。此外,还提供了设计示例供用户用作参考。请参阅以下以太网设计示例列表。

本参考设计基于ZYNQ开发板, 使用VDMA做原始图像采集系统,在petalinux下做服务器,通过Socket发送图像至Windows或者Linux上位机。

劳特巴赫的 PowerDebug 模块设计选用了 AMD Zynq™ UltraScale+™ MPSoC。该器件以优化的异构处理引擎组合形式提供了出色的处理、I/O 和内存带宽

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。

本文将会详细介绍关于DPU Fingerprint的相关内容,并提供此类校验失败问题的检查手段和解决方案。

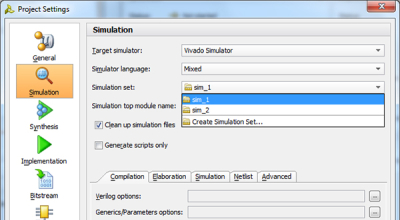

Vivado 具有一个功能特性,能够将这些文件便利地排列组合为多个可轻松访问的不同仿真集。本文描述了如何在 Vivado 中使用多个仿真集。

本文主要讨论一下如何在外部数据文件中指定RAM 初始内容。

本章使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性