Vivado Design Suite 用户指南: 设计分析与收敛技巧

judy 在 周六, 05/11/2024 - 09:40 提交

本文档涵盖了如何驱动 AMD Vivado™ Design Suite 来分析和改善您的设计

本文档涵盖了如何驱动 AMD Vivado™ Design Suite 来分析和改善您的设计

通过阅读本文,可以快速掌握Modelsim的常用调试操作。

本文对Vivado编译时常见的错误或者关键警告做一些梳理汇总,便于日后归纳总结。

今天给大侠带来Vivado调用IP核详细操作步骤,手把手教学,请往下看

在使用Vivado进行FPGA设计时,大家是否会遇到中文注释显示乱码的问题,而且在乱码时修改代码,导致文件注释更乱了,且恢复不了,那么如何解决呢?

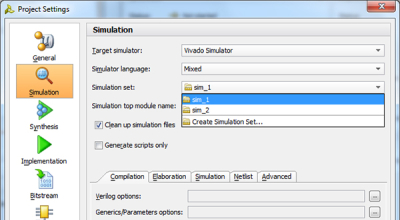

Vivado 具有一个功能特性,能够将这些文件便利地排列组合为多个可轻松访问的不同仿真集。本文描述了如何在 Vivado 中使用多个仿真集。

本文主要讨论一下如何在外部数据文件中指定RAM 初始内容。

本文记录描述了如何在仿真集内选择不同的顶层模块。

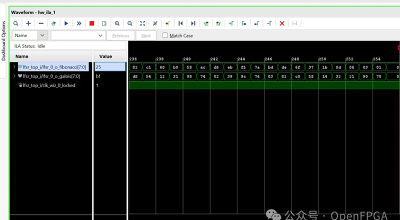

ILA应该是调试AMD-Xilinx FPGA最常用的IP。在调试中,我们希望ILA中的波形能够提供有关设计问题的所有信息,但情况并非如此

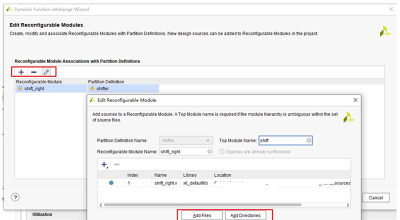

本文介绍在Vivado中用工程模式使用DFX流程以及需要注意的地方。