Vitis 简介

AMD Vitis™ 工具套件包含多种设计技术,用于开发以 AMD 器件(例如,AMD Versal™ 自适应 SoC 器件、AMD Zynq™ MPSoC 和 AMD Alveo™ 数据中心加速器卡)为目标的异构嵌入式应用。

Vitis 工具包括:

C++ 编译器、库和本征函数,适用于 AI 引擎和可编程逻辑( PL )

适用于 Arm 和 MicroBlaze CPU 的传统工具链和库

图形化集成设计环境( IDE )

系统连接器,用于配置复杂的器件子系统,如 AI 引擎、NoC 和 Control & Integrated Processing system( CIPS ),并将其与高性能多速率系统中的 PL 模块与内核相集成

调试器和硬件/软件检测自动化,有助于定位和解决嵌入式系统中的性能瓶颈和问题

跨 PL( HDL )、AI 引擎( System-C ) 和 CPU( QEMU )无缝编译、链接和运行异构仿真

程序分析器,用于剖析和可视化仿真中和目标上的硬件/软件性能

Xilinx Runtime( XRT )提供 Linux 用户空间 API,用于运行时镜像加载、存储器管理与内核控制

开发平台,提供开箱即用的沙箱,用于 AI 引擎 开发、PL+AI 引擎子系统开发以及嵌入式系统应用引导

硬件优化的库,用于 DSP、视觉和图像处理、线性代数和诸多其他应用域

Vitis 工具套件是基于 AMD Vivado Design Suite 构建的,支持硬件和软件的 C/C++ 编程、灵活且可缩放的系统连接规格用于促进自上而下、中间向外和自下而上的设计迭代、RTL 模块集成、清晰的底层 Vivado 硬件工具流程自动化和交接。

Vitis 关键概念

本主题介绍的关键概念有助于您了解和使用 AMD Vitis™ 工具来开展嵌入式系统设计。这些工具支持通过以下方式完成各种开发流程:使用脚本编制执行开发或者通过 Vitis IDE 进行交互式设计输入来执行开发。所有开发流程均以相同结果为目标,但设计师的技能等级和工程要求可能会影响特定流程类型的倾向性。下表描述了这些步骤。

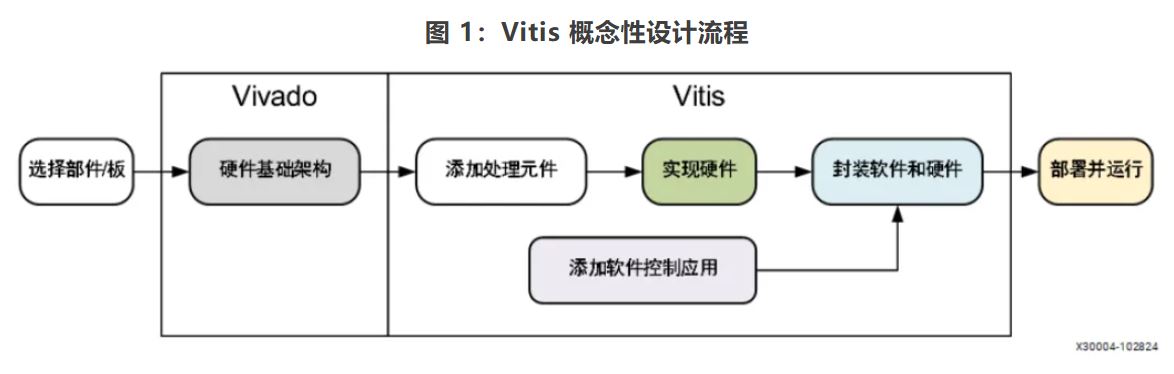

下图演示了设计嵌入式系统并将其与 AMD 工具集成的概念性流程。

Vitis 工具支持多种不同的设计流程,如第 3 章:Vitis 流程和构建环境所述。以下章节着重讲解了用于创建和集成这些不同组件的各种工具和技巧。

获取完整版用户指南请扫描左侧二维码进行下载

文章来源:Xilinx赛灵思官微