本文转载自:FPGA入门博客

1、参考资料

xilinx 官方 PG066 PG198

http://www.chinaaet.com/tech/designapplication/3000080357

jesd204b应用指南

https://github.com/analogdevicesinc/hdl

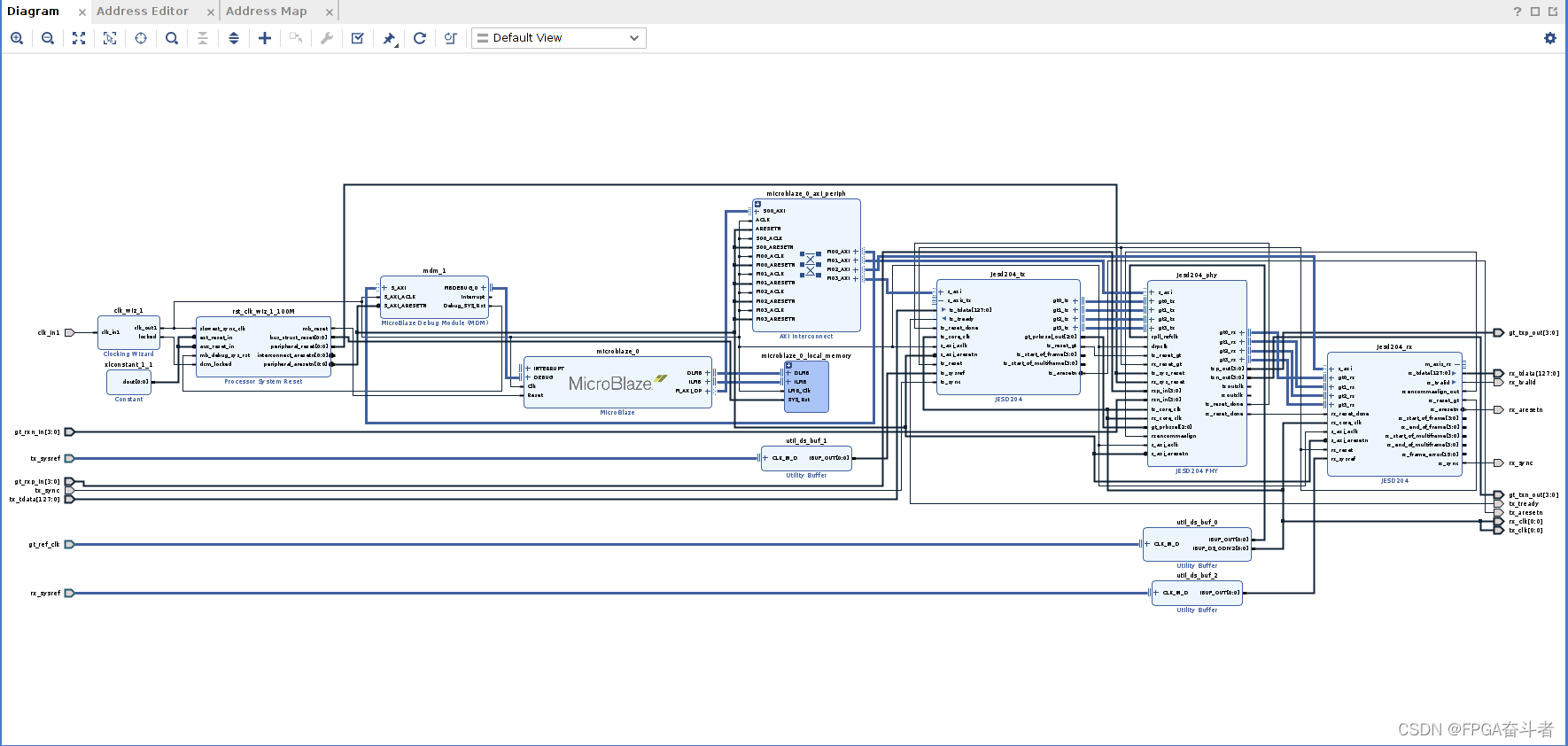

2、工程搭建

3、概述

系统主要采用官方JESD_PHY(免费),JESD_RX(评估版),JESD_TX(评估版)三个IP核做测试,采用自发自收,外部GT引脚回环方式。其中,PHY采用4个LANE接收和发送数据,一般线速率为参考时钟的40倍,这样的一个好处就是用户端的接收数据是连续的。模式分为三类,一般应用的都是子类1。

4、部分名词解释

(1)确定性延时

延时可重复,且相对固定

在adc端来看,每个通道的延时都是相同的,虽然无法保证数据并串-串并转换后会同时到达接收端,但是可以保证采样时间是同一时刻,相位相对固定。

(2)LMFC

adc中一个多帧的周期,类似于一个隐形的时钟,这个时钟的边沿,会发送一个多帧。

(3)SYNC

同步信号,当信号为低时,发送端发送K码(K28.5),拉高时,发送端在第一个LMFC边沿处开始发送四组多帧数据,多帧数据以不同的K码开始和结束,第二个多帧比较特殊,包含一些属性数据,其他三组多帧数据暂时未发现特殊意义,仅仅为同步头而已。发送多帧数据后,开始发送采样数据。

(4)SYSREF

LMFC同步信号,当采样时钟采样到SYSREF信号时,会强行将LMFC的起始位置对齐到此处,实现LMFC对齐,当多个通道的LMFC对齐后,则采样的第一个数据也会对齐,规定SYSREF的周期必须是LMFC的整数倍,由此可见,只有刚开始的对齐才有意义。

比如我的芯片采样时钟为500M,采用4倍降采样,也就是类似于125M的数据输出速率,多帧长度为32,则LMFC=(1\500M)232=128ns 则SYSREF必须为128ns的整数倍,可以是脉冲信号,也可以是周期信号,但是高电平持续时间最少为采样时钟的2倍,一般采用周期信号,占空比为50%。

(5)建立和保持时间

在实际使用时,需要调节SYSREF的相位来满足采样时钟对SYSREF信号的建立和保持时间,一般将期间采样时钟的上升沿滞后于SYSREF上升沿,然后保持最少两个采样时钟周期。

(6)

F

短帧字节数

K

每个多帧中包含短帧的个数

S

每个短帧的样本数

(7)器件时钟

对于ADC来说,是采样时钟,对于FPGA来说,是用户时钟,这两个时钟频率可以是不同的,但是必须是同源的。

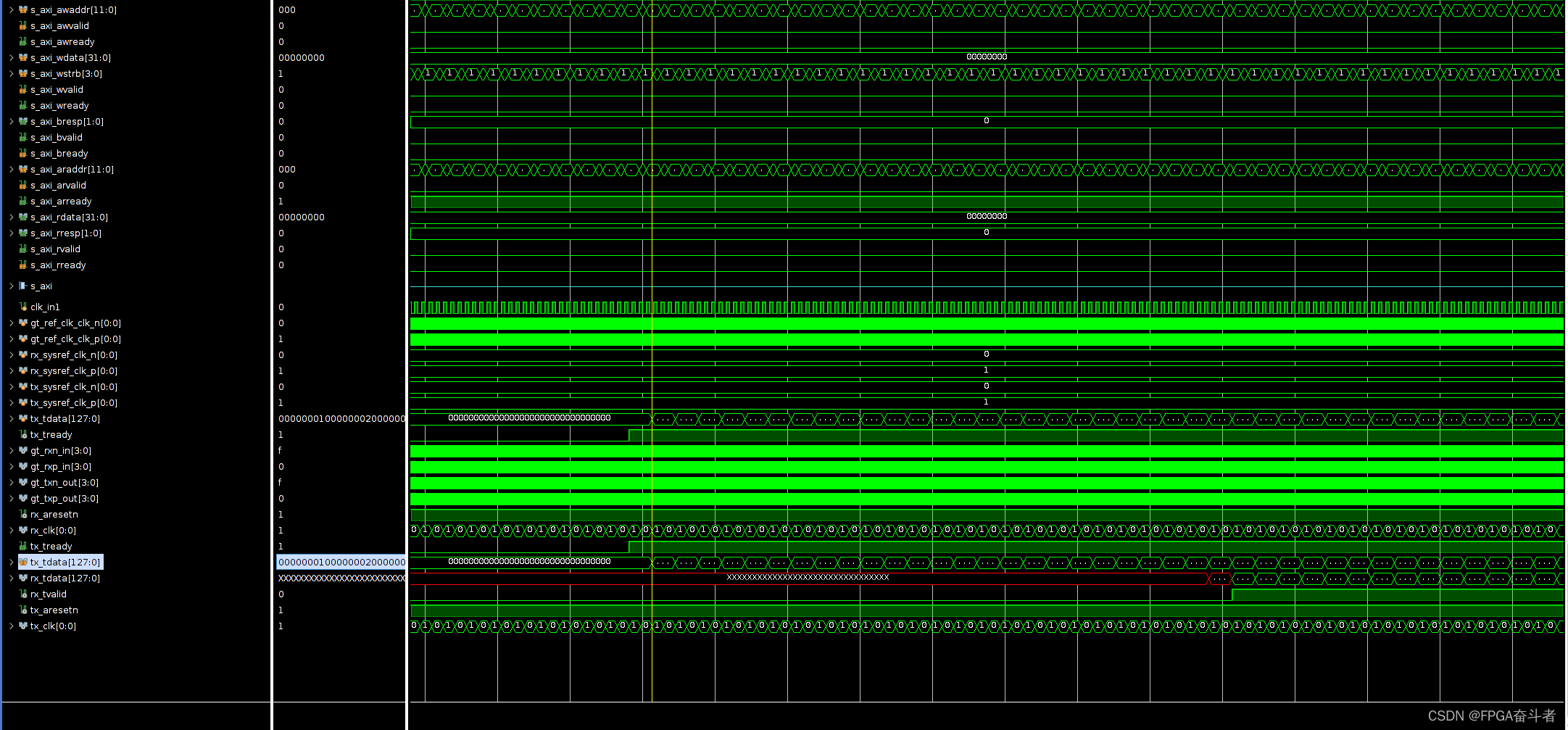

5、仿真

在sdk中对链路层进行初始化

由仿真可以看出,最开始链路进行训练时,发送k码(k28.5),当链路训练结束后,发送四个多帧,每个多帧64Byte,然后ready拉高,开始发送数据,数据经外部gt直接环回,在接收端valid拉高,输出接收的数据,由仿真中可以看出,发送和接收的数据是相同的,由此可以看出,链路是正确的。

6、实物验证

将工程中的tx去掉,加入约束,编译生成bit,导入sdk

sdk中初始化流程

(1)配置时钟芯片

(2)配置adc芯片9694

(3)配置FPGA接收端属性

(4)使能信号发生器100M

(5)是能FPGA内部1024点FFT,可以输出在100M处得到能量最大索引,同时用ila抓取数据,为一个正弦波

7、工程链接

https://download.csdn.net/download/sinat_39724439/65633711