作者:张大侠,来源:傅里叶的猫

set_input_delay属于时序约束中的IO约束,我之前的时序约束教程中,有一篇关于set_input_delay的文章,但里面写的并不是很详细,今天我们就来详细分析一下,这个约束应该如何使用。

首先还是需要明确一点,这个约束没有延迟的作用,如果需要对输入信号做延迟,就要使用IODELAY这种原语。

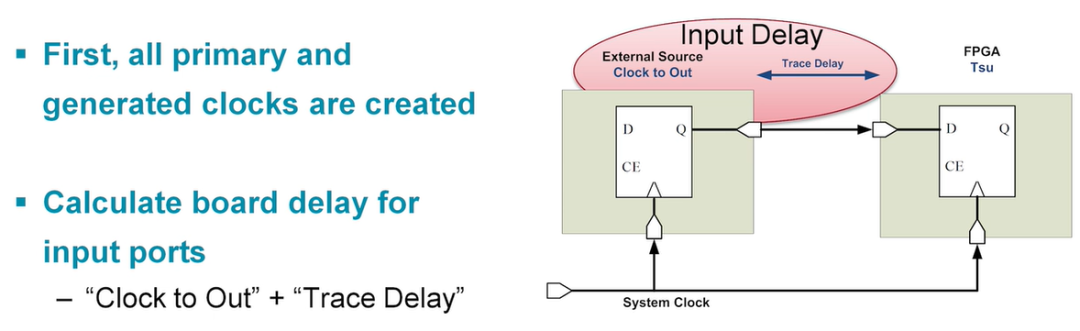

什么是input_delay?

input_delay是指输入的数据到达FPGA的pad时相对于时钟边沿的延迟有多大,单位是ns,数值可以是正,也可以是负。

假设时钟是没有skew的,那么上图中的input_delay就等于Clock to Out+Trace Dealy,即上游器件的时钟到触发器输出的延时+PCB上的布线延迟,即Tco+Tdelay。

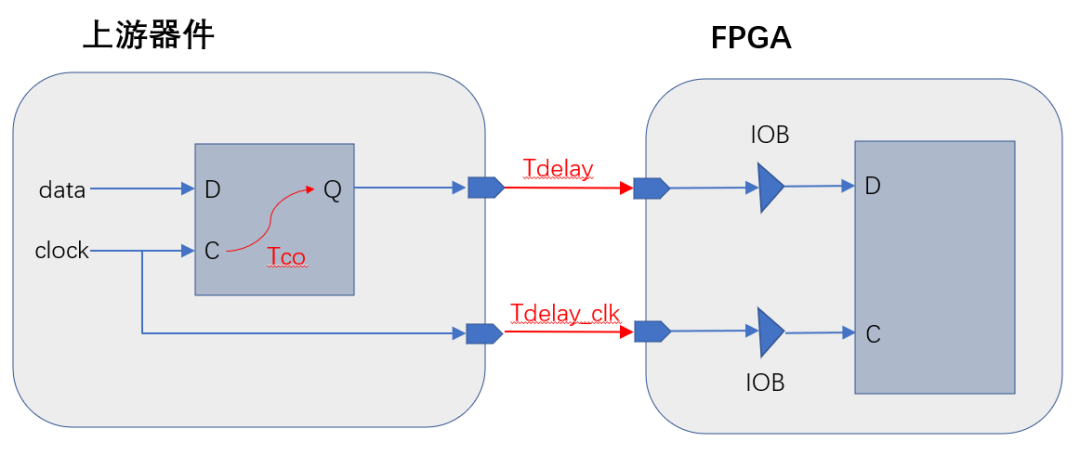

但我们实际的应用,碰到的大多数情况都是随路时钟,也就是说上游器件输出数据的同时也会输出时钟给FPGA,就像下图所示:

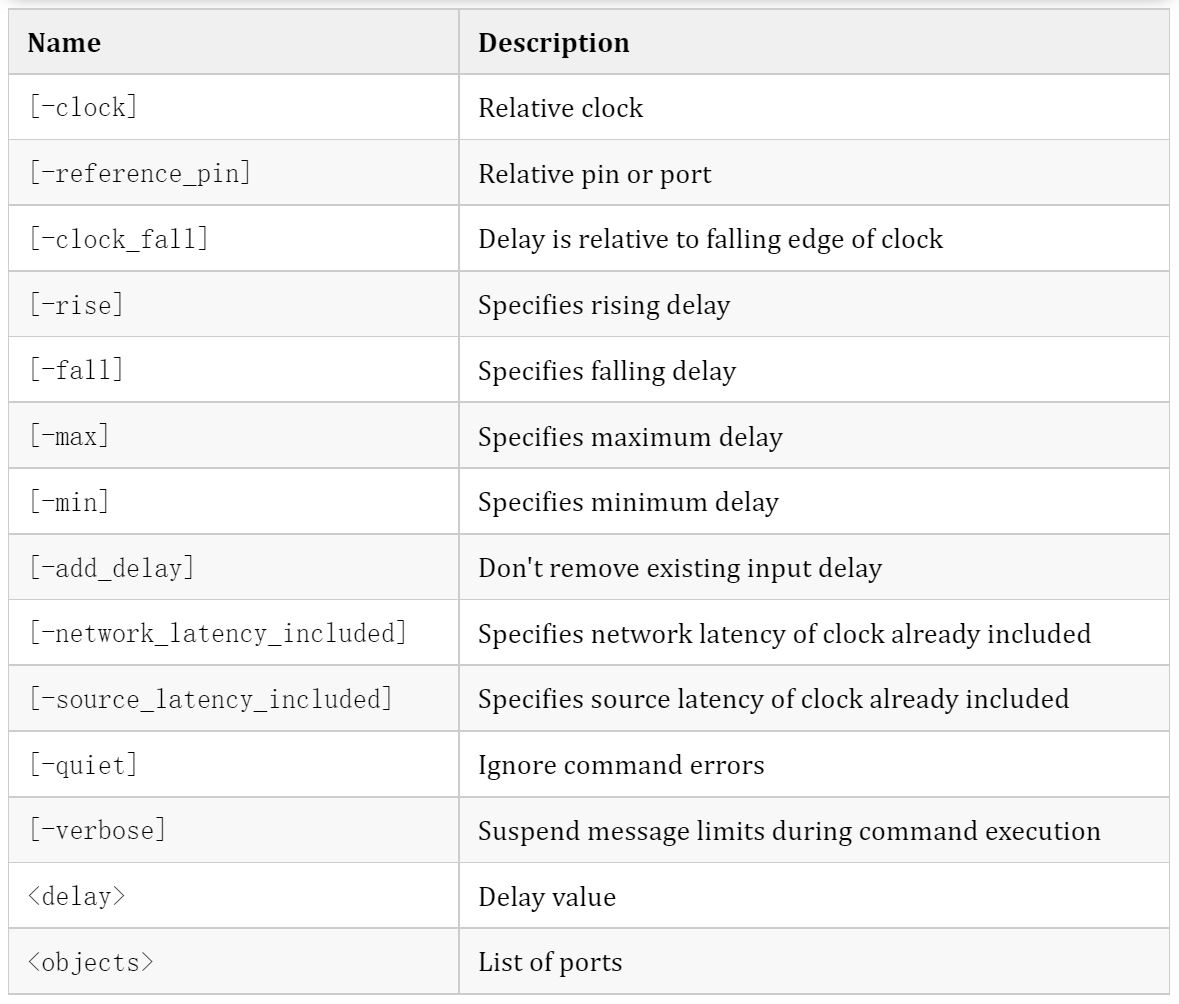

set_input_delay语法

set_input_delay [‑clock <args>] [‑reference_pin <args>] [‑clock_fall]

[‑rise] [‑fall] [‑max] [‑min] [‑add_delay] [‑network_latency_included]

[‑source_latency_included] [‑quiet] [‑verbose] <delay> <objects>

下面来详细说明一下:

-clock:input_delay一般是相对时钟而言的,而且默认是相对于上升沿,我们可以通过clock_fall参数来指定下降沿,这里的时钟可以是虚拟时钟;

-reference_pin:指定相对于某个pin上的时钟边沿,跟-clock的参数其实是一个意思,毕竟时钟也是通过pin输入进来的;

-clock_fall:指定相对于时钟下降沿

-rise:指定端口的上升转换的输入延迟

-fall:指定端口的下降沿的输入延迟

-max:最大延迟

-min:最小延迟,我们做input delay主要就是约束这两个参数

-add_delay:以增量的方式添加延迟,如果不加该参数,默认行为是替换现有的延时

-network_latency_included:表示参考时钟的网络延迟也包含在延迟中

-source_latency_included:跟上一个参数类似的含义,该参数表示时钟的源端延迟包含在延时中

-quiet:忽略指令的错误信息,即便指令错了也依然返回TCL_OK

-verbose:命令执行期间忽略消息数量的限制,就是说会返回该指令的所有的message

delay:延迟值

objects:端口列表

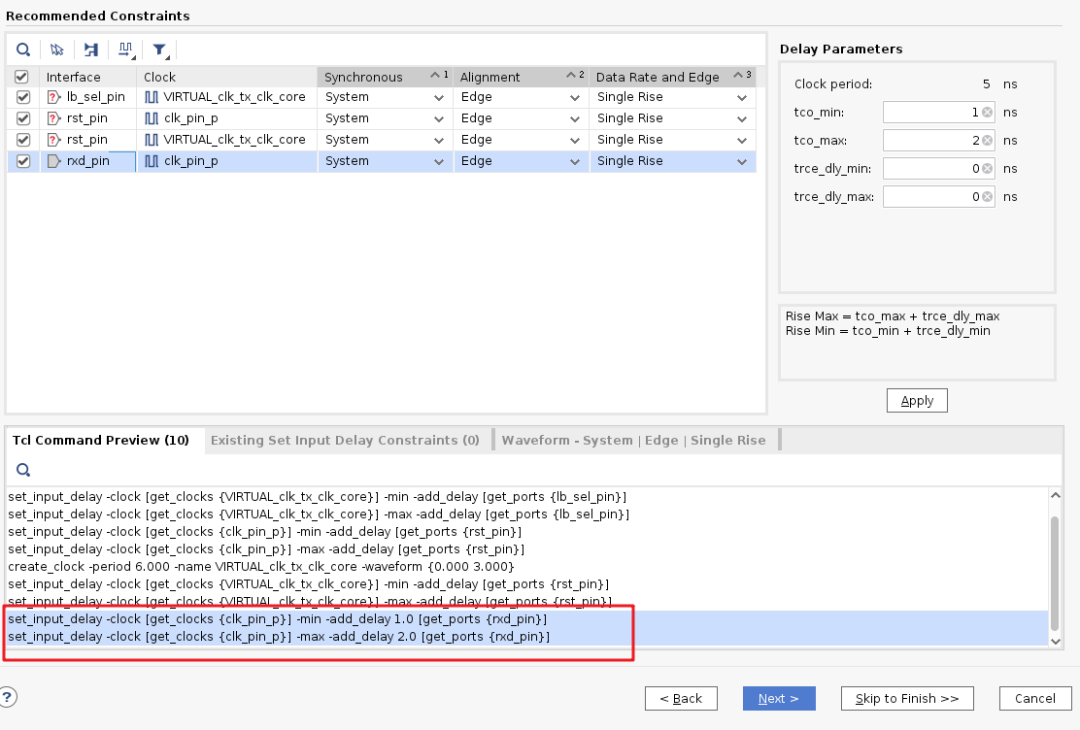

Vivado Timing Constraints Wizard

很多约束时钟vivado中的Timing Constraints Wizard工具会方便很多,对于input delay的约束,界面如下:

我们需要设置的就是数据相对于时钟的最大和最小的延时,trce_dly_min和trce_dly_max是指布线的延迟,一般随路时钟跟数据都会采用等长布线的方式,因此可以设置为0即可。

在设置完成后,下面的Tcl Command Preview中就会出现约束的tcl语法,这种方式对于该约束是很了解或者懒得手写约束的朋友来说非常的方便。

Examples

1.输入数据比时钟延迟3ns的delay:

create_clock -name clk -period 10 [get_ports clk_in]

set_input_delay -clock clk 3 [get_ports DIN]

2.输入数据相对于时钟的下降沿有2ns的delay:

set_input_delay -clock_fall -clock clk 2 [get_ports DIN]

3.复位管脚相对于BUFG输出的时钟有2ns的delay:

set_input_delay -clock wbClk 2 -reference_pin [get_pin wbClk_IBUF_BUFG_inst/O] [get_ports reset]

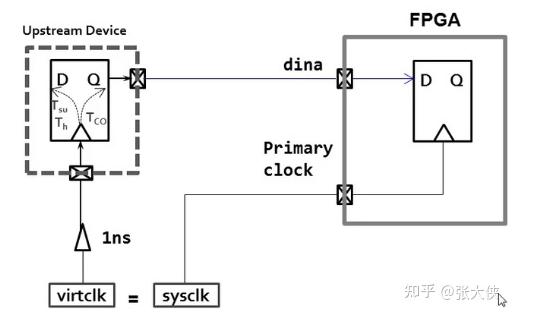

4.时钟虚拟时钟的约束

虚拟失踪的具体时钟方式可以参考另一篇文章

外部IO的参考时钟比设计中主时钟的路径上多了一个BUFFER

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virtclk -period 10

set_clock_latency -source 1 [get_clock virtclk]

set_input_delay -clock virtclk -max 4 [get_ports dina]

set_input_delay -clock virtclk -min 2 [get_ports dina]

5.双沿时钟的约束,对上升沿和下降沿都需要进行约束

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

set_input_delay -clock clk_ddr -max 2.1 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -max 1.9 [get_ports DDR_IN] -clock_fall -add_delay

set_input_delay -clock clk_ddr -min 0.9 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -min 1.1 [get_ports DDR_IN] -clock_fall -add_delay

具体案例

比如某器件手册的输出时钟与数据的setup和hold要求如下图:

该时钟双沿采样,在时钟边沿到来后,结合input_delay的最大最小延迟的定义,可以知道:

最小延迟就是hold time,因为如果比hold time还小了,那保持时间就不满足了,即1.2ns 最大延迟是时钟周期-setup time,这里上下沿之间的间隔是4ns,因此max delay是2.8ns

因此input delay的约束如下:

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD0] -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD1] -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD2] -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD3] -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXC] -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD0] -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD1] -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD2] -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD3] -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXC] -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD0] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD1] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD2] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXD3] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -min 1.200 [get_ports RXC] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD0] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD1] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD2] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXD3] -clock_fall -add_delay

set_input_delay -clock [get_clocks rx_clk] -max 2.800 [get_ports RXC] -clock_fall -add_delay

因此,只要记住:

min_delay就是上游器件的hold time max_delay是时钟周期-上游器件的setup time 如果是双沿的话,就是半个时钟周期,而且还需要对时钟的下降沿进行约束