本文转载自: FPGA打工人

新的DSI-2协议定义了两个高速串行数据传输接口选项。

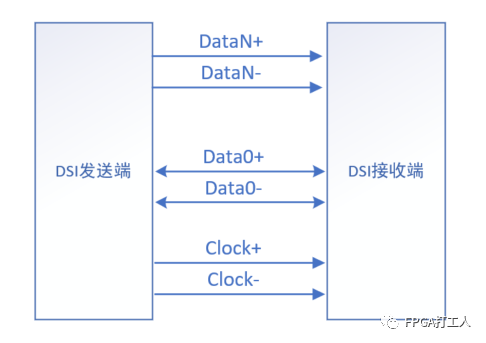

第一个选项被称为D选项,是具有一个2线时钟通道和一个或多个2线数据通道的高速差分接口(通道0在LP模式下可能是双向的)。具体如下图:

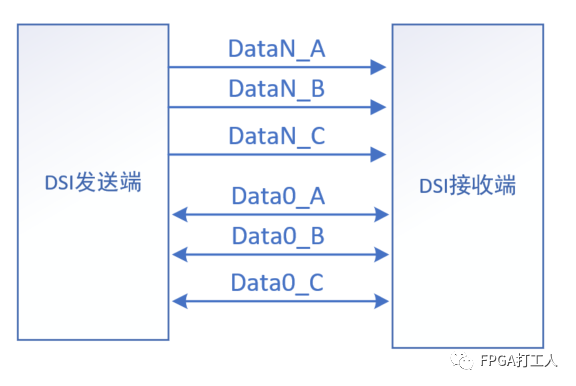

第二个选项被称为C选项,由一个或多个3线串行数据通道组成,每个通道都有自己的嵌入式时钟。如下图所示,当通道0处于LP模式时,应通过Data0_A和Data0_C传输线进行数据传输,而将Data0_B驱动到低电平状态(通道0在LP模式下可能是双向的)。

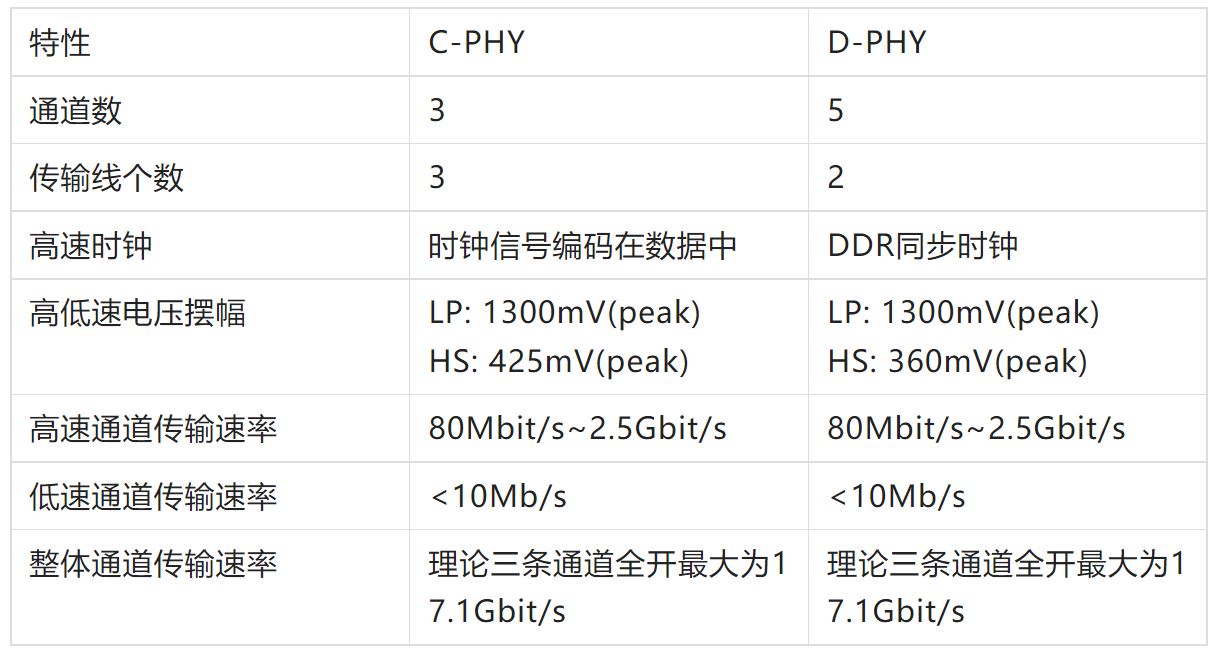

C型和D型物理层的简单对比

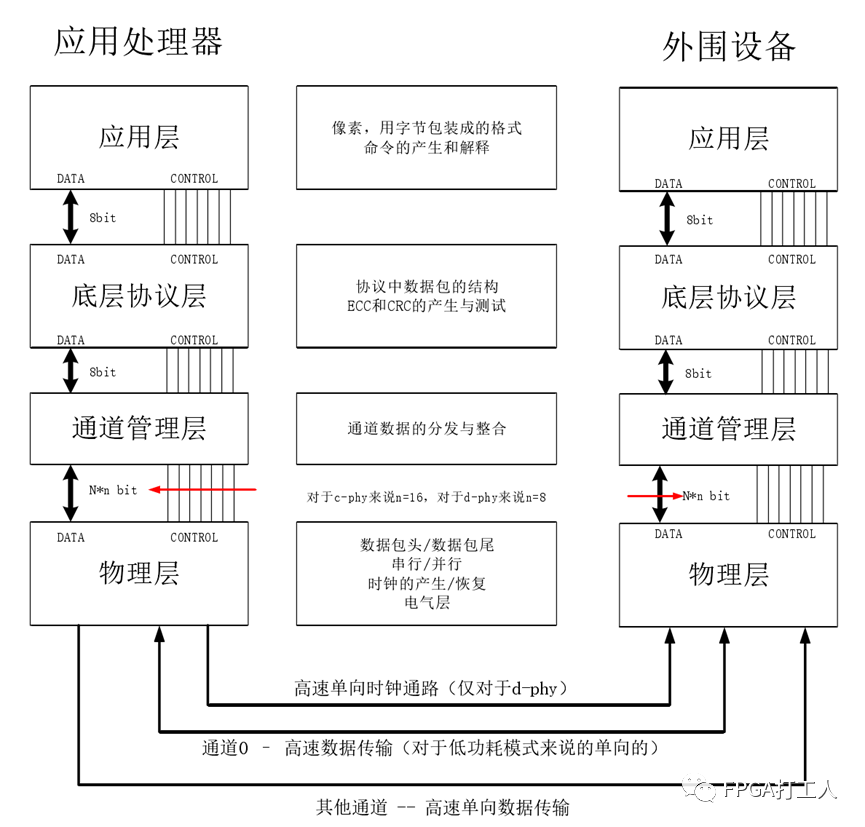

DSI的功能层

物理层:物理层定义了传输介质,记录了高速传输模式和低功耗传输模式不同的电气特性,以及时钟和数据通道之间的时序关系。其中同时指定了数据传输以SoT开始,以EoT传输结束的机制。

数据通道管理层:对于D型物理层,其最多支持4条通道传输,接口的发送端将传出数据流的字节分配到一个或多个通道。在D型物理层的接收端,接口从通道中收集字节,并将其合并到重组的数据流中,以恢复原始数据流序列。而对于C型物理层,其通道最多支持3条。

底层协议层:底层协议层主要对通道中的数据进一步处理,定义了字节如何被组成数据包,同时也定义了每个数据包所需的包头,以及包头信息的生成方式。

应用层:此层描述数据流中包含的数据更高级编码和含义。比如像素值、指令和指令参数等数据包。

UltraScale+支持MIPI D-PHY

仅限Virtex UltraScale+、Kintex UltraScale+和Zynq UltraScale+器件的HP I/O bank才支持MIPI D-PHY标准标准。与其他DCI标准一样,MIPI_DPHY_DCI在VRP管脚上需要一个240欧外部电阻。针对接收和发射提供了具体的原语使用。接收对应的IBUFDS_DPHY,发射对应的是OBUFDS_DPHY。

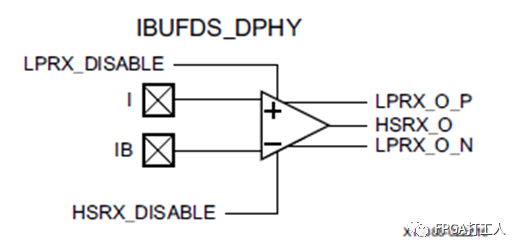

IBUFDS_DPHY:HSRX_DSABLE端口用于启用或禁用MIPI D_PHY高速(HS)接收器。LPRX_DISABLE端口用于启用或禁用低功耗(LP)接收器。HSRX_O和LPRX_O(_P/_N)分别从HS和LP接收器输入到内部处理网络。该原语仅支持MIPI_DPHY_DCI作为IOSTANDARD属性的值。

OBUFDS_DPHY:HSTX_T端口用于将MIPI D-PHY高速(HS)发射器设为三态。LPTX_T端口用于将低功耗(LP)发射器设为三态。HSTX_I和LPTX_I(_P/_N)输入分别对应从内部处理网络到HS发射器和LP发射器。该原语仅支持MIPI_DPHY_DCI作为IOSTANDARD属性的值。

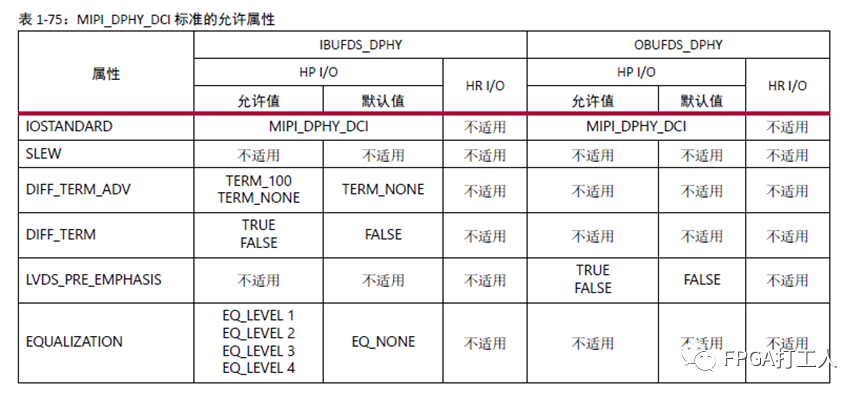

MIPI_DPHY_DCI标准的允许属性

需要注意一点:从vivado2019.1开始,LVDS_PRE_EMPHASIS属性可供MIPI_DPHY_DCI使用。将LVDS_PRE_EMPHASIS属性设置为TRUE可提高MIPI_DPHY_DCI I/O的最大运行速度。为了适应vivado工具相应早期版本中速度较低的操作,应将LVDS_PRE_EMPHASIS设置为FALSE。

同样,也会有对应的MIPI IP,支持MIPICSI-2和DSI协议,能被配置为发送和接收的其一。Tx配置包括一个时钟通道和1-4个数据通道,Rx配置包括一个时钟通道和1-8个数据通道。在HS模式下,传输数据速率为80Mb/s到3200Mb/s;在LP模式下,所有线路都是单端线路,能够支持10Mb/s的异步数据通信。