本文转载自:Vuko-wxh的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

写在前面

本文对射频数据转换器(RFSoC RF Data Converter )进行了简要描述说明,参考了xilinx的PG269的手册第一二三章,用于快速了解RFSoC射频数据转换器的相关特性,接口,以便于后续使用RFSoC射频数据转换器进行开发设计。

简介

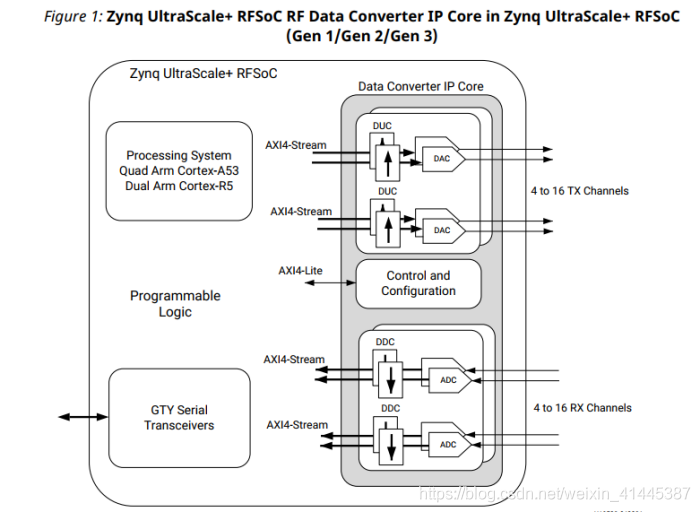

RFSoC射频数据转换器IP核提供了一个可配置的封装器,允许RF- DAC和RE-ADC块用于IP集成器设计。

特点

多达16个14位RF - DAC

第1代/第2代:4个12位二倍频RF-ADC,或4个12位四倍频RF-ADC

第3代:2或4个14位二倍频RF-ADC,和/或2或4个14位四倍频RF-ADC

支持多个转换器之间的对齐(多片同步(MTS))

支持预编程RF-DAC和RF-ADC,用户可以定义关键参数

RF-ADC和RF-DAC的多个AX14-Stream数据接口

单独的AX14-Lite配置接口

第1代/第2代:1x(旁路),2x, 4x, 8x抽取和插值

第3代:1x(旁路),2x, 3x, 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x, 24x, 40x抽取和插值后的额外的2x插值

数字复合混频器和数控振荡器(NCO)

正交调制校正(QMC第3代:每个RF-ADC的嵌入式数字步进衰减器(DSA),每个RF-DAC的可变输出功率(VOP)控制

片上时钟系统,包括每个磁片的锁相环

第3代:片上时钟分配网络

第3代:TDD模式支持省电模式和RX/Obs共享模式

概述

Zynq UltraScale+ RFSoC系列集成了实现完整的软件定义无线电所需的关键子系统,包括直接射频采样数据转换器,在单个高度可编程SoC上实现eCPRI和千兆以太网到射频。

每个RFSoC提供多个射频采样模数转换(RF-ADC)和射频采样数模转换(RF-DAC)数据转换器。该数据转换器具有高精度、高速和节能的特点。两者都是高度可配置的,并与Zynq UltraScale+ RFSoC的可编程逻辑(PL)资源紧密集成。

RF-ADC支持设备依赖的采样率和输入信号频率,具有卓越的动态范围性能。RF-DAC以Zynq UltraScale+ RFSoC定义的速率产生输出载波频率,取决于设备。

射频数据转换器还包括功率高效的数字下转换器(DDCs)和数字上转换器(DUCs),其中包括可编程插补和抽取率、数字控制振荡器(NCO)和复杂的混频器。DDC和DUCs也支持多频带操作。

RF-ADC和RF-DAC被组织成块,每个块包含一个、两个。或四个RF-ADC或一个、两个或四个RF-DAC。每个片还包括一个带锁相环的块和所有必要的时钟处理逻辑和模拟和数字逻辑的分配路由。

本文描述了Zynq UltraScale+ RFSoC射频数据转换器IP核和软件驱动程序,用于配置数据转换器并实例化它们,以便在设计中使用。

射频数据转换器框图

二倍频和四倍频RF-ADC/RF-DAC片

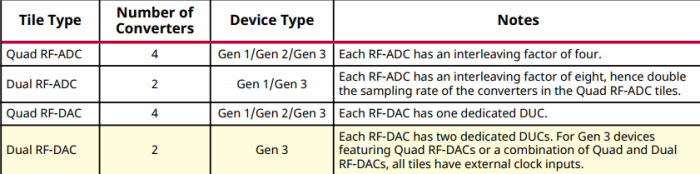

RF-ADC有两种类型的转换器片,称为二倍频和四倍频转换器片。对于RF-ADC, 二倍频片中的转换器具有不同的最大采样率和相比四倍频片的不同交错因子。

第1代/第3代设备有两种类型转换器片,而第2代设备只包含四倍频RF-ADC的转换器片。四倍频RF-DAC瓦可在第1/第2代设备和二倍频RF-DAC片可在第3代设备;Dual RF-DAC贴片为每个通道有两个专用的DUCs,以支持双频应用。在两种类型的RF-DAC贴片中,转换器之间没有性能差异。

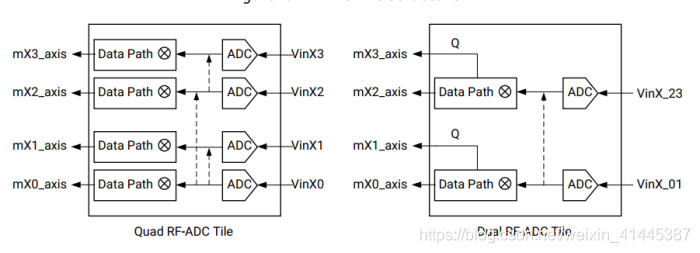

RF-ADC片结构

双RF-ADC片适用于Gen 1/3。

RF-DAC片结构

双RF-DAC片适用于Gen 3。

Single转换片结构 (Gen 3)

Single RF-DAC和RF-ADC片适用于第3代。

子ADC和交错因子

Xilinx使用交错技术来构建RF-ADC。Dual RF-ADC中的每个RF-ADC由8个子ADC组成,Quad RF-ADC中的每个RF-ADC由4个子ADC组成。作为交错因子提到的子ADC的数量是四倍RF-ADC瓦片的4个或双RF-ADC瓦片的8个。交错因子越高,RF-ADC支持的最大采样率越高。

外部时钟输入

在某些设备中,并非所有片都有外部时钟输入。

在第1代/第2代设备中,所有片都有一个外部时钟输入。

在第3代设备中,所有RF-ADC块都有外部时钟输入。在Quad RF-DAC的块中,所有RF-DAC块都有一个外部时钟输入。如果只有双RF-DAC块存在,则奇数RF-DAC块(RF-DAC块1和3)没有外部时钟输入。

没有外部时钟输入的已启用的片应该配置为从设备上的另一个片的接收时钟。

RF-ADC

有两种类型的RF-ADC片,双RF-ADC和四RF-ADC片。每个片包括一个锁相环和时钟电路。一个片中的所有RF-ADC共享这个公共时钟。

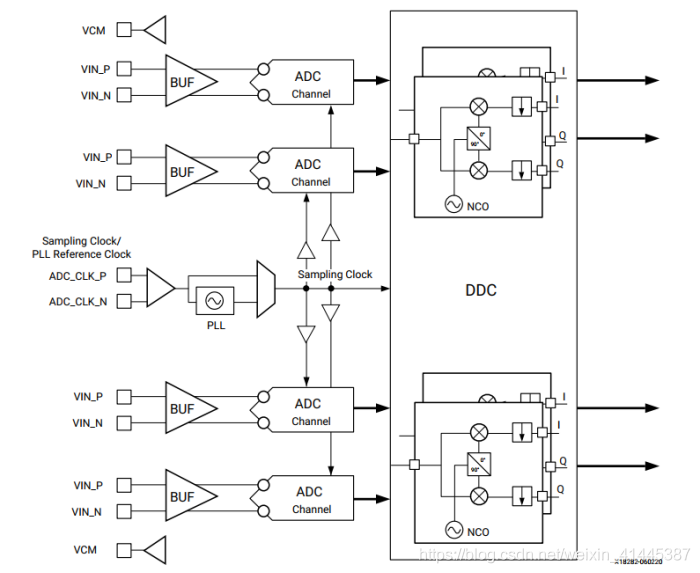

Quad RF-ADC片由四个RF-ADC组成,安排在两对。每个这些转换器可以单独配置为真实的输入信号,或作为一对,为IQ输入信号。下面的图显示了第1代/第2代和第3代四路RF-ADC片的概述。

Quad RF-ADC Tile Overview (Gen 1/Gen 2)

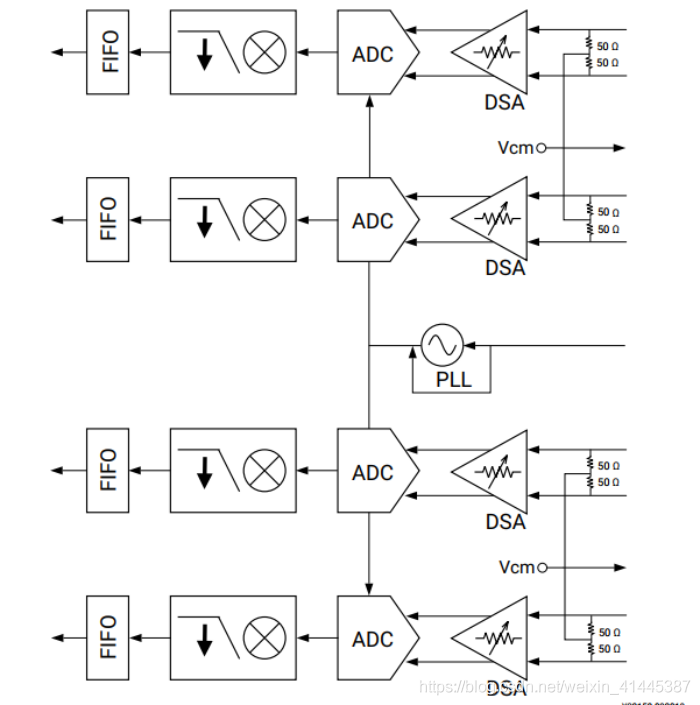

Quad RF-ADC Tile Overview (Gen 3)

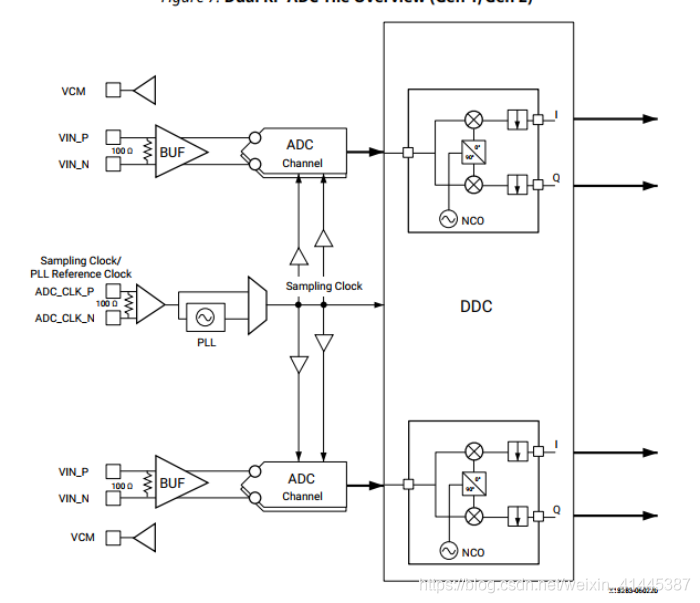

双RF-ADC模块由两个RF-ADC组成。这些转换器可以单独配置为真实的输入信号,或作为一对,为I/Q输入信号。下图显示了第1代/第2代和第3代双RF-ADC片的概述。

Dual RF-ADC Tile Overview (Gen 1/Gen 2)

Dual RF-ADC Tile Overview (Gen 1/Gen 2)

RF-ADC特性

配置

每片上有四个或两个RF-ADC和一个锁相环

第1代/第2代:12位RF-ADC分辨率,具有16位数字信号处理数据通路;每个12位数据流在传递到DDC块之前,在RF-ADC核心的输出处与16位样本msb对齐。

第3代:14位RF-ADC分辨率,具有16位数字信号处理数据通路;每个14位数据流在传递到DDC块之前,在RF-ADC核心的输出处与16位样本msb对齐。

实现为四个通道(Quad)或两个通道(Dual)(采样率是依赖于设备;

抽选过滤器

第1代/第2代:1x(旁路滤波器),2x, 4x, 8x

第3代:1x(旁路滤波器),2x, 3x, 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x, 24x, 40x

奈奎斯特带宽80%,阻带衰减89 dB

数字复杂混频器

全复杂混频器支持RF-ADC的真实或I/Q输入

每个RF-ADC的48位数控振荡器(NCO)

固定Fs/ 4、Fs/2低频混频模式,其中Fs为采样频率

支持I/Q和真实输入信号

单/多波段的灵活性

2X band 对一个RF-ADC

2X band 对一个 Quad RF-ADC

支持真实输入和I/Q输入

可以通过旁路方式访问RF-ADC的全带宽

输入信号幅度阈值:每个RF-ADC有两个可编程阈值标志

内置数字校正外部模拟正交调制器:(支持一个I/Q输入对(两个rf - adc)的增益,相位和偏移校正)

多通道同步的SYSREF输入信号

灵活的AXI4-Stream接口支持广泛的可编程逻辑时钟速率和转换器采样速率

每片电流模式逻辑(CML)时钟输入缓冲器与片上校准100Ω终端;提供RF-ADC采样时钟或为片上锁相环提供参考时钟。

专用高速,高性能,差分输入缓冲器每个RF-ADC与片上校准100Ω终端(片上终端)。

直流耦合RF-ADC输入输出共模参考电压

第3代:数字阶跃衰减器(DSA)、时分双工(TDD)应用中的省电模式、在时分双工(TDD)应用中,RX和观测信道的不同抽取因子和FIFO数据速率。

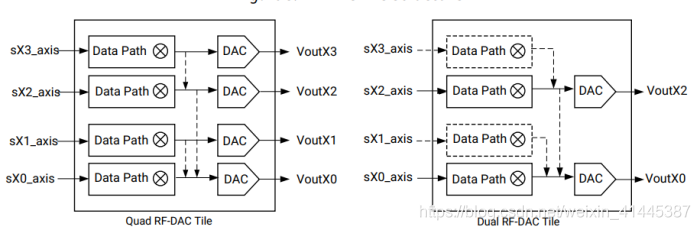

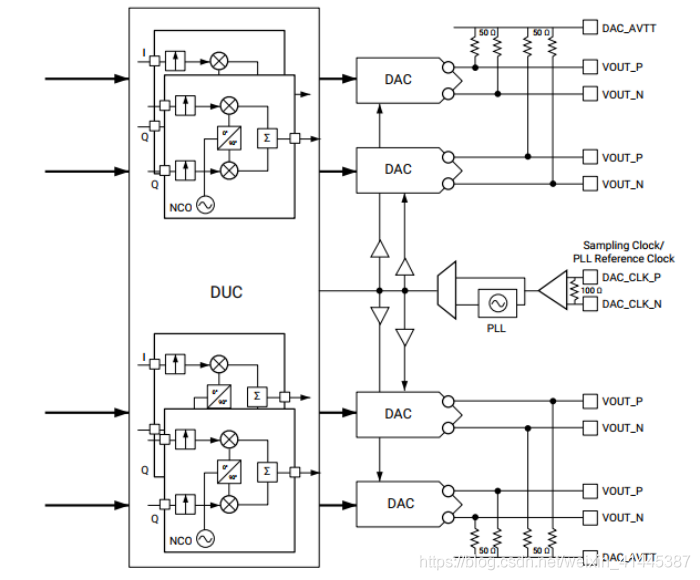

RF-DAC

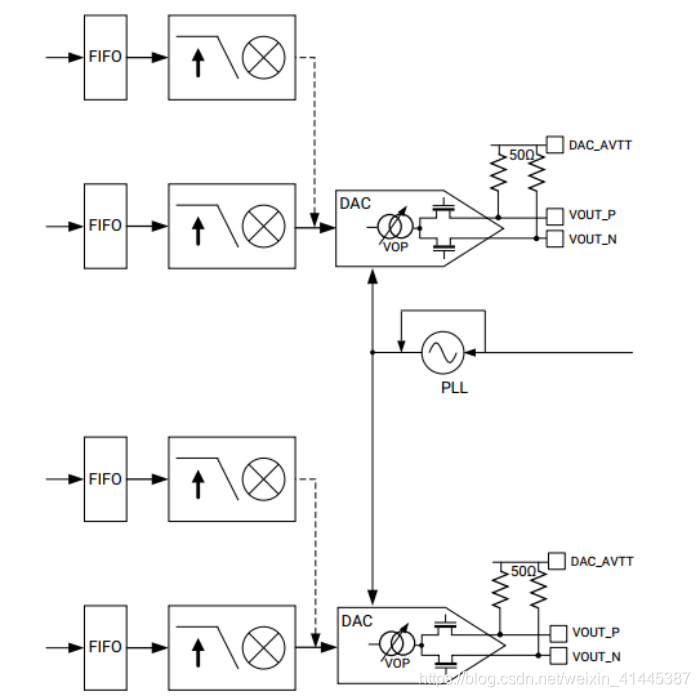

在第1代/第2代设备中,每个RF-DAC片由4个RF-DAC组成,可单独配置用于实际输出信号,或作为一对,用于I/Q输出信号生成。在第3代设备中,每个RF-DAC片由两个或四个可以类似配置的RF-DAC组成。每个RF-DAC以一个数据速率运行。RF-DAC块有一个锁相环和一个时钟实例。下面的图显示了第1代/第2代和第3代RF-DAC片的概述。

RF-DAC Overview (Gen 1/Gen 2)

Quad RF-DAC Overview (Gen 3)

Dual RF-DAC Overview (Gen 3)

RF-DAC特性

配置

第1代/第2代:每片有四个RF-DAC和一个锁相环

第3代:每片有4或2个RF-DAC和一个锁相环

14位RF-DAC分辨率,16位数字信号处理路径;数据是msb对齐到16位。

设备相关的采样速度;

插值

第1代/第2代:1x(旁路滤波器),2x, 4x, 8x

第3代:1x(旁路滤波器),2x, 3x, 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x, 24x, 40x;在IMR模式下有一个额外的2x

80%通频带,89db阻频带衰减

数字复杂混频器

全复杂混频器支持真实或I/Q输出信号到RF-DAC

一个RF-DAC对应48位NCO

固定Fs/ 4、Fs/2低功耗混频模式

支持混合模式RF-DAC功能,使第二个尼奎斯特带的RF-DAC功率最大化

单/多波段的灵活性

2X band 对一个RF-DAC

2X band 对一个 Quad RF-DAC

支持真实输入和I/Q输入

旁路模式下的全奈奎斯特带宽

外部模拟正交调制器的数字校正:支持一个I/Q输出对(2个RF-DAC)的增益、相位和偏移校正。

第1/第2代:第一奈奎斯特区Sinc校正

第3代:第一和第二奈奎斯特区Sinc校正

外部输入信号(SYSREF)用于数据转换通道的多通道同步

每片电流模式逻辑(CML)时钟输入缓冲器与片上校准100Ω终端;提供RF-DAC采样时钟或为片上锁相环提供参考时钟(不适用于奇数双RF-DAC only片)

第1代/第2代:支持20ma或32ma输出功率模式

可变输出功率(VOP)支持全尺寸电流接收器,向下兼容Gen 1和Gen 2d 20/32 mA模式

第3代:时分双工(TDD)应用中单个功能块的节能模式

IP相关说明

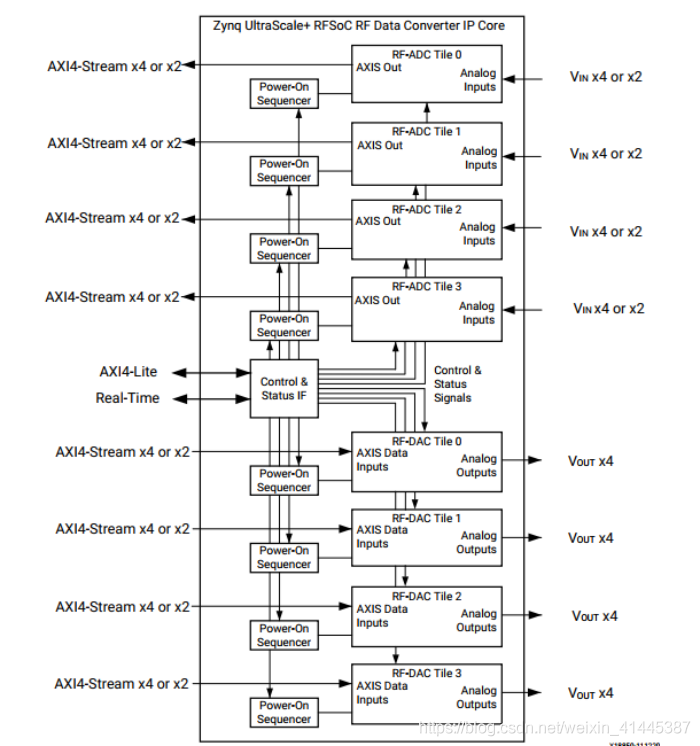

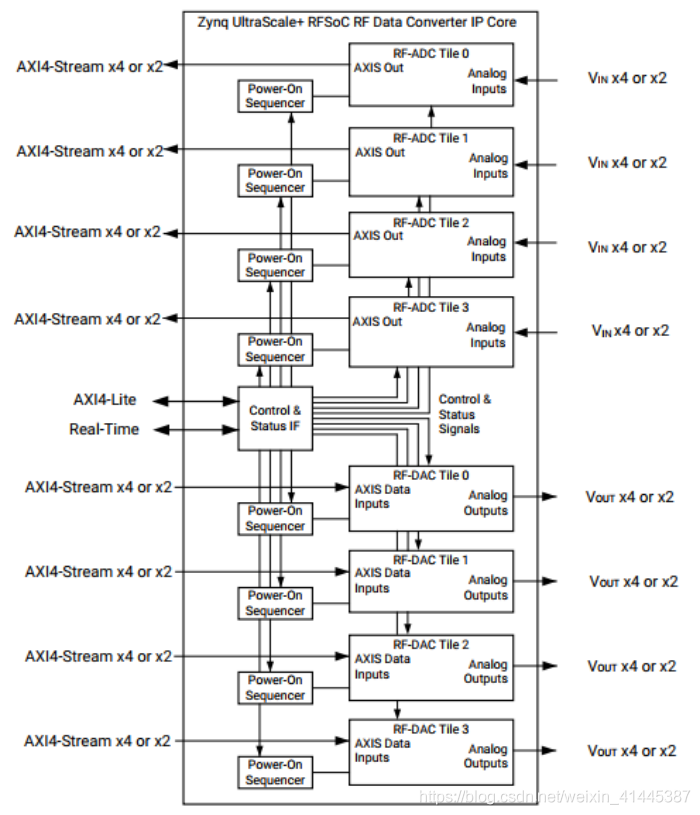

Zynq UItraScale+ RFSoC射频数据转换器IP核提供了一种实例化IP集分器Zynq UItraScale+ RFSoC中所有RF- DAC和RF- ADC块的方法。一个IP核实例允许访问设备中的所有转换器。该IP确保所有启用的块都被上电,并且未使用的转换器被禁用。

IP框图

IP Core Overview (Gen 1/Gen 2):

IP Core Overview (Gen 3) :

一个RF-ADC块有两个或四个RF-ADC。对于Gen 1/Gen 2设备,一个RF-DAC块有四个RF-ADC;对于第3代设备,一个RF-DAC块可以有两个或四个RF-DAC。转换器的数量和最大采样率取决于设备和包装。每个片中的转换器都是相同类型的。

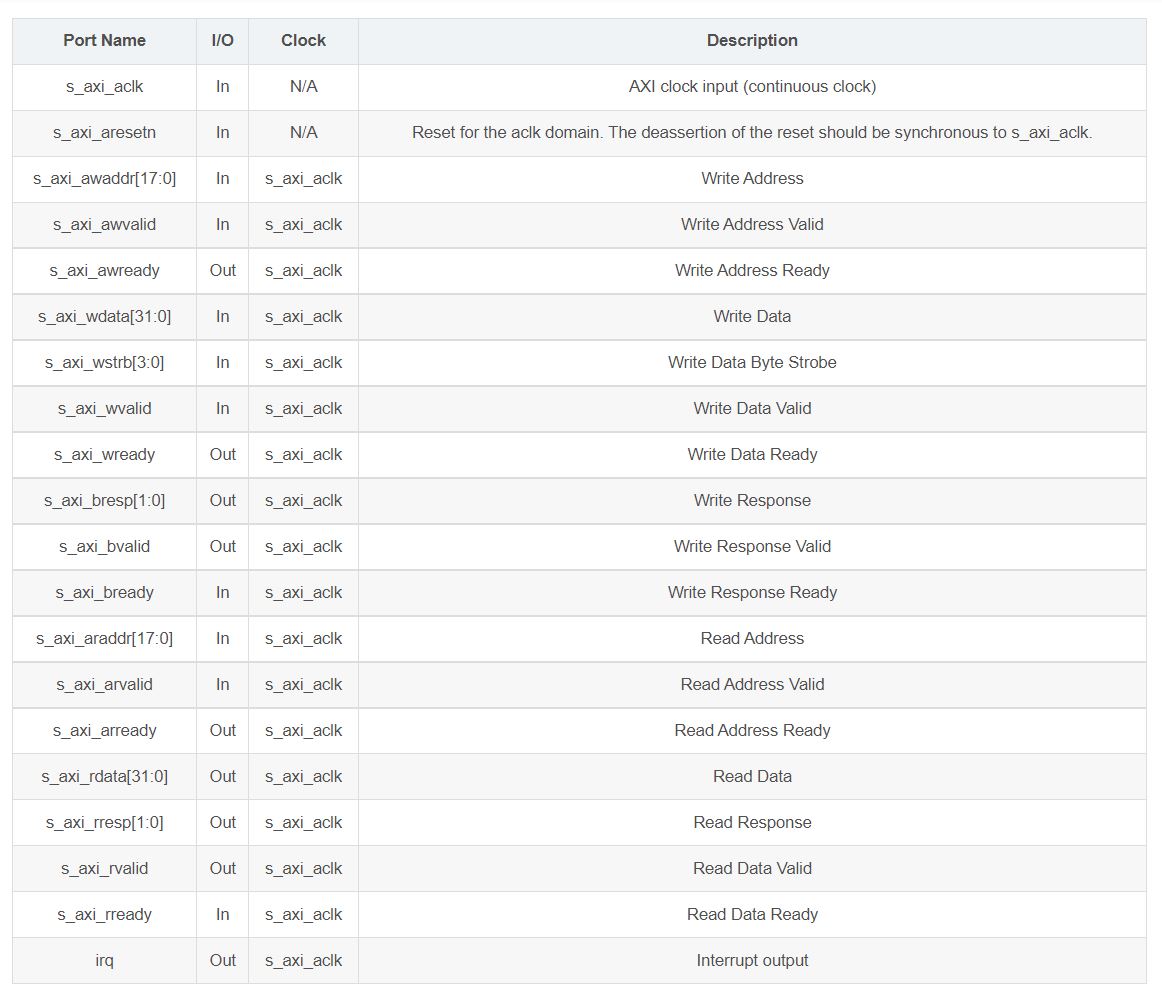

公用端口

配置接口端口

通过AXI-S进行IP的配置,支持中断输出。

通过AXI-S进行IP的配置,支持中断输出。

Multi-Tile同步端口

RF-DAC端口

RF-DAC片通用时钟端口

dacX_clk_p,dacX_clk_n:RF-DAC片上锁相环参考时钟或采样时钟输入。

dacX_clk_p,dacX_clk_n:RF-DAC片上锁相环参考时钟或采样时钟输入。

clk_dacX:输出时钟到用户逻辑。

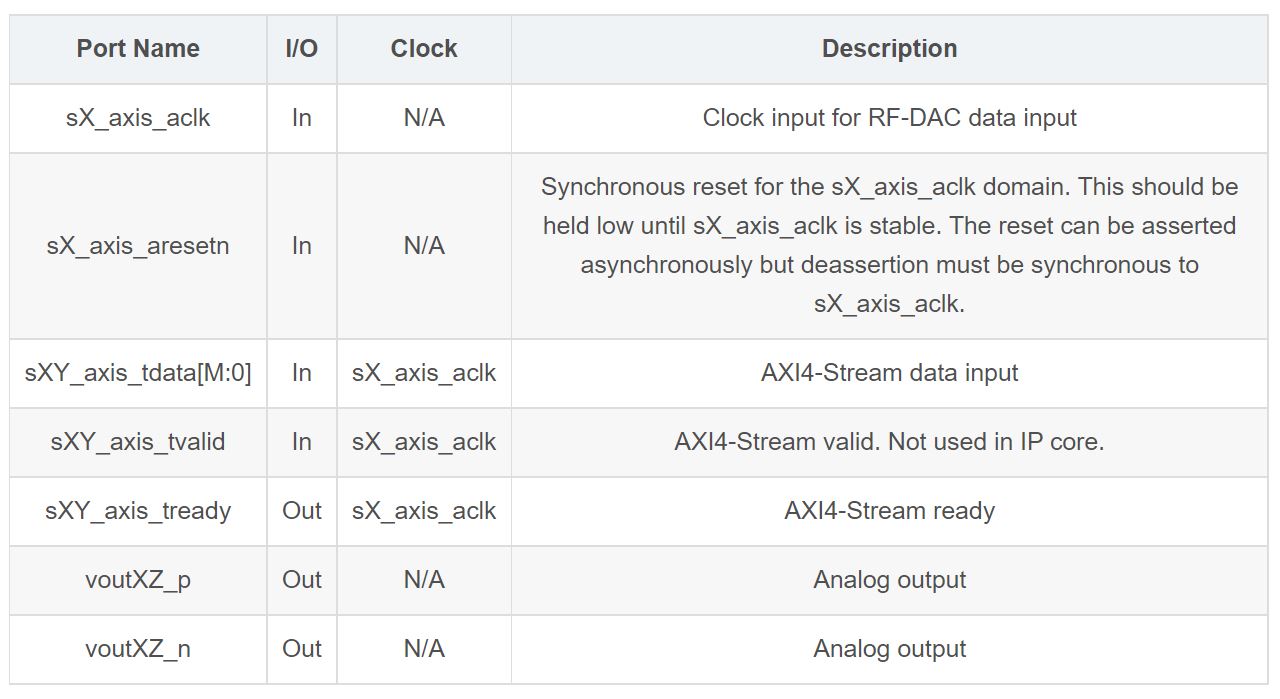

RF-DAC的AXI4 流相关端口

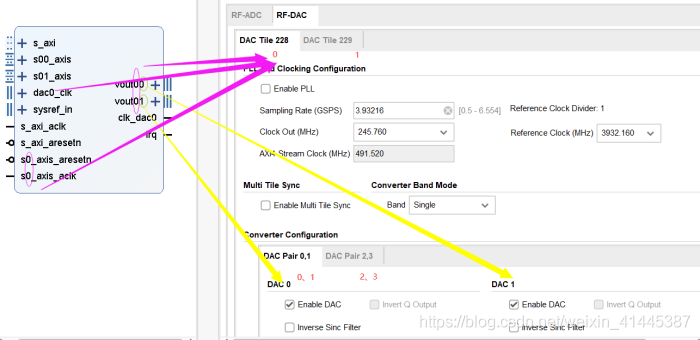

X代表对应的tile,这里的DAC有两个片,用 0,1标识。Y代表这个片的第几个DAC。Z指的是RF-DAC在片中的位置(0到3)。M是XY转换器每个AXI4-Stream(字* 16)的样本数量。示例如下图所示:

X代表对应的tile,这里的DAC有两个片,用 0,1标识。Y代表这个片的第几个DAC。Z指的是RF-DAC在片中的位置(0到3)。M是XY转换器每个AXI4-Stream(字* 16)的样本数量。示例如下图所示:

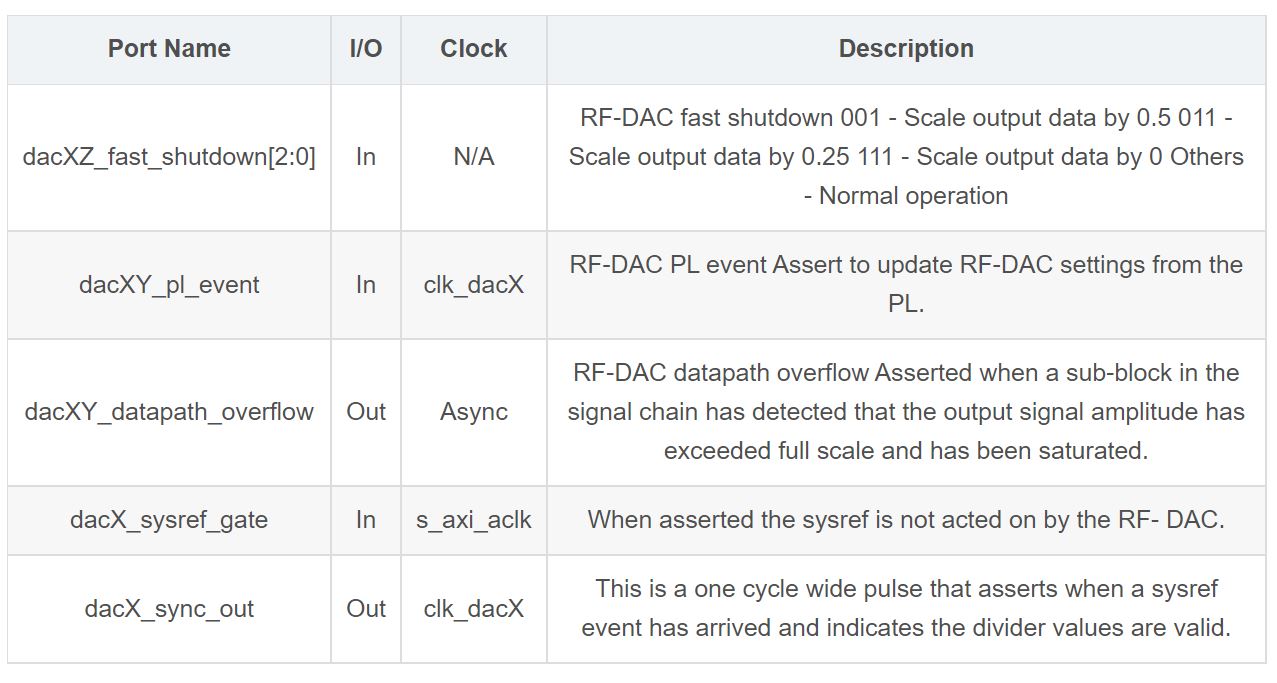

RF-DAC的实时信号接口

X代表对应的tile,这里的DAC有两个片,用 0,1标识。Y代表这个片的第几个DAC。Z指的是RF-DAC在片中的位置(0到3)。

dacXZ_fast_shutdown[2:0]:RF-DAC快速关闭,输入为001按 0.5 缩放输出数据,输入为011按 0.25 缩放输出数据,输入为111按 0 缩放输出数据,其他为正常工作。

dacXY_pl_event: 输入拉高时,从 PL 更新 RF-DAC 设置。

dacXY_datapath_overflow:数据路径溢出,当信号链中的一个子块检测到输出信号幅度已超过满量程并已饱和时进行拉高。

dacX_sysref_gate:当拉高时,sysref 对RF-DAC不起作用。

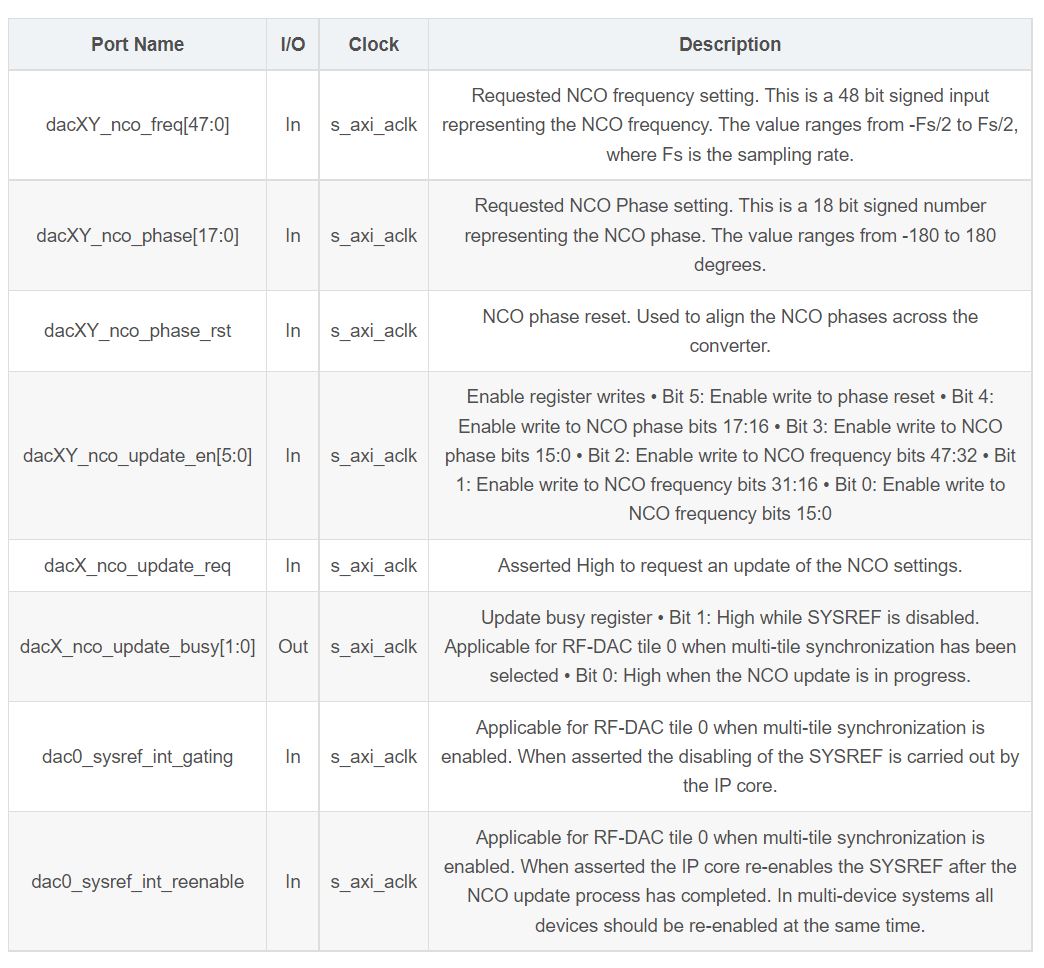

RF-DAC的Real-Time NCO信号接口(数字振荡器)

dacXY_nco_freq[47:0]:请求NCO频率设置。这是一个48位带符号的输入,表示NCO频率。取值范围为-Fs/2 ~ Fs/2,其中Fs为采样率。

dacXY_nco_phase[17:0]: 请求的NCO相位设置。这是一个18位有符号的数字,表示NCO相位。取值范围为-180 ~ 180°。

dacXY_nco_phase_rst: NCO相位复位。用于调整整个变换器的NCO相位。

dacXY_nco_update_en[5:0]: 使能寄存器写入

Bit 5: 使能写入相位复位

Bit 4: 使能写入NCO相位控制位的17:16

Bit 3: 使能写入NCO相位控制位的15:0

Bit 2: 使能写入NCO频率控制位的47:32

Bit 1: 使能写入NCO频率控制位的31:16

Bit 0: 使能写入NCO频率控制位的15:0

dacX_nco_update_req: 拉高请求更新NCO设置位。

dacX_nco_update_busy[1:0]: 更新busy寄存器

1位:当该为高时,而SYSREF被禁用。当选择了多片同步时,适用于RF-DAC片0

0位:当该为高时,NCO进行更新。

dac0_sysref_int_gating: 当启用多片同步时,适用于RF-DAC第0片。当拉高时,SYSREF的禁用是由IP核执行的。

dac0_sysref_int_reenable: 当启用多片同步时,适用于RF-DAC第0片。当拉高时,IP核在NCO更新过程完成后重新启用SYSREF。在多设备系统中,所有设备应该同时重新启用。

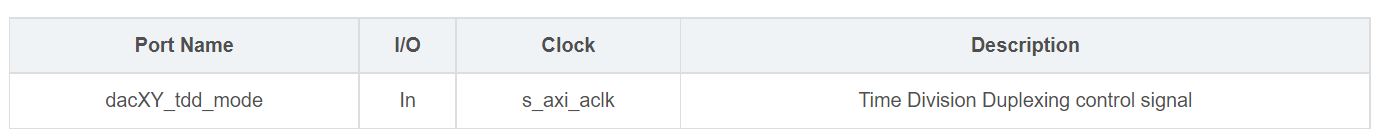

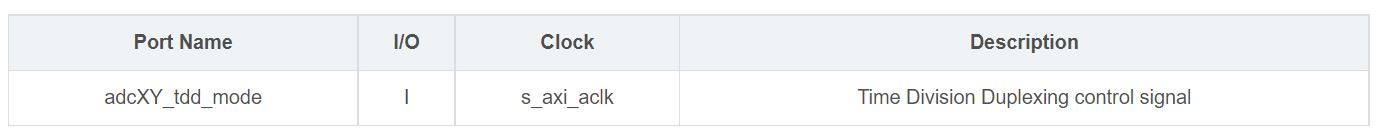

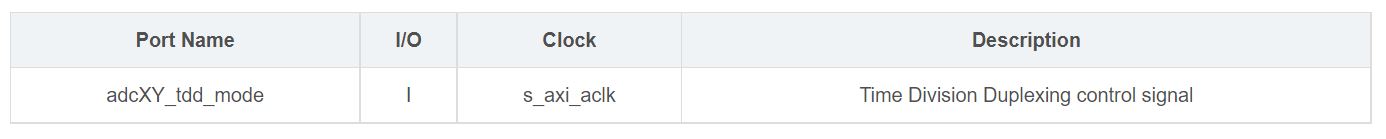

RF-DAC的实时TDD信号接口(时分复用)

dacXY_tdd_mode: 时分双工控制信号。该部分只有第三代才有。

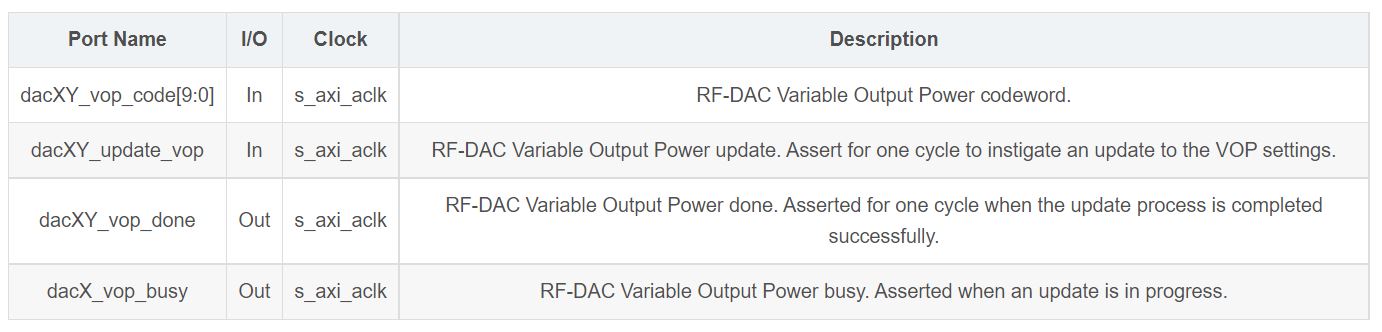

RF-DAC的实时VOP信号接口(可变输出功率)

该部分只有第三代才有。

该部分只有第三代才有。

dacXY_vop_code[9:0]: RF-DAC可变输出功率码字。

dacXY_update_vop: RF-DAC可变输出功率更新。拉高一个周期,以启动对VOP设置的更新。

dacXY_vop_done: RF-DAC可变输出功率完成。当更新过程成功完成时拉高一个周期。

dacX_vop_busy: RF-DAC可变输出功率忙。在进行更新时拉高。

RF-ADC端口

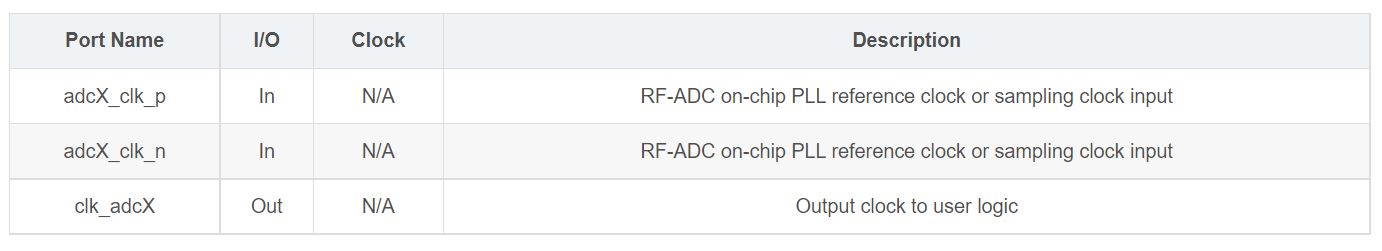

RF-ADC片通用的时钟端口

X表示RF-ADC片的位置。

X表示RF-ADC片的位置。

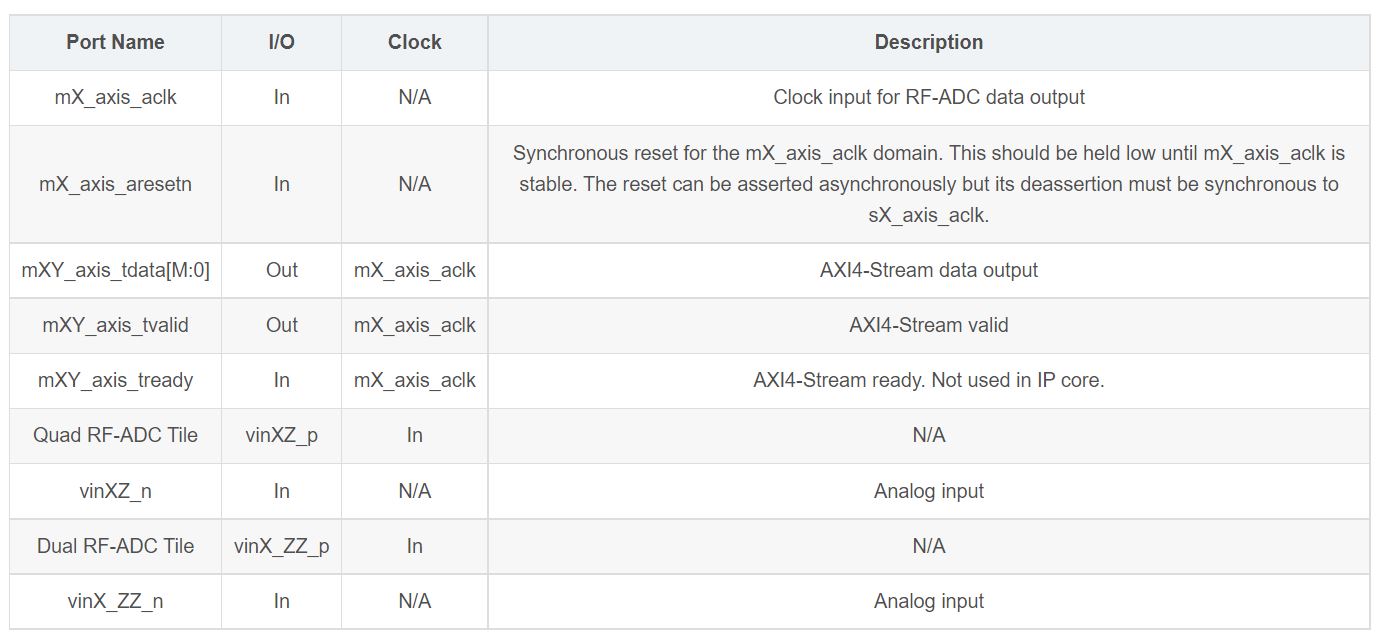

RF-ADC的AXI4 流相关端口

X是指转换器所在的片的位置。Y是指DDC块在片中的位置(0到3)。

X是指转换器所在的片的位置。Y是指DDC块在片中的位置(0到3)。

在Quad RF-ADC片设备中,Z指的是RF-ADC在片中的位置(0到3)。在双RF-ADC片设备中,ZZ要么是01(瓦片中的较低RF-ADC),要么是23(瓦片中的较高RF-ADC)。如下图:

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-2yph5qMZ-1628679889198)(C:/Users/Administrator/Pictures/md_img/image-20210810155833798.png)]

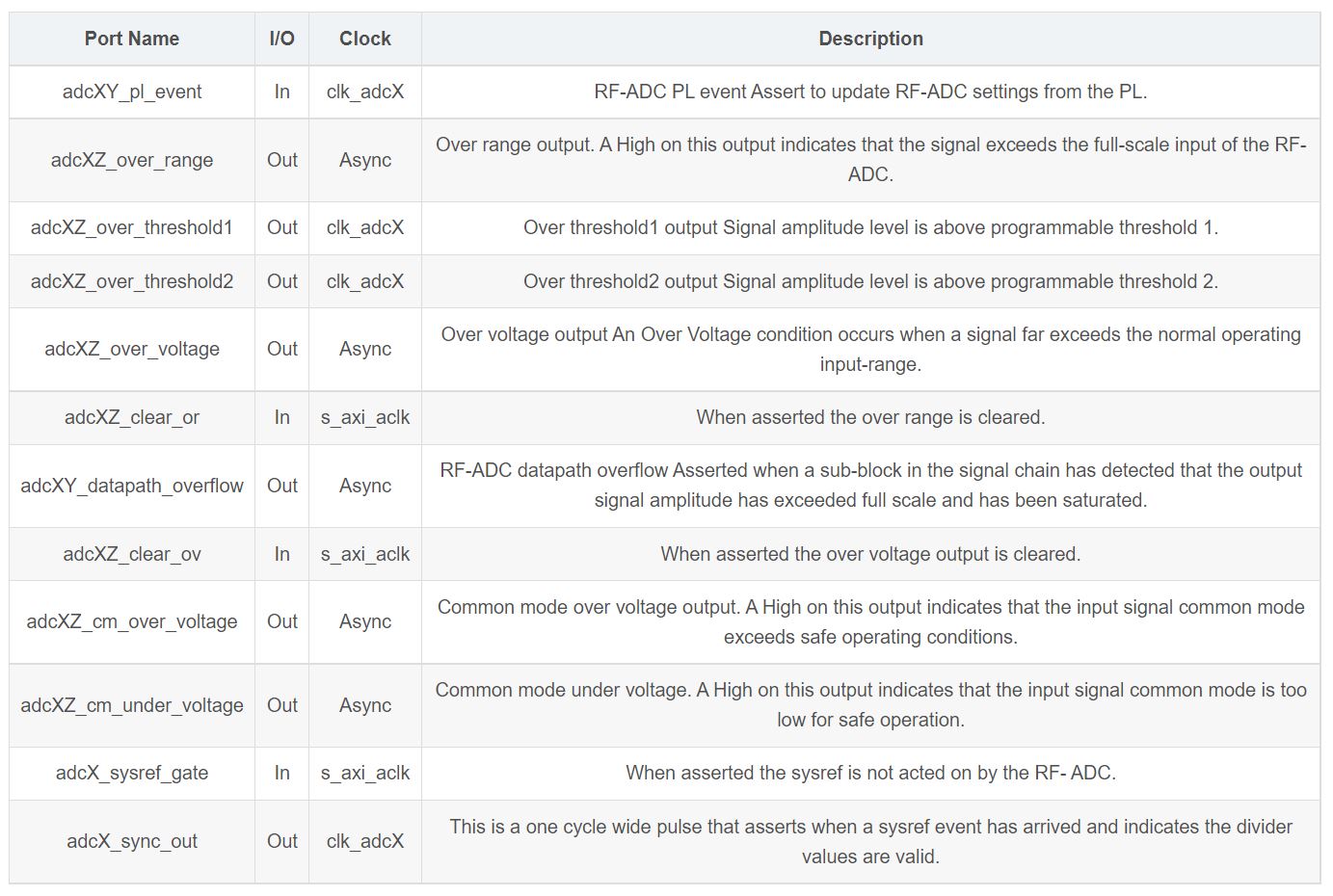

四倍频RF-ADC的实时信号接口

该部分只在第三代有。

该部分只在第三代有。

adcXY_pl_event: RF-ADC PL事件。拉高时从PL更新RF-ADC设置。

adcXZ_over_range: 表示超过输出范围。在这个输出上的高表示信号超过了全量程的输入RF-ADC。

adcXZ_over_threshold1: 输出超过threshold1阈值。拉高时表示信号振幅电平高于可编程阈值1。

adcXZ_over_threshold2: 输出超过threshold2阈值。拉高时表示信号振幅电平高于可编程阈值2。

adcXZ_over_voltage: 输出电压超过范围,当信号远远超出正常工作输入范围时,就会出现过电压情况。此时会拉高。

adcXZ_clear_or: 当拉高时,超出的范围被清除。

adcXY_datapath_overflow: ADC数据溢出,当信号链中的一个子块检测到输出信号幅度已超过满量程并已饱和时该信号拉高。

adcXZ_clear_ov: 当拉高时,过电压输出被清除。

adcXZ_cm_over_voltage: 共模过电压输出。该输出上的高电平表示输入信号共模超过了安全运行条件。

adcXZ_cm_under_voltage: 共模欠压。该输出上的高电平表示输入信号共模过低,不利于安全操作。

adcX_sysref_gate: 当拉高时,sysref对RF- ADC没有作用。

adcX_sync_out: 这是一个周期宽的脉冲,它用于指示sysref事件何时到达,并指示分隔符值是否有效。

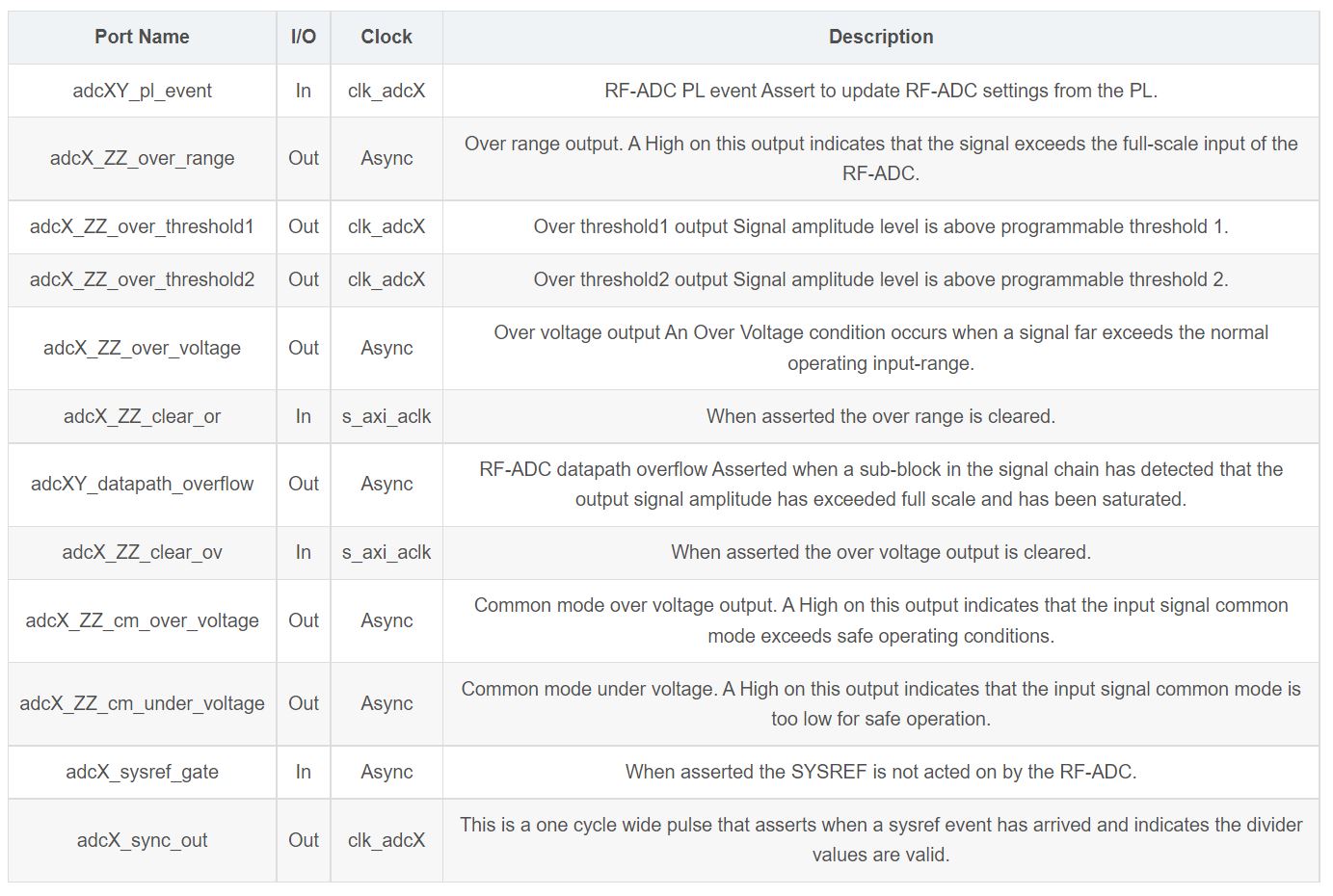

二倍频RF-ADC的实时信号接口

同上面四倍频RF-ADC的实时信号接口,该部分也只有第三代才有。仅名字不同,用于区分。

同上面四倍频RF-ADC的实时信号接口,该部分也只有第三代才有。仅名字不同,用于区分。

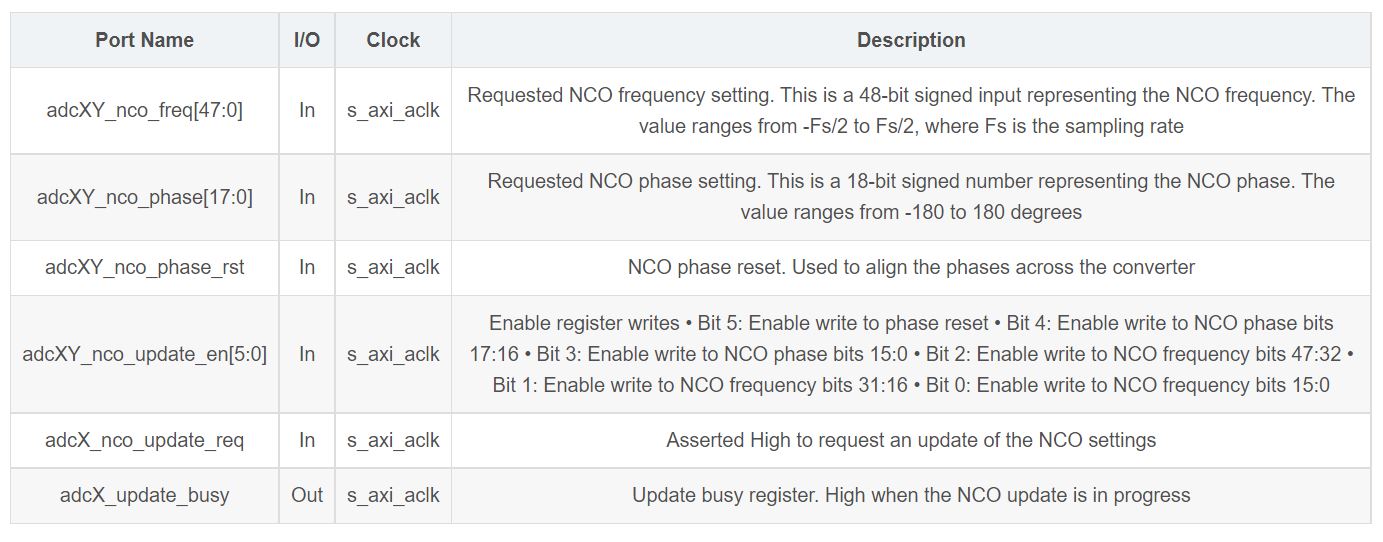

四倍频RF-ADC实时NCO信号接口

adcXY_nco_freq[47:0]: 请求NCO频率设置。这是一个48位的带符号输入,表示NCO频率。取值范围为-Fs/2 ~ Fs/2,其中Fs为采样率。

adcXY_nco_phase[17:0]: 请求NCO相位设置。这是一个18位有符号的数字,表示NCO相位。取值范围为-180° ~ 180°

adcXY_nco_phase_rst: NCO相位复位。用于调整整个变换器的NCO相位。

adcXY_nco_update_en[5:0]: 使能寄存器写入

Bit 5: 使能写入相位复位

Bit 4: 使能写入NCO相位控制位的17:16

Bit 3: 使能写入NCO相位控制位的15:0

Bit 2: 使能写入NCO频率控制位的47:32

Bit 1: 使能写入NCO频率控制位的31:16

Bit 0: 使能写入NCO频率控制位的15:0

adcX_nco_update_req: 拉高时请求更新NCO设置位。

adcX_update_busy: 更新busy寄存器,当NCO更新正在进行时,该位为高。

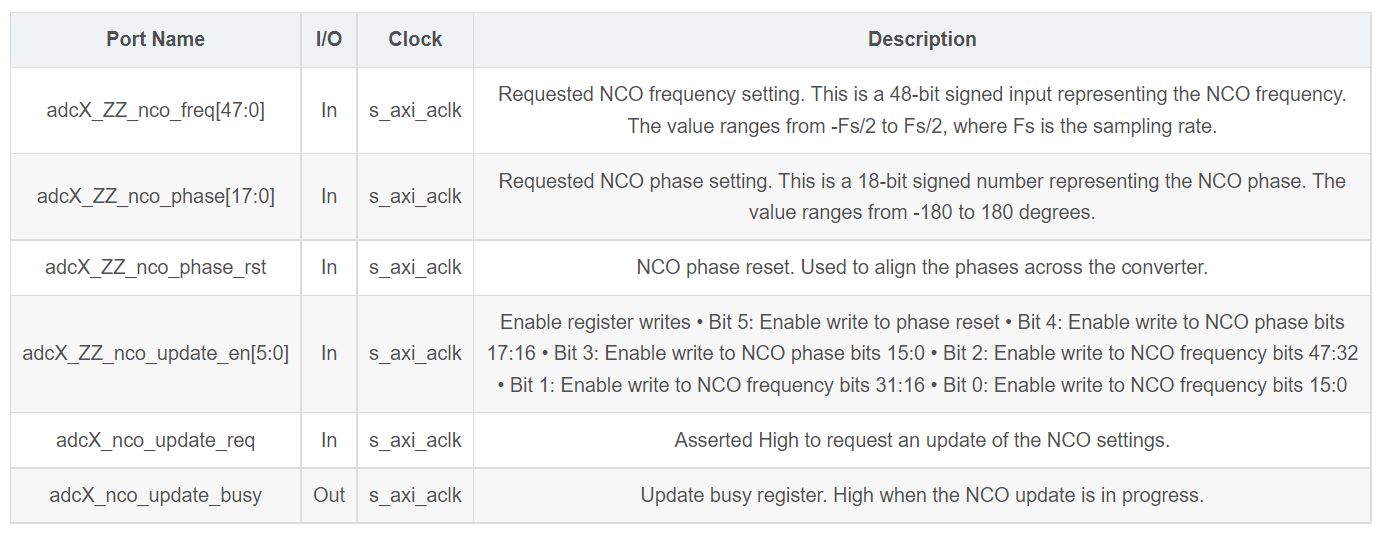

二倍频RF-ADC实时NCO信号接口

同上面四倍频RF-ADC实时NCO信号接口。仅名字不同,用于区分。

同上面四倍频RF-ADC实时NCO信号接口。仅名字不同,用于区分。

四倍频RF-ADC的实时TDD信号接口

adcXY_tdd_mode : 时分双工控制信号。只有gen 3 才有。

二倍频RF-ADC的实时TDD信号接口

每个AXI4-Stream接口都增加了一个TDD信号接口。 当 I/Q 数据输出时,每个 RF-ADC 都有两个接口。 在这种情况下,adcXY_tdd_mode 输入应连接在一起。

每个AXI4-Stream接口都增加了一个TDD信号接口。 当 I/Q 数据输出时,每个 RF-ADC 都有两个接口。 在这种情况下,adcXY_tdd_mode 输入应连接在一起。

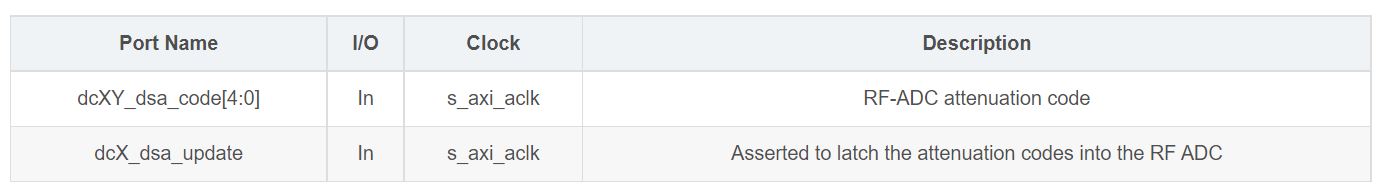

四倍频RF-ADC的实时DSA信号接口

dcXY_dsa_code[4:0] : 衰减控制字。

dcXY_dsa_code[4:0] : 衰减控制字。

dcX_dsa_update : 拉高时将衰减码锁存到射频ADC中。

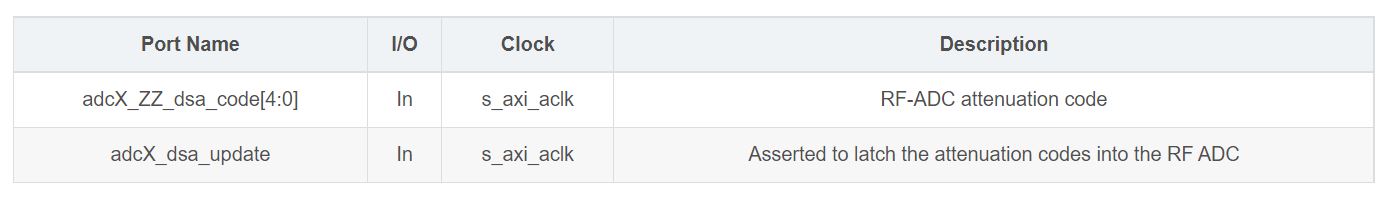

二倍频RF-ADC的实时DSA信号接口

同上,四倍频RF-ADC的实时DSA信号接口。

同上,四倍频RF-ADC的实时DSA信号接口。

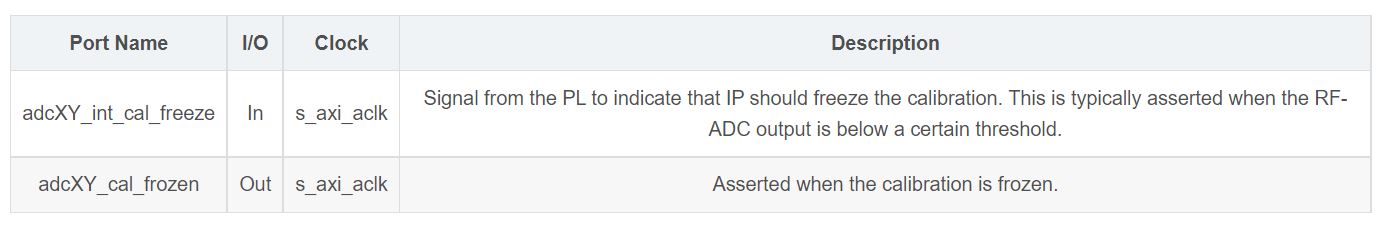

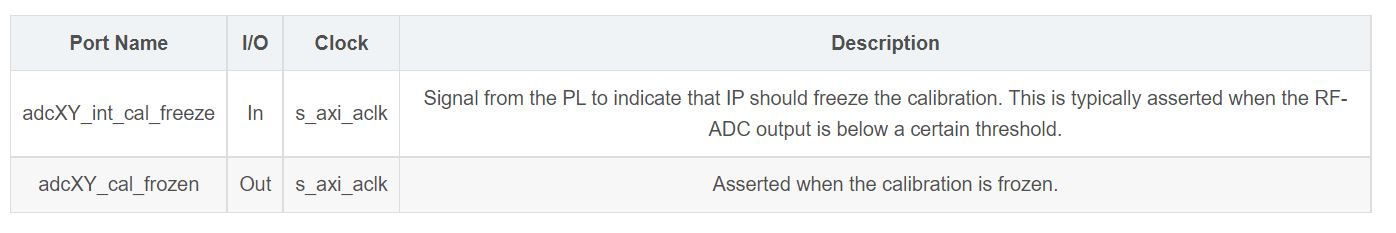

Quad RF-ADC Tiles 的校准冻结端口

adcXY_int_cal_freeze: 来自PL的信号表明IP应该冻结校准。这通常是在RF-ADC输出低于某个阈值时拉高的。

adcXY_cal_frozen: 校准冻结时拉高。

Dual RF-ADC Tiles 的校准冻结端口

同上,Quad RF-ADC Tiles 的校准冻结端口。

同上,Quad RF-ADC Tiles 的校准冻结端口。

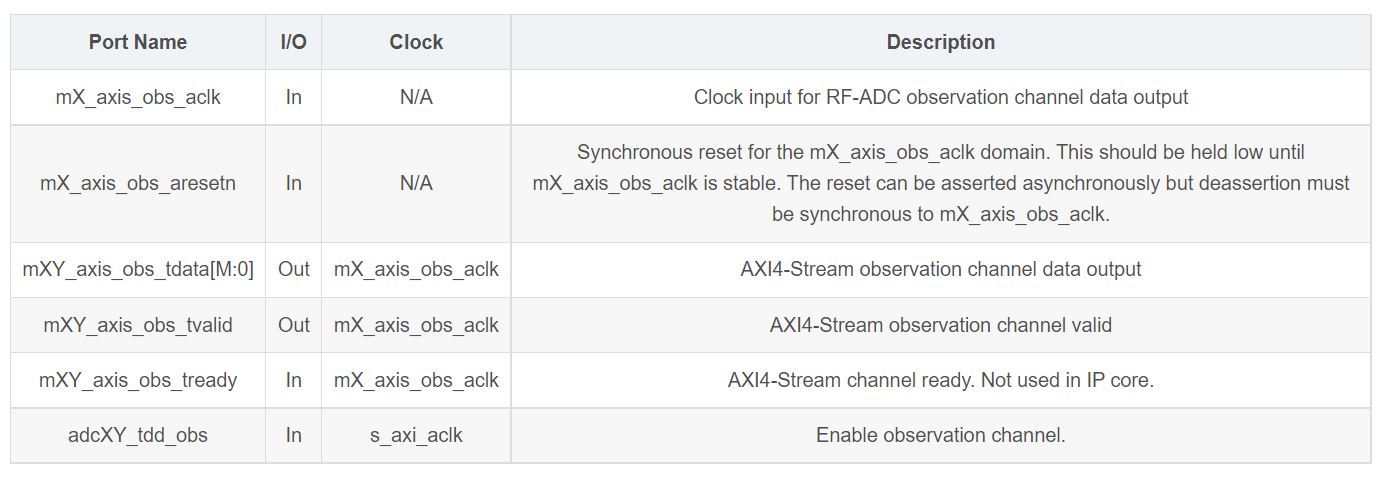

RF-ADC的流观测通道端口

mX_axis_obs_aclk : 用于 RF-ADC 观察通道数据输出的时钟输入。

mX_axis_obs_aclk : 用于 RF-ADC 观察通道数据输出的时钟输入。

mX_axis_obs_aresetn : mX_axis_obs_aclk 域的同步复位。 这应该保持低,直到 mX_axis_obs_aclk 稳定。 复位可以异步置位,但置位必须与 mX_axis_obs_aclk 同步。

mXY_axis_obs_tdata[M:0] : AXI4-Stream观测通道数据输出

mXY_axis_obs_tvalid : AXI4-Stream 观测通道有效

mXY_axis_obs_tready : AXI4-Stream 通道准备就绪。 未在 IP 核中使用。

adcXY_tdd_obs: 使能观察通道。

references

PG269 Zynq UltraScale+ RFSoC RF Data Converter