本文转载自: 硬码农二毛哥微信公众号

FIFO是FPGA设计中最常用的IP,读写时序相对简单,可能正是因为这个原因,通常不会去细读FIFO手册,具体怎么操作大概清楚,上手就写,一般不会出什么问题。最近却遇到读FIFO异常的情况,特意记录一下,顺便细读了一下PG057。

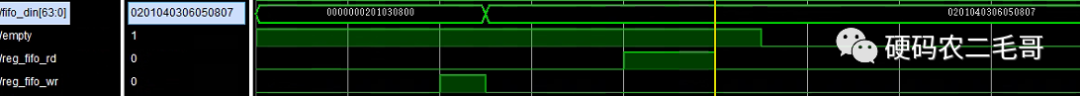

FIFO读操作异常

数据写入FIFO后,读取数据,没有输出。

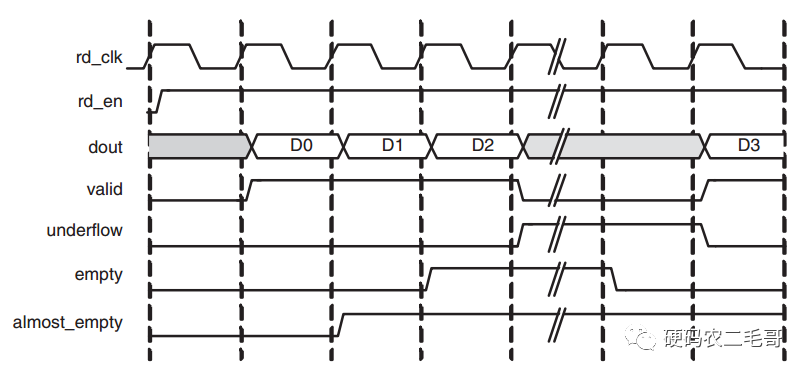

FIFO 读时序

下图是pg057读时序图,在文档中读到这样一句话:

shows a standard read access. When you write at least one word into the FIFO,empty is deasserted — indicating that the data is available to be read。

当FIFO中的empyt信号为0时,才可以读FIFO。

为什么原来不出这种错误呢

仔细观察抓到的时序图发现,从写使能有效到empty由高变低经历了几个时钟周期,之前使用FIFO时,empty应该是在写使能下一个周期就置低了。差异就在于以前FIFO读写都是8bit数据,这次是64bit数据。应该是输入位宽导致empty的变化。

读写位宽不同时

FIFO输入为64bit,输出为32bit。

当向FIFO写入64‘h090a0b0c0d0e0f10时,从输出端先读出32’h090a0b0c,后读出32‘h0d0e0f10。

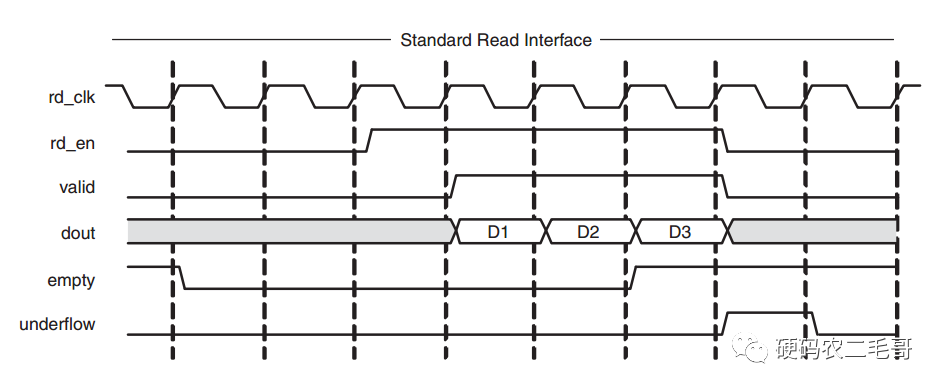

使用valid信号

valid不是必须使用信号,但该信号指示读出数据有效状态,非常有用。

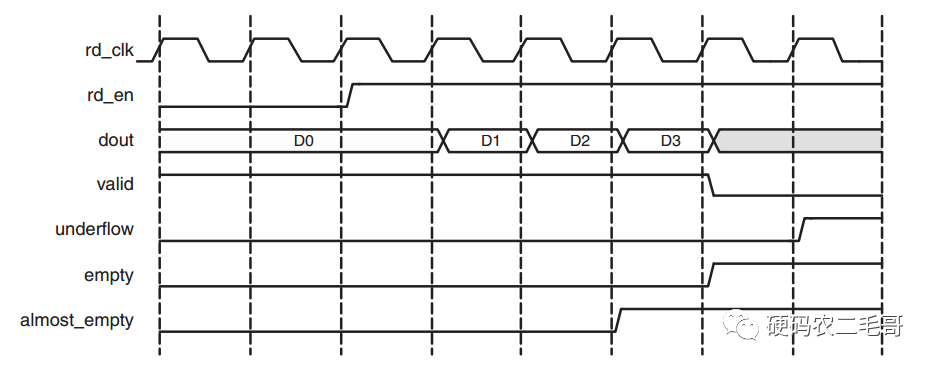

First-Word Fall-Through与Show-ahead

在读使能信号有效之前,FIFO输出数据,这个功能在Xilinx叫First-Word Fall-Through,Intel叫Show-ahead。功能类似,在使用First-Word Fall-Through时,valid信号不再能准确只是输出有效。在有效情况下使用First-Word Fall-Through会更方便,但我有时更愿意麻烦点,使用标准FIFO,因为遇到做器件移植的情况,要移植的器件不支持这种模式,需要修改时序。

Underflow 与Overflow

Underflow

Underflow用来指示读操作不成功,当FIFO为空时,进行读操作,该信号触发。

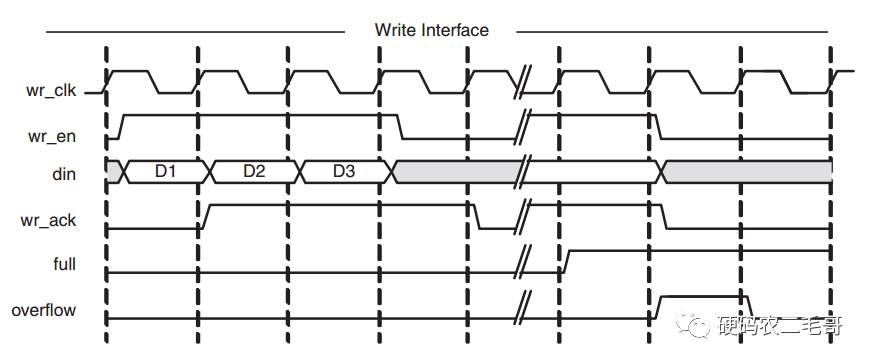

Overflow

Overflow用来指示写操作不成功,当FIFO为满时,进行写操作,该信号触发。

FIFO实现

Intel FPGA的FIFO通常由两种资源实现,Block RAM和 Distributed RAM。Xilinx有如下四种资源实现。