设计收敛技巧:正确使用功耗估算

judy 在 周三, 04/14/2021 - 09:32 提交

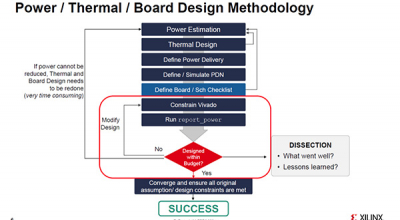

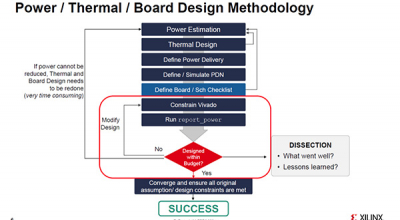

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。

首先,我们要知道的是,Hold Time违例,是因为时钟绕的太远,到达时间太晚。而且综合之后给出的时序报告都是估计值,因此综合之后可以不考虑Hold Time,只考虑Setup Time;即便此时Hold Time违例,我们也不需要去理会

在前面的章节中,我们用了很多Tcl的指令,但有些指令并没有把所有的参数多列出来解释,这一节,我们就把约束中的Tcl指令详细讲一下。

本次系列研讨会将由赛灵思战略应用高级工程师 Lauren Gao(高亚军)带领大家从基础到进阶,一站式领略 Vivado 这款神奇的开发工具。

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

对于延迟约束,相信很多同学是不怎么用的,主要可能就是不熟悉这个约束,也有的是嫌麻烦,因为有时还要计算PCB上的走线延迟导致的时间差。而且不加延迟约束,Vivado也只是在Timing Report中提示warning,并不会导致时序错误,这也会让很多同学误以为这个约束可有可无。

多周期路径,我们一般按照4个步骤来约束:有使能的数据;两个有数据交互的时钟之间存在相位差;存在快时钟到慢时钟的路径;存在慢时钟到快时钟的路径。

在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径。