FPGA时序约束理论篇之IO约束

demi 在 周三, 02/05/2020 - 11:41 提交

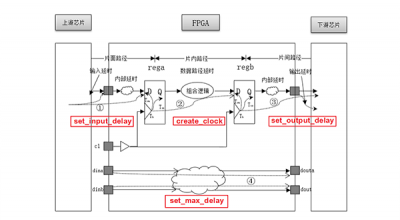

I/O约束是必须要用的约束,又包括管脚约束和延迟约束。管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值,前者指定了管脚的位置,后者指定了管脚对应的电平标准。

I/O约束是必须要用的约束,又包括管脚约束和延迟约束。管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值,前者指定了管脚的位置,后者指定了管脚对应的电平标准。

在前面的章节中,我们用了很多Tcl的指令,但有些指令并没有把所有的参数多列出来解释,这一节,我们就把约束中的Tcl指令详细讲一下。

多周期路径,我们一般按照以下4个步骤来约束:带有使能的数据;两个有数据交互的时钟之间存在相位差;存在快时钟到慢时钟的路径;存在慢时钟到快时钟的路径。

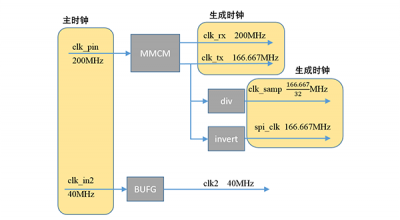

Vivado会自动设别出两个主时钟,其中clk_pin_p是200MHz,这个是直接输入到了MMCM中,因此会自动约束;另一个输入时钟clk_in2没有约束,需要我们手动进行约束。

我们以Vivado自带的wave_gen工程为例,该工程的各个模块功能较为明确,如下图所示。为了引入异步时钟域,我们在此程序上由增加了另一个时钟--clkin2,该时钟产生脉冲信号pulse,samp_gen中在pulse为高时才产生信号。

在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。虽然执行顺序是从前到后,但优先级却不同;就像四则运算一样,+-x÷都是按照从左到右的顺序执行,但x÷的优先级比+-要高。

默认情况下,保持时间的检查是以建立时间的检查为前提,即总是在建立时间的前一个时钟周期确定保持时间检查。

时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。