作者:Fisher Yang,来源:FPGA FAE技术分享选集

RFDC这个IP,是RFSoC系列中ADC、DAC的核心。这个IP和PL的资源有互联通道,和ARM相对是独立的。IP的手册参考AMD的PG269文档,这里描述的是常用的一些配置方法和关键要素。下文以ZCU208的工程为例,介绍RFDC IP的常用设置。

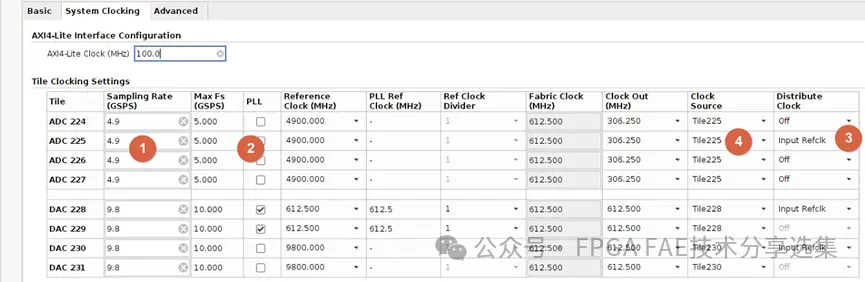

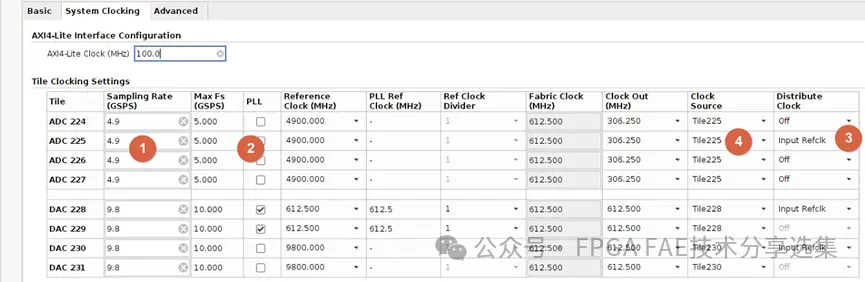

IP第一步,配置时钟在RFDC的System Clocking页面。1. 先填写需要设置的ADC和DAC的sampling rate,即采样率。

2. 这一步是关于是否使能ADC和DAC内部的PLL。如果给的是参考时钟,PLL需要勾选上;如果给的是直采时钟(例如外部用LMX2594倍频的采样时钟),那么这里PLL可以不用勾选。

3. 时钟分配方式,也就是共享给其他Tile的时钟。如果是直采时钟共享给其他Tile则选择Input Refclk;如果是内部PLL倍频后再给其他Tile,选择PLL Output。

4. 选择Clock的来源,如果有其他Tile分享时钟,则可以选择其他路的时钟。上述例子,对于ADC来说,ADC 225的时钟输入了4.9G的直采时钟,同时共享出来,ADC 224、226和227都使用ADC 225的4.9G时钟。DAC是228的时钟,分享给229。同时228和229都使能了Tile内的PLL。DAC 230则外部有PLL倍频到9.8G作为直采时钟,同时分享给DAC 231作为采样时钟。

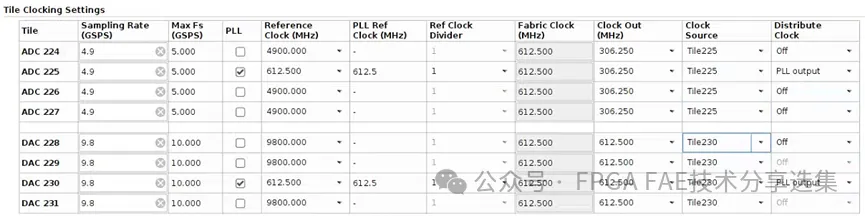

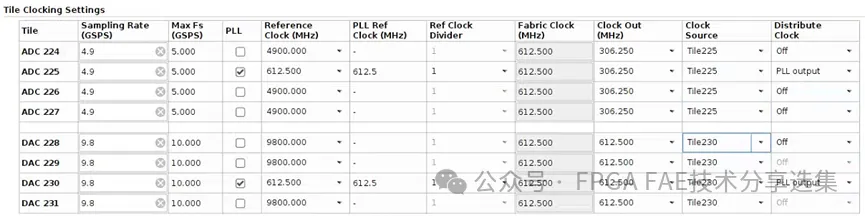

再看这个例子,ADC 225的时钟输入是参考时钟,Tile内的PLL倍频后分享出来,其他3个Tile均使用ADC 225 PLL倍频后的时钟作为采样时钟。

DAC 230输入也是参考时钟,Tile内的PLL倍频后分享出来,其他3个Tile都使用同一个时钟。

更多关于时钟的信息,参考PG269中关于RFDC的时钟介绍。

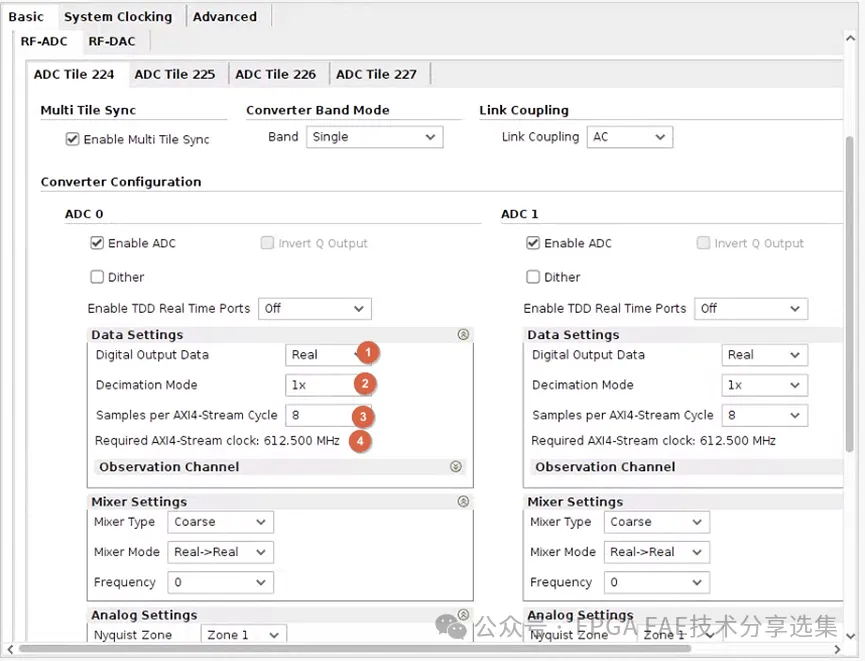

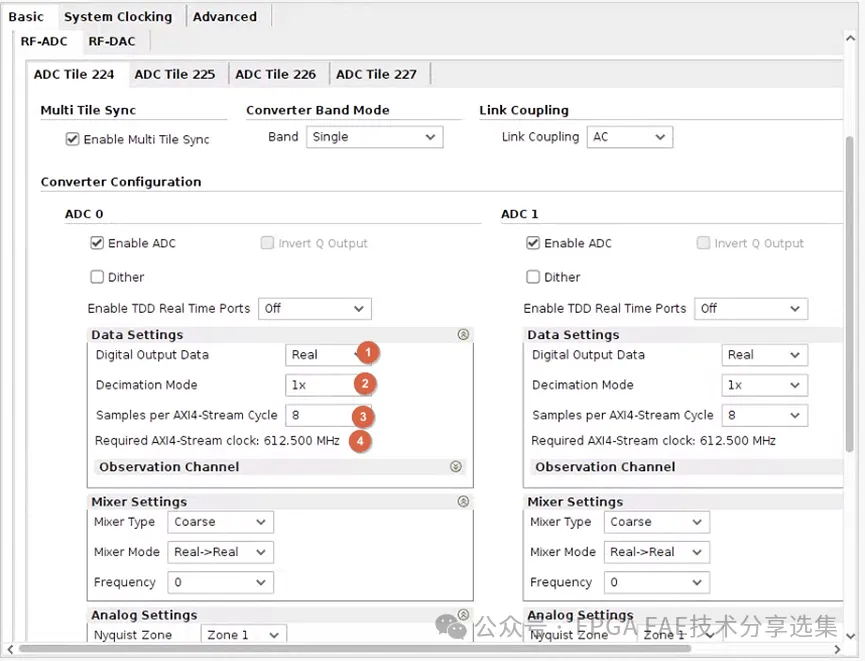

ADC的配置在Basic页面中,ZCU208一共有4个Tile,都需要对应正确的配置。1. ADC的输出,是Real模式还是IQ模式。Real模式输出实采的数据,IQ模式包括Mixer混频;2. 抽样;

3. 每个时钟出多少个samples,注意每个sample是16bit,2 bytes;

4. 对应配置下,ADC PL应该给多少频率的时钟,对应IP的mx_axis_aclk,注意外面连接的时钟必须对应这个频率;

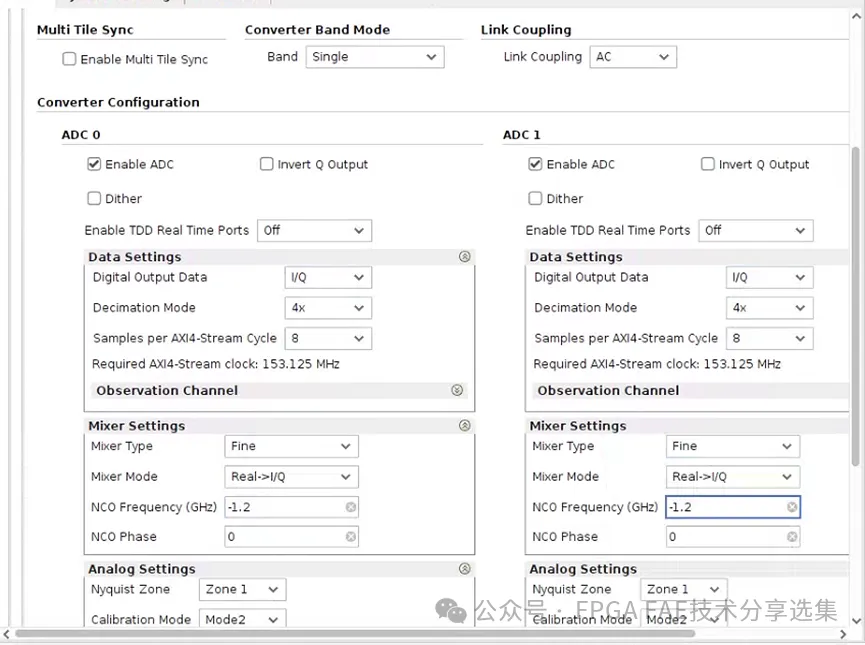

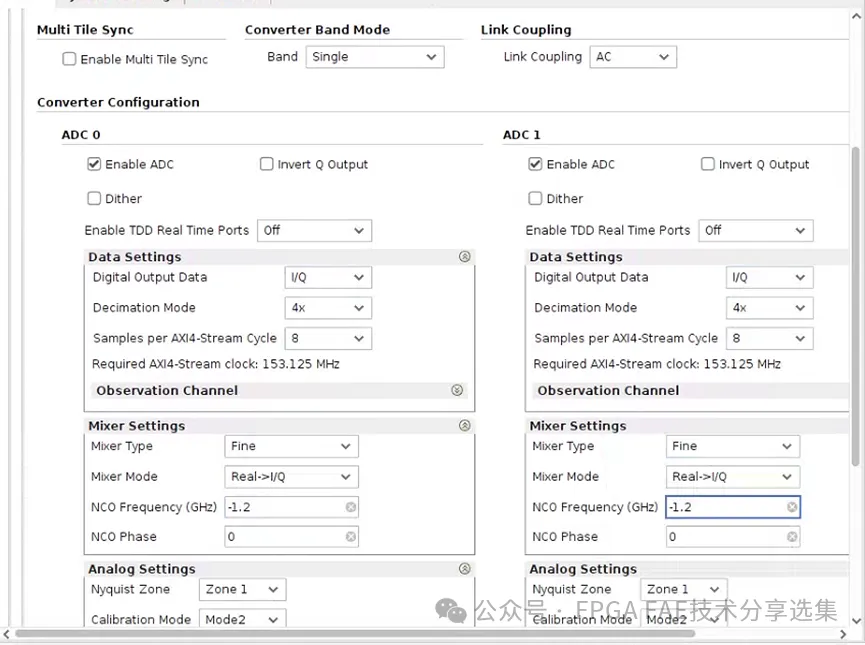

这个输出是IQ模式,4x抽样,每个时钟出8个samples,Mixer混频为-1.2G下变频。

抽样对应DAC的插值;samples per AXI4-Stream是一样的含义,每个时钟周期多少个samples。

额外需要注意一点ADC没有的,是Datapath Mode,参考PG269的描述,额外可以设置一个插值。

IP设置后,正确连接对应的时钟,复位信号。生成的bit,ADC和DAC基本功能就可以运行起来了。