作者:Rachel Gaines,AMD工程师;文章来源:AMD开发者社区

这篇博客是在上一篇博客 Vitis HLS 系列 1 的基础上撰写的,但使用的是 Vitis Unified IDE,而不是之前传统版本的 Vitis HLS。

工具流程为:Vitis Unified (HLS) > Vivado > Vitis Unified(平台和嵌入式应用)。我们将创建一个 HLS 组件,并将其整合到 Vivado 硬件设计中。然后,我们将创建一个独立的嵌入式应用工程,该工程使用 Vivado 中创建的 XSA 作为平台。该嵌入式应用工程将控制 HLS IP。

本教程的运行条件如下:

操作系统:Ubuntu 20.04

版本:2023.2

注释:请确保使用适合您的版本的操作系统 - 受支持的操作系统

这篇博客的底部随附有 Vitis 应用工程的源代码。

与 Vitis 传统 IDE 相比,Vitis Unified IDE 发生了一些变化:

. 外观 - GUI 基于 Visual-Studio 而不是基于 Eclipse

. Vitis HLS、Vitis 库和 Vitis 应用工程以及 Vitis 平台创建都在同一个 GUI 内进行操作

. 术语 - HLS 设计现在称为“组件”,而不是 IP 或内核

. 不再支持多个 HLS“解决方案”并存 - 您将克隆自己的 HLS 设计来比较结果

第 1 步 - 创建 HLS 组件

启动 Vitis Unified IDE 并选择一个工作空间,该工作空间用于集中保存每个 Vitis 工程(HLS 组件、平台工程和应用工程)。

只需在命令行中输入 vitis 即可启动 IDE

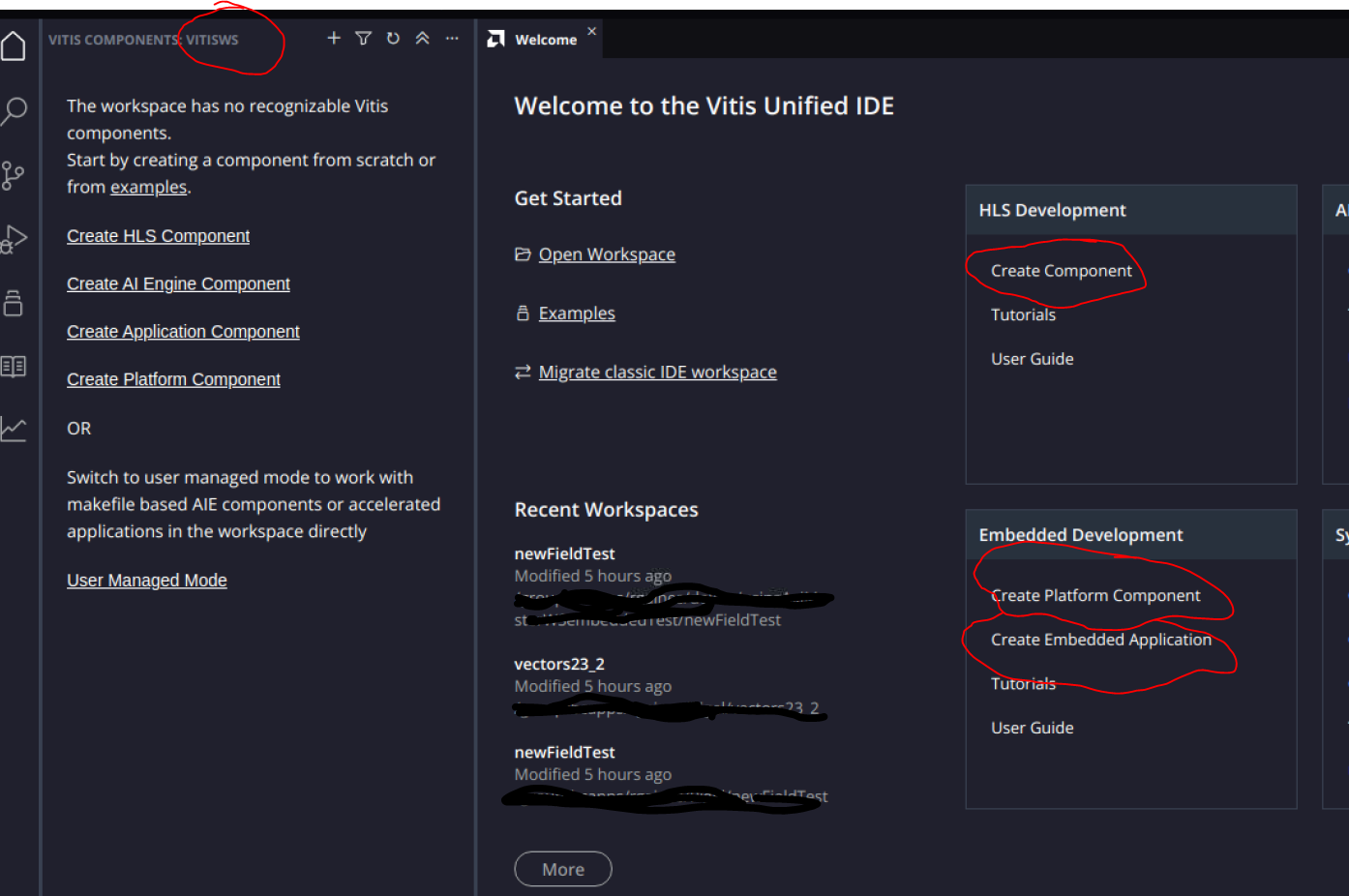

工作空间会显示在左上角,即“VitisWS”。在“Welcome”(欢迎)页面上,有不同的 Vitis 开发框可供选择。我们将创建上面圈出的工程。我们将根据 HLS 设计示例创建一个 HLS 组件。

. 选择左侧的示例图标。导航到“using_axi_master”并单击 + 号

注释:如果未显示 HLS 示例,请通过选择“Vitis HLS Introductory Examples”(Vitis HLS 简介示例)标题旁边的下载箭头来下载仓库

. 选择组件的名称和位置,然后选择“Next”(下一步)。

. 复查汇总信息,然后单击“Finish”(完成)

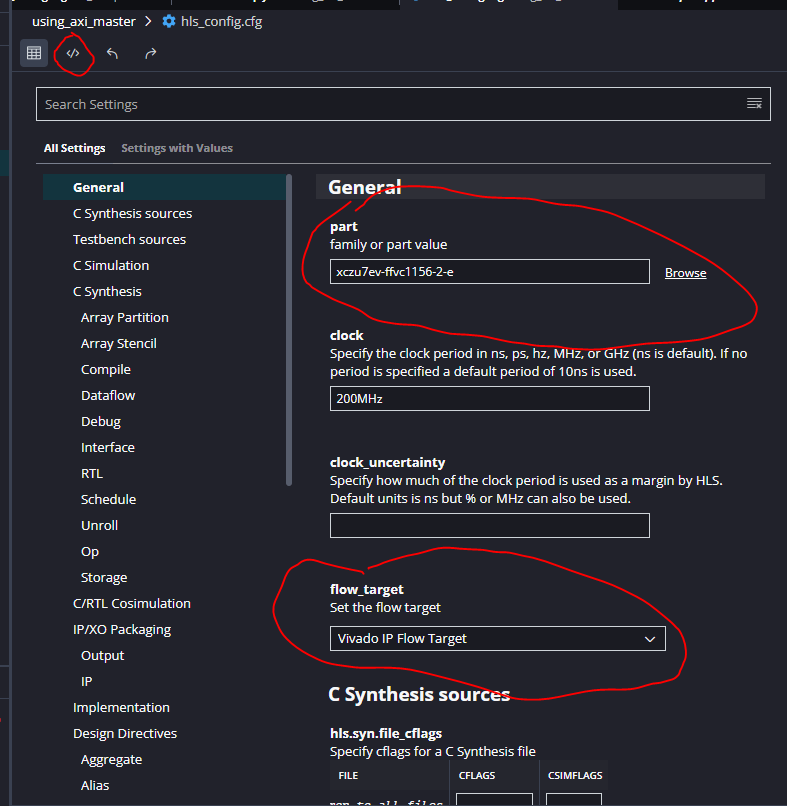

. 打开设置文件 hls_config.cfg,编辑“Part”(部件)、“Flow”(流程)和“Output”(输出)文件

hls_config.cfg 文件是新 IDE 的一部分,也是控制设计设置和编译指示使用的方法之一。您还可以在编辑器窗口(而不是 GUI 视图)中查看该文件。

对于部件,请选择“ZCU104”,对于目标流程,请选择“Vivado IP Flow”(Vivado IP 流程):

选择“IP/XO Packaging”(IP/XO 封装),并确保针对输出格式选择“Generate Vivado IP and .zip archive”(生成 Vivado IP 和 .zip 存档)

. 选择“C Simulation”(C 语言仿真),并选中“Code Analyzer”(代码分析器)框。当前设计过于简单,无法利用该功能,但将来可参考该方法启用该功能。您可以在“C . . . . Simulation > Reports > Code Analyzer”(C 语言仿真 > 报告 > 代码分析器)下查看分析结果。

. 从 Flow Navigator 运行“C-Simulation”(C 语言仿真)、“C-Synthesis”(C 语言综合)、“C/RTL Co-Simulation”(C/RTL 协同仿真)和“Package”(封装)。您会看到每一项的.旁边都有一个绿色的勾选标记。现在,您已经准备就绪,可以在 Vivado 中使用 HLS 组件了。

. 要更深入地了解如何使用 Unified GUI 进行 HLS 设计,请参阅在 Vitis Unified IDE 中创建 HLS 组件

第 2 步 - 创建 Vivado 平台

. 启动 Vivado 并使用 ZCU104 评估板创建一个新工程

**注释**:请勿将 Vivado 工程保存在您的 Vitis 工作空间文件夹中 - 请将这些工程/工作空间分开保存,以避免工具之间发生任何意外冲突/行为

. 将 HLS 组件添加到 IP 目录中

打开 IP 目录,右键单击“Vivado Repository”(Vivado 仓库),选择“add Repo”(添加仓库)

浏览到导出 IP 的位置,并将“ip”文件夹添加到目录中。默认路径为

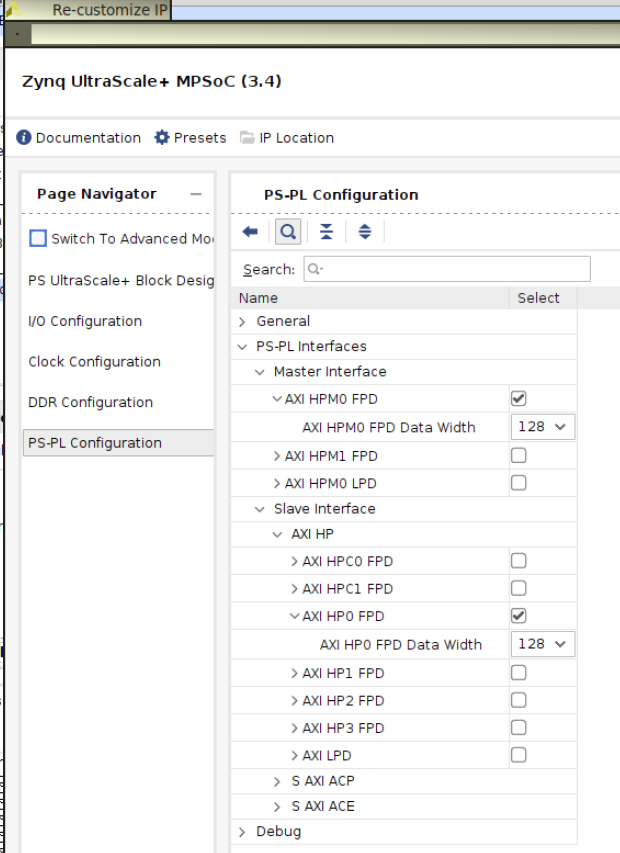

. 创建一个新的块设计,并添加 HLS IP 和 Zynq UltraScale+ MPSoC。通过添加 S_AXI_HP0_FPD 端口来自定义 Zynq 器件。该评估板默认启用 DDR,但请在“DDR Configurations”(DDR 配置)选项卡中确认 DDR 是否已启用。

. 使用设计辅助来运行自动连接。它将通过 AXI Interconnect 和 AXI SmartConnect 自动连接 Zynq 和 HLS IP。

. 当前示例中并未使用中断,但您可以手动将 HLS IP 上的中断端口连接到 Zynq 器件上的 pl_ps_irq 端口。您的设计应与以下示例相似:

. 打开“Address Editor”(地址编辑器)选项卡,确保已如下所示分配了所有地址

. 确认该设计。创建封装文件以及综合、实现和生成比特流的步骤。完成后,选择“File > Export > Export Hardware”(文件 > 导出 > 导出硬件),并选中“include bitstream”(包含比特流)以导出设计,并将 XSA 文件保存到期望的位置。

第 3 步 - 创建独立的嵌入式应用

. 您的 Vitis Unified 工作空间应该仍处于打开状态。如果未打开,请重新打开用于 HLS 组件的工作空间。嵌入式应用的设置分为两步。

构建平台

. 从“Welcome”屏幕中选择“Create Platform Component”(创建平台组件),用 XSA 创建自定义平台

. 选择“Name”(名称),将“Location”(位置)保留默认值(前提是默认设为您的工作空间路径)

. 浏览至第 2 步中创建的 XSA

. 这时将自动填充操作系统和处理器

. 复查汇总信息,然后单击“Finish”

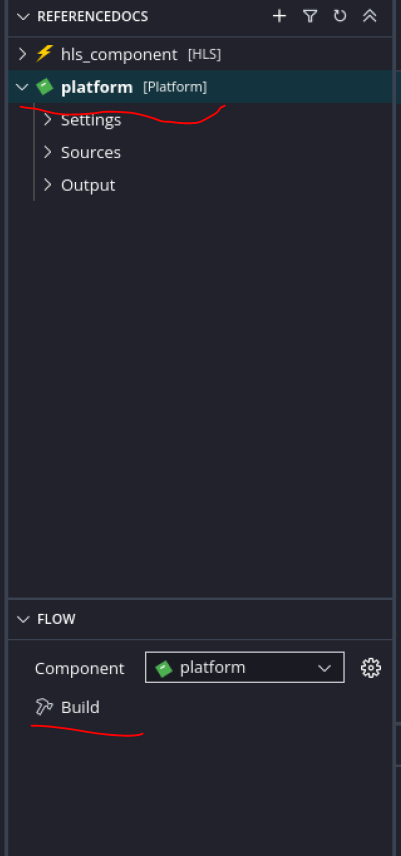

. 注释:此过程需要一些时间,但您将在左下角圈出位置看到平台创建的进度,然后它将作为一个工程出现在工作空间中

. 在工作空间中列出平台工程后,从 Flow Navigator 中选择“Build”(构建)来构建平台,以供嵌入式应用工程使用

构建应用

. 要更深入地了解应用过程,请参阅 Vitis Unified 嵌入式 IDE 入门

. 从“Welcome”页面选择“Create Application Component”(创建应用组件),或者选择“File/New Component/Application”(文件/新建组件/应用)

. 选择“Name”,将“Location”设置为工作空间路径,单击“Next”

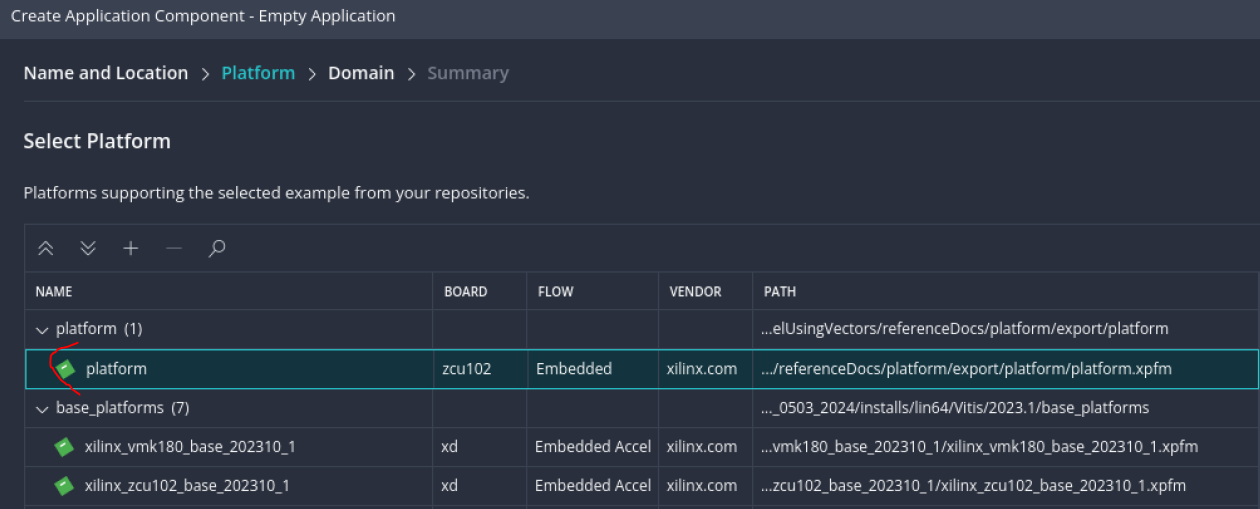

. 选择刚刚构建的平台,单击“Next”

. “Domain”(域)将会自动生成 - 对于本示例,应该会列出 standalone 和 psu_cortexa53_0

. 复查汇总信息,然后单击“Finish”

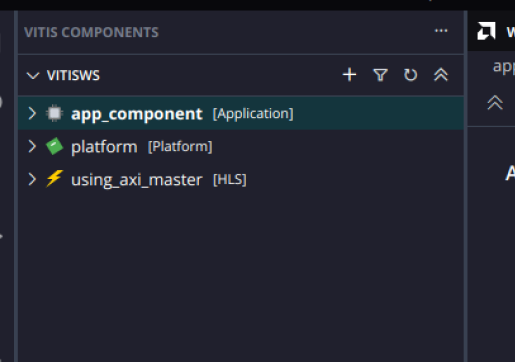

现在,以下三个 Vitis 组件全都会出现在当前工作空间内 - HLS 组件、平台组件和嵌入式应用组件:

. 将这篇博客随附的源代码添加到应用工程中:

展开应用的 component/Sources/src

右键单击“src”文件夹,然后选择“Import > Files”(导入 > 文件)

在应用代码中,可通过调用 HLS 自动生成的驱动程序函数 xexamples.h 来控制 HLS IP。这些驱动程序来自 XSA,在创建平台工程时生成

. 构建应用工程

. 构建完成后,您即可编辑调试/运行配置选项,以连接到评估板,并在硬件上运行设计

在 ZCU104 评估板上,已通过选择“Run As”(运行方式)选项中的“Launch Hardware”(启动硬件)来对该工程进行了测试和验证。当连接到该评估板时,您还可以运行调试器并单步执行代码。您可使用终端连接到 UART (com0),以查看硬件上的输出。