作者:Jimmy Chen,来源:FPGA FAE技术分享选集

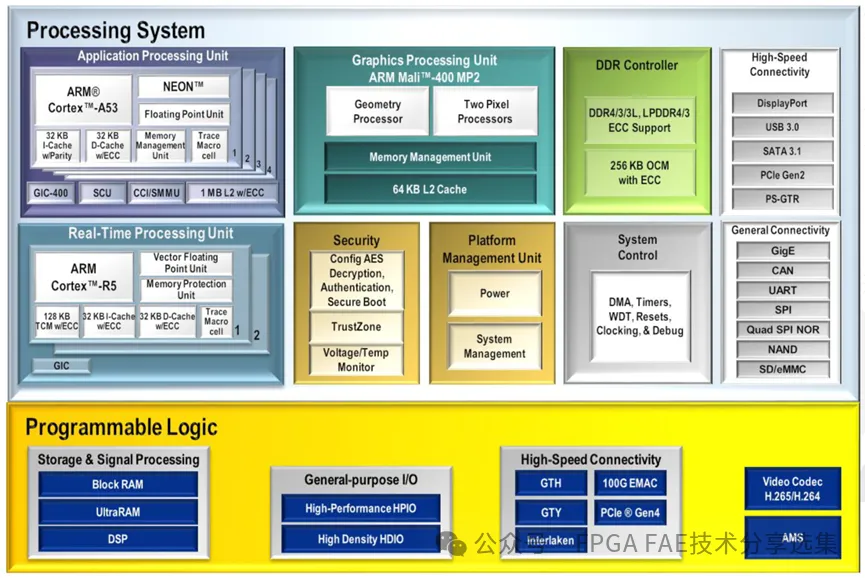

在工业控制,工业通信领域,即需要高性能,也需要高实时性要求,同也能继承原有在裸机下运行的业务程序,满足无缝迁移的要求。例如EtherCAT主站设计,及部分工业控制中,原有业务运行在Bare Metal下,在这种情况下,使用Zynq UltraScale+ MPSoC AMP,就可以运行在高性能的A核上,而不是R核。即满足高性能\高实时性要求,也可以尽可能小的改动下,迁移业务。

为了实现上面需求,本文主要描述Zynq UltraScale+ MPSoC中APU多个A53,怎么设置成AMP非对称处理模式,让整个系统既能满足性能要求,也能满足实时性要求。

多核处理器相关概念:

从硬件视角看:

1.同构多核:多个核心的架构一致;MPSoC APU是多个A53核,同构。

2.异构多核:多个核心架构不一致;MPSoC PS包括APU和RPU,A53和R5组成就是异构多核。

从软件视角看:

1.非对称处理AMP(Asymmetric Multi-Processing):多个处理器运行各自的程序,相互之间隔离。

2.对称处理SMP(Symmetric Multi-Processing):多处理器运行同一个OS,由OS统一调度。

设置成AMP非对称处理模式具体操作方式如下:

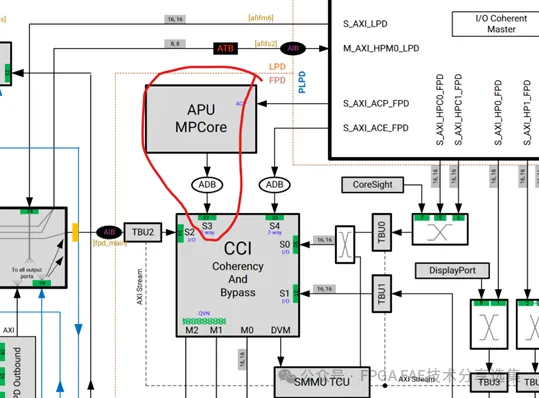

1.Zynq UltraScale+ MPSoC设置CCI(Cache Coherent Interconnect),避免Cache不一致。

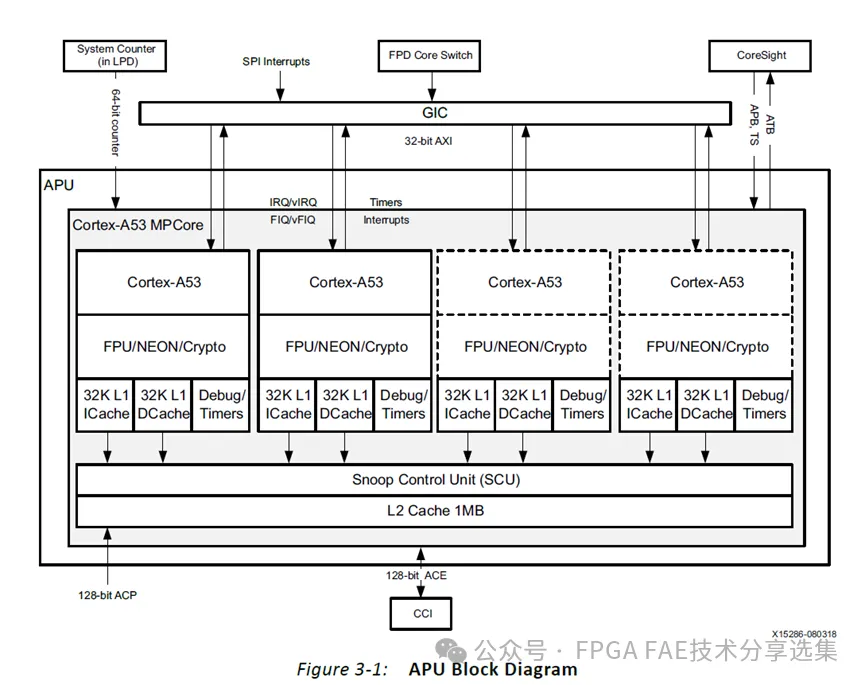

下面是MPSoC A53基本架构的关键部分:

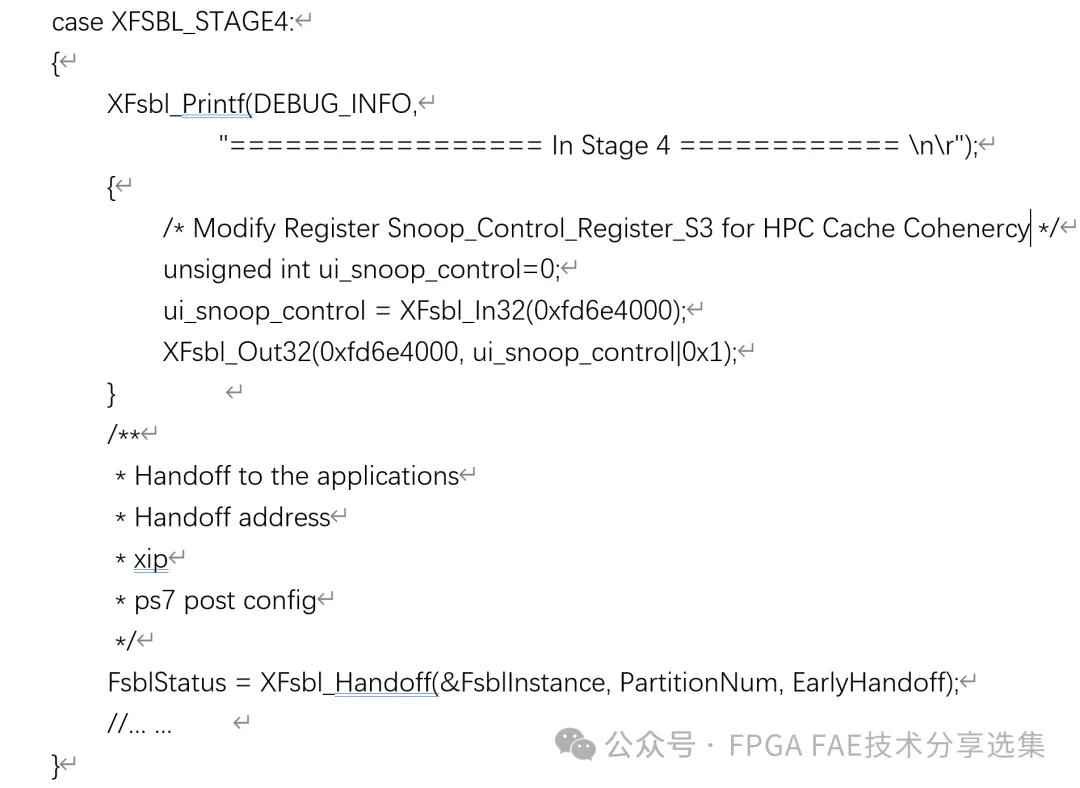

FSBL使能CCI监听APU,避免A53 Cache不一致;FSBL使能CCI监听APU操作实现如下:

缺省情况下,MPSoC CCI (Cache Coherent Interconnect)不监听传输。为了利用CCI Cache同步功能,需要使能CCI监听传输功能。

设置寄存器Snoop_Control_Register_S3,其地址0xFD6E4000的最低位,使CCI监听APU cluster。寄存器Snoop_Control_Register_S3最低位的含义是Enable issuing of snoop requests from slave interface S3。在FSBL的xfsbl_main.c的main()里添加下列修改Snoop_Control_Register_S3的部分代码:

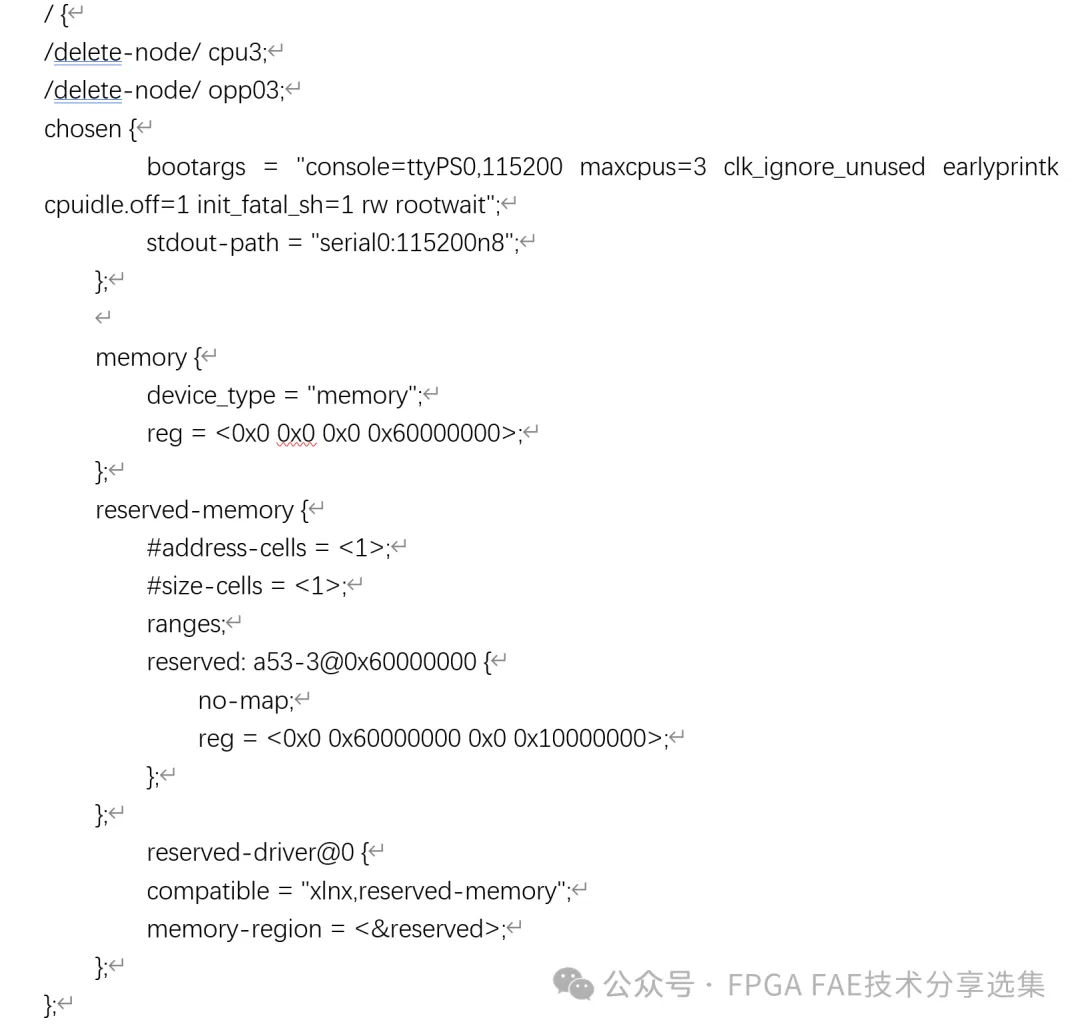

2.设置linux设备树:

设置A53 linux核的使用,设置保留内存给Bare Metal使用。

设备树配置:

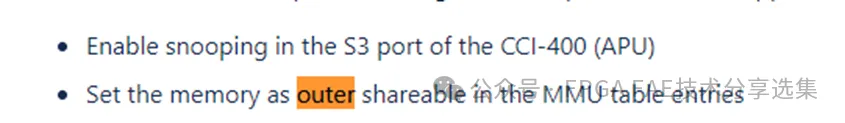

3.需要设置Broadcasting Inner Shareable

内存的cache属性包括non-shareable\inner shareable\outer shareable。inner shareable范围只包含A53和L2 cache。缺省情况下,Inner Shareable的内存传输不会被广播给CCI。Linux缺省设置cacheable memory为Inner Shareable,导致CCI看不到所有cacheable memory的传输。为了使能硬件同步cache,必须使Inner Shareable的内存传输也被广播给CCI。

寄存器lpd_apu(0xFF41A040)的最低两位有这个功能:

bit 0:表示Enable broadcasting of Outer Shareable trasnactions;

bit 1:表示Enable broadcasting of Inner Shareable transactions。

注意,必须在A53处于复位态时设置寄存器LPD_APU。

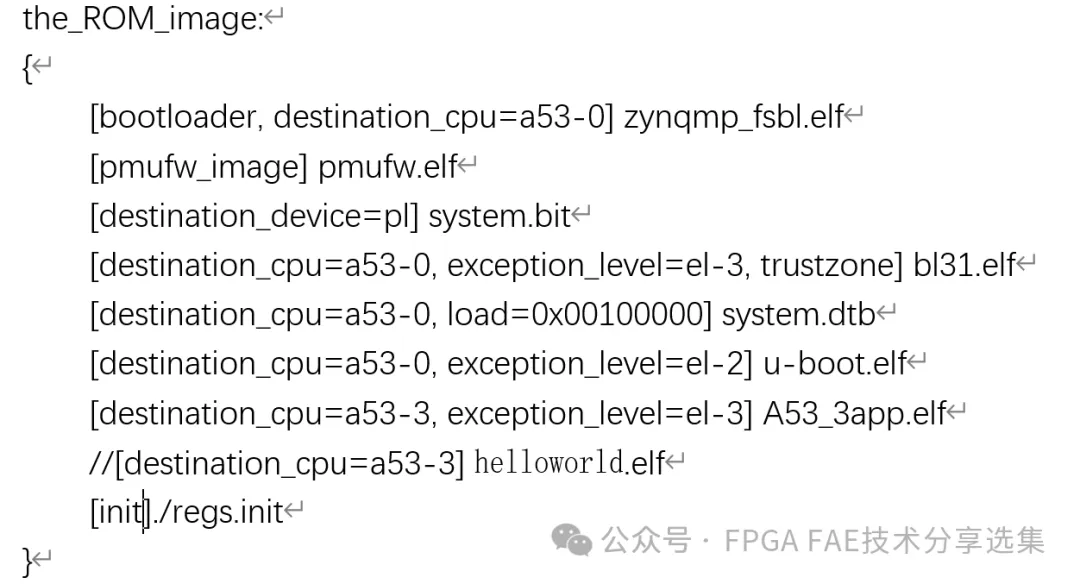

4.用启动文件boot.bin里的寄存器初始化功能设置寄存器LPD_APU,使BootRoM在加载时设置寄存器LPD_APU,可以达到上述要求。具体细节请参阅ARM体系结构参考手册ARMv8的D4.3节,了解ARMv8-A体系结构配置文件(DD10487A)。

使用的方式是,编写寄存器初始化文件regs.init,并加入到BOOT.BIN中。

准备寄存器初始化文件,置寄存器lpd_apu最低两位都为1。

.set. 0xFF41A040 = 0x3;

完整的boot.bin的配置信息,bootgen.bif

在bootgen.bif文件中,需要区分是Bare metal还是Linux

对于Bare metal,处理器跑在EL3,要配置成secure memory访问;

对于Linux,需要配置成2,产生non-secure的访问。

如果您了解更多关于MPSoC AMP方面应用,欢迎联系我们,同时也感谢Trevor在此文提供的友情指导。