赛灵思 App Store, 助力万物加速!

judy 在 周五, 03/19/2021 - 10:31 提交

赛灵思应用商店 (Xilinx App Store) 是赛灵思首次面向广大用户所提供的数字化自适应加速应用发布平台,其加速应用来自赛灵思、第三方合作伙伴和优质独立软件开发商。目前,Xilinx 应用商店支持多种领域的加速计算,包括视频及图像处理、数据分析、高性能计算、机器学习及网络安全等

赛灵思应用商店 (Xilinx App Store) 是赛灵思首次面向广大用户所提供的数字化自适应加速应用发布平台,其加速应用来自赛灵思、第三方合作伙伴和优质独立软件开发商。目前,Xilinx 应用商店支持多种领域的加速计算,包括视频及图像处理、数据分析、高性能计算、机器学习及网络安全等

一图读懂赛灵思全新UltraScale+成本优化型产品组合

本文提供Versal™ ACAP编程和设计的软件专用信息。

在2月28日全球最顶尖的FPGA'21大会上,PYNQ团队发布了全新的RFSoC-PYNQ开源框架,示范应用,硬件平台以及丰富教学资源。此次发布不仅仅包括RFSoC-PYNQ框架,对应的Jupyter Notebook全部开源的应用实现。

在 "人工智能引发能源问题,我们该怎么办 (一)"中,我们简要介绍了更高层次的问题,这些问题为优化加速器的需求奠定了基础。作为一个尖锐的问题提醒,现在让我们通过一个非常简单的图像分类算法,来看一看与之相关联的计算成本与功耗。

设备树是 Petalinux kernel 的关键组件,接下来以 2020.1 版本为例,为大家介绍一下在Xilinx Petalinux 工程中的设备树是如何产生,配置以及修改的。

SmartLynq+ 模块的构建旨在满足高速调试和跟踪需求,主要面向使用 Versal™ 平台的开发者。与以前的赛灵思调试产品相比,SmartLynq + 模块通过 HSDP 可将 Linux下载时间最多提高28倍,并将数据捕获速度提高100倍。

前不久,赛灵思联手 Hackster.io 举办首届赛灵思自适应计算挑战赛,号召独立开发者利用 Vitis 统一软件平台和 Vitis AI 在选定的赛灵思硬件平台上开发新应用,以创新方法解决现实问题。在来自全球的 70 多个独创项目中,评委为每个类别甄选出三个冠军项目,分别获得高达 10,000 美元的奖金奖励。

多输入多输出(MIMO)技术已被许多无线系统采用,以利用信道的空间多样性。本应用说明展示了在Xilinx® Versal™ AI Core器件的AI Engine阵列上高效实现波束成形功能。

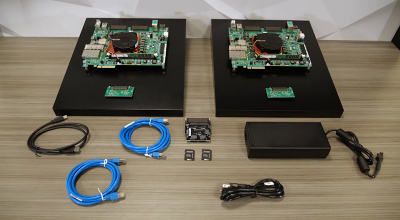

配备业界首个自适应计算加速平台(ACAP)的 Xilinx Versal AI Core 系列 VCK190 评估套件和 Versal Prime 系列 VMK180 评估套件现已推出。