性能提升100 多倍!—— Xilinx Versal 评估套件上市, 助力开发者阔步迈入解锁ACAP功能的高速路

judy 在 周五, 01/08/2021 - 15:28 提交

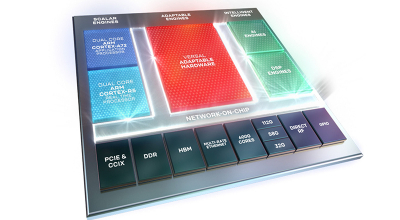

装备业界首个自适应计算加速平台(ACAP)的赛灵思 Versal AI Core 系列 VCK190评估套件 和 Versal Prime 系列 VMK180 Prime 评估套件,现已上市!VCK190 是赛灵思首款 Versal™ AI Core 系列评估套件,可帮助设计者使用 AI 和 DSP 引擎开发解决方案,与当前服务器级 CPU 相比,该解决方案可将计算性能提升 100 多倍!