Versal ACAP,APU - 跟踪系统中发生 ATB 停滞可能引发处理器死锁

judy 在 周五, 04/30/2021 - 09:34 提交

处理器可使用等待事件 (wait for event, WFE) 或等待中断 (wait for interrupt, WFI) 机制来进入低功耗状态。仅当嵌入式跟踪宏单元 (Embedded Trace Macrocell, ETM) 耗尽 AMBA ATB 接口上的所有跟踪字节后,处理器才能进入低功耗状态。

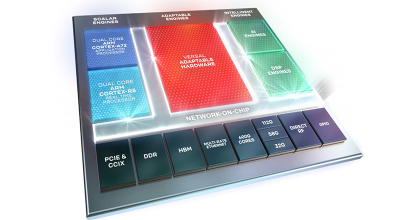

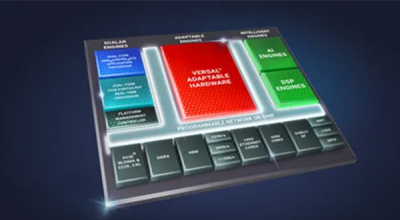

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

处理器可使用等待事件 (wait for event, WFE) 或等待中断 (wait for interrupt, WFI) 机制来进入低功耗状态。仅当嵌入式跟踪宏单元 (Embedded Trace Macrocell, ETM) 耗尽 AMBA ATB 接口上的所有跟踪字节后,处理器才能进入低功耗状态。

赛灵思今日宣布,其 Versal AI Core 与 Versal Prime 系列器件现已全面量产并向客户出货。此外,Versal 产品组合的第三个系列 Versal Premium 也已通过赛灵思早期试用计划出货给多家一级客户。

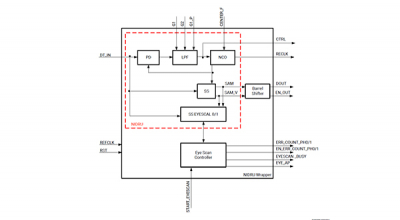

本文描述了Versal™ ACAP的一个非整数数据恢复单元(NIDRU)。NIDRU将较低的数据速率限制扩展到0 Mb/s,并允许SelectIO作为时钟和数据恢复单元运行。

本文描述Versal™设备中可用的SelectIO™资源。

Alveo 加速卡除了有我们 ultrascale+系列的芯片以外,还有 TI 的 MSP432,它的作用就是监控板子的状态,比如电流电压温度等信息。主控端可以通过 FPGA,访问 MPS432,然后获取这些信息。那么怎么样简单的获得这些信息呢,为此我们准备了 CMSIP。

赛灵思 Versal ACAP 硬件、IP 和平台开发方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。Versal ACAP从设计之初即采用正确方法并尽早关注设计目标(包括 IP 选择和配置、块连接、RTL、时钟、I/O 接口和 PCB 管脚分配)至关重要。

随着技术的发展与革新,服务器、SmartNIC与DPU之间的界限越来越模糊,但实际上,定义与用例之间几乎没有多大关系。今天,我们针对Xilinx日前推出的新一代Alveo SmartNIC产品组合,从中窥探SmartNIC的未来发展趋势:可组合性。

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。

国家政策导向逐步明确;5G发展进一步加速;云计算、大数据迎来又一波发展高峰.........这些因素都注定推动了数据中心产业的转型升级。对于数据中心转型,单从软件或硬件层面中的一个层面下手发力远远不够,需要企业“软硬兼施”,双管齐下,才能在数据中心转型升级的过程中,抢占先机,平顺、快速、完美的完成转型升级。

电源估算工具随 VCK190/VMK180 评估套件提供,是一款允许用户最大限度提高功耗性能比的生产力工具。有了该工具,用户可测量、规划和监控整个开发过程中的电源预算,不会影响在 Versal ACAP 上运行的设计。电源工具是开发板评估与管理 (BEAM) 工具的一个特性,其可为 Versal 评估套件用户提供更高的创造性体验。