ALINX 出席 AMD 自适应计算峰会分享 FPGA 硬件解决方案

judy 在 周三, 07/31/2024 - 10:02 提交

AMD 自适应计算峰会在深圳举行,聚焦 AMD 自适应 SoC 和 FPGA 产品最新动态,以及设计工具和开发环境的前沿技巧

AMD 自适应计算峰会在深圳举行,聚焦 AMD 自适应 SoC 和 FPGA 产品最新动态,以及设计工具和开发环境的前沿技巧

芯驿电子阐述了 ALINX 模块化产品设计理念,展示基于 Versal 系列芯片开发的新品及后续规划。

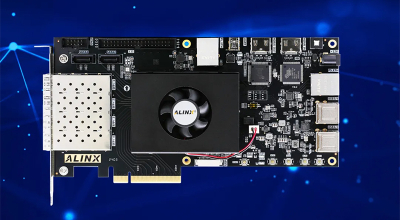

AXP203 是基于紫光同创 Logos-2 系列 FPGA 的综合型开发板,可用作高带宽存储和高速数据传输的应用设计。

芯驿电子携多款 FPGA 新品和行业方案亮相展会,覆盖自动驾驶、AI、工业、医疗、智能制造等行业领域。

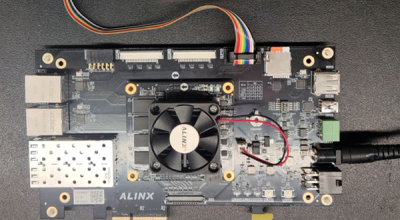

Kosmo-2 开发平台核心板采用双核 ARM Cortex-A53 架构,默认主频高达 1GHz,具备卓越的处理能力。其核心板实现 100% 国产化

开发板有两路千兆以太网,通过RGMII接口连接,本实验演示如何使用Vitis自带的LWIP模板进行PS端千兆以太网TCP通信。

本章使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性

本实验通过PL端Verilog代码直接读写ddr4,主要了解NoC的配置方法

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次

Versal 包含了 Cortex-A72 处理器和 Cortex-R5 处理器,PL 端可编程逻辑部分