AXI DMA详解与应用篇 | 第二讲、AXI DMA工程搭建及SDK代码分析

demi 在 周一, 06/15/2020 - 13:45 提交

在上一篇中着重讲解了DMA的含义和AXI_DMA_IP,本次的重点就是搭建一个AXI_DMA环路工程,并从C语言角度分析其SDK代码

在上一篇中着重讲解了DMA的含义和AXI_DMA_IP,本次的重点就是搭建一个AXI_DMA环路工程,并从C语言角度分析其SDK代码

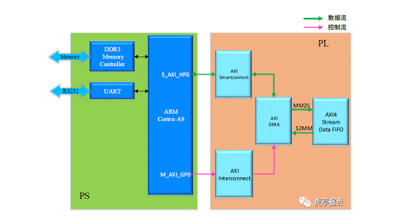

在Xinlinx的ZYNQ中,拥有ARM+FPGA这种架构,每款产品均带有双精度浮点的双核ARMCortex-A9MPCore处理系统,ARM(PS端)具有比较强的事务管理功能,可以用来跑界面以及应用程序等,其优势主要体现在控制方面,里面整合了很多现成的硬件资源供编程调用。FPGA(PL端)灵活性强,拥有更大的并行度和计算能力

如何设计高效的 PL 和 PS 数据交互通路是 ZYNQ 芯片设计的重中之重。AXI 全称 Advanced eXtensible Interface,是 Xilinx 从 6 系列的 FPGA 开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。

AXI2MEM转换接口需要将来自PCIE的AXI信号(时钟为250MHz或者500MHz)转换成100MHz时钟的MEM接口。MEM接口用于SOC总线主端口,用于读写芯片内部模块或者配置寄存器。

本文以xinlinx FPGA PCIE为例,选择集成AXI的PCIE结构为例,说明AXI接口读写地址是如何映射成PCIE读写地址的。

在ZYNQ开发过程中,PS与PL之间的通信是不可避免的,除了MIO与EMIO通信外,还有一种更高速的接口与ARM核通信。本章将创建并测试一个基于高速AXI总线的IP核,以及调用并测试vivado自带的IP核。

AXI 有5个通道:1、写地址通道信号;2、写数据通道信号;3、写响应通道;4、读地址通道;5、读数据通道。

axi_timer模块即为PS可以访问的PL计数器,通过计数值以及接入axi_timer的计数时钟周期,可以在PS内取得比较精确的计时。axi_timer有2种使用方式,一种是作为计数器使用,另一种是作为定时器使用。

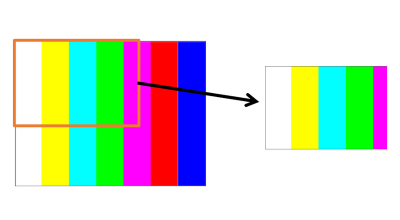

该视频系列 26 展示的是可以如何使用 AXI Video Direct Memory Access (VDMA) IP 来实现视频剪裁、画中画或软模式生成器功能。

在本系列视频中,我们将了解如何将三重缓存模式下设置的 AXI VDMA IP 集成到 Vivado 设计的视频流水中。该设计将针对使用 PS DDR 的 Zynq®-7000 SoC ZC702 评估套件来进行设计。