一种集成FPGA和DSP芯粒的异构系统级封装

judy 在 周二, 06/25/2024 - 15:41 提交

将多个异构芯粒集成在一起进行封装是一种具有广阔前景且成本效益高的策略,它能够构建出既灵活又可扩展的系统,并且能有效加速多样化的工作负载

将多个异构芯粒集成在一起进行封装是一种具有广阔前景且成本效益高的策略,它能够构建出既灵活又可扩展的系统,并且能有效加速多样化的工作负载

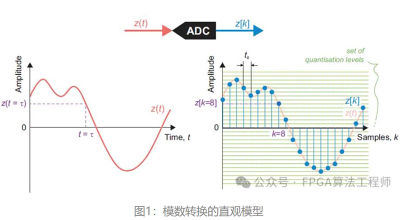

本文系摘录自《RFSoC SDR Book》第四章——DSP Fundamentals,略有改动。下面将介绍采样(Sampling)的基本概念

本文主要介绍说明XQ6657Z35-EVM 高速数据处理评估板ZYNQ与DSP之间EMIF16通信的功能

使用DSP的方法一般有两种:让综合器自己推断、例化DSP原语。有的时候为了偷懒或者有的计数器之类的需要跑高速,则可以让计数器也使用DSP实现。

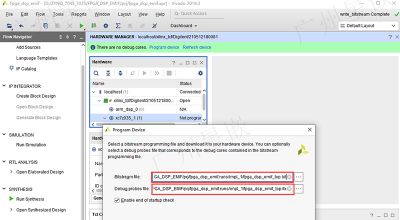

本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。其中提供了有关执行下列操作的分步操作方法指南。

本文介绍了使用16通道发射(16Tx)和16通道接收(16Rx)子数组的实验结果,其中所有发射和接收信道都使用数字转换器集成电路(IC)中的强化型DSP模块来校准。与其它架构相比,这个多信道系统在尺寸、重量和功率上都更有优势。相对于该系统的FPGA资源利用率后可发现,强化型DSP模块可为多信道平台的设计人员解决重要挑战。

了解 Vivado System Generator for DSP 2018.3 版本中的全新超级采样率模块集,提供与 MATLAB® 和 Simulink® 集成的设计流程,以加速 Zynq UltraScale + RFSoC 器件上高速 DSP 应用的设计和实现

建立时间,保持时间

为了确保寄存器在时钟沿稳定采集数据,那么必须要满足寄存器的建立,保持时间要求。

建立时间要求:在寄存器有效时钟沿之前至少Tsetup时间,数据必须到达且稳定。如下图所示。

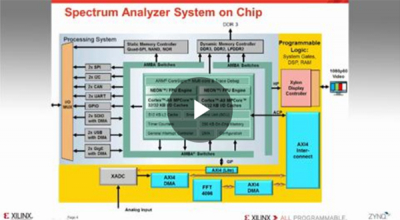

本演示介绍了 Zynq-7000 SoC 及其利用 NEON 引擎或硬件加速功能实现软件加速的能力。敬请查看 Zynq-7000 SoC 在面向数据采集和加速数字信号处理 (DSP) 的单芯片参考设计中的灵活性优势,其不仅可对软件进行加速,还能充分利用处理器和可编程逻辑之间的低延迟和高性能数据传送功能。