一、使用多时钟域实现多速率系统设计

1、简介

多速率的概念是相对于单速率(Single Rate)信号处理而言的。单速率是指整个信号处理流程中只有一种数据速率;多速率是指系统中存在多个数据速率。使用多速率信号处理可以节省存储空间、减少通信数据量、减少运算量、减轻设计难度。

比如在DDC(数字下变频)系统中,前级需要很高的采样率fs确保ADC采集到信号的信噪比;而在去载波并提取出低频的基带信号后,信号有效带宽已经很小,此时可以满足要求的采样率也远远低于fs,如果不进行数据速率转换的处理,会造成许多资源的浪费和设计上的困难

2、创建时钟域层次结构

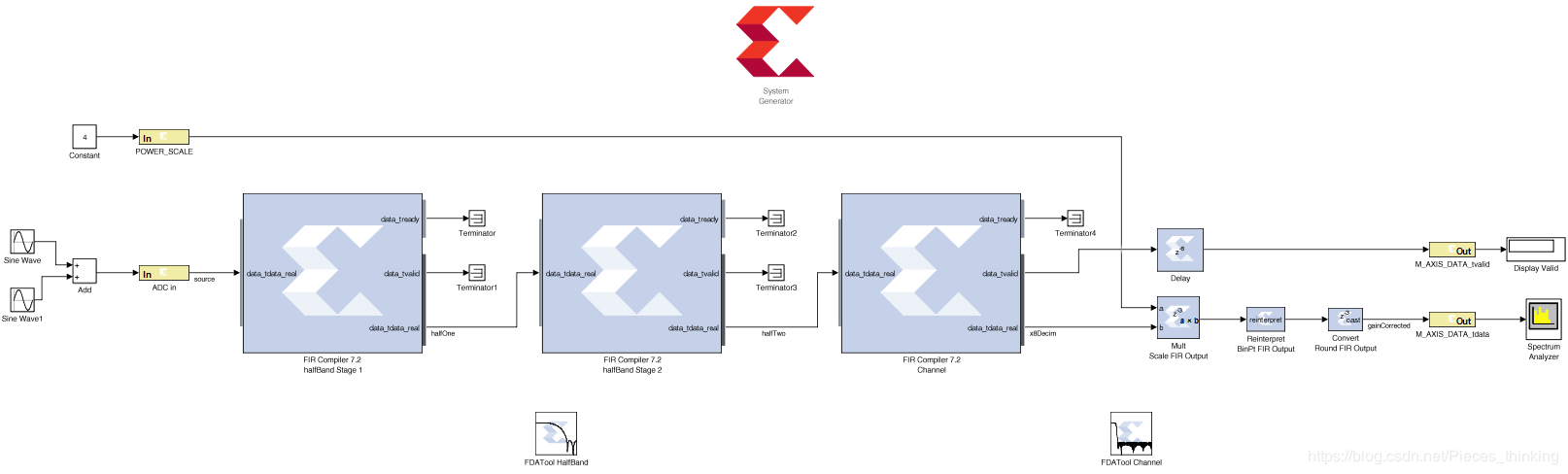

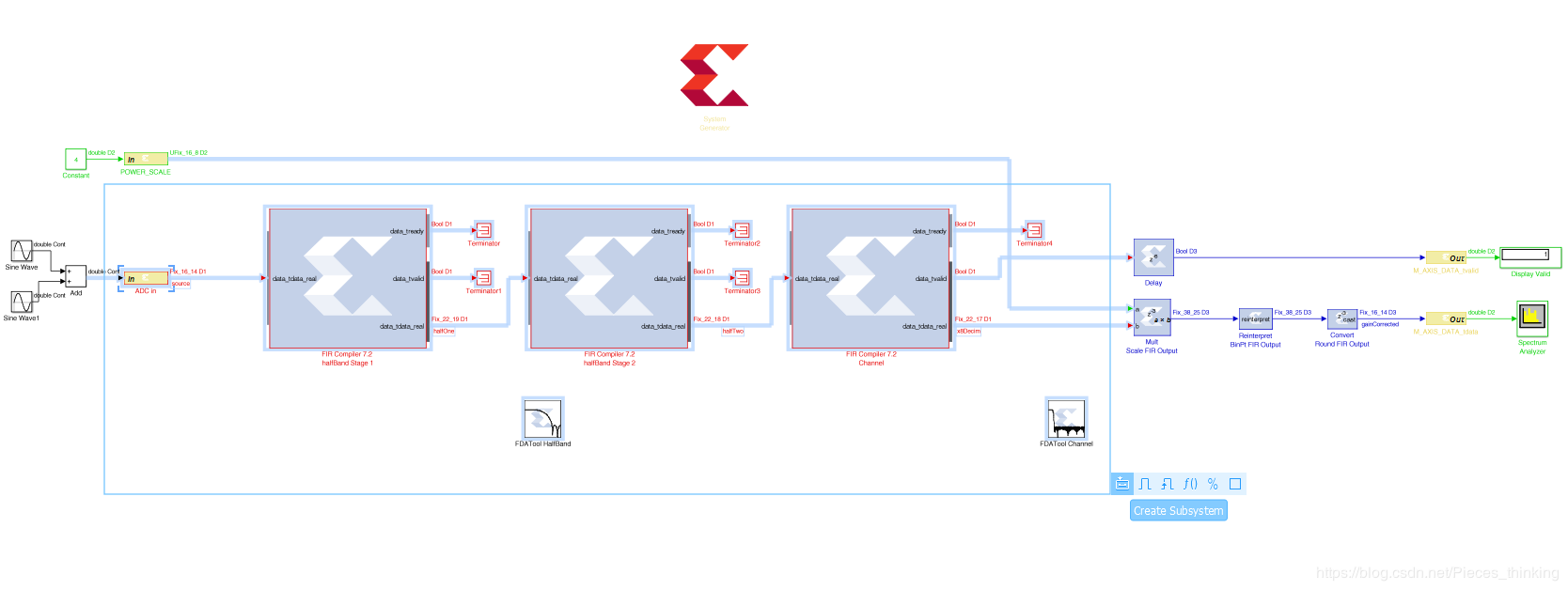

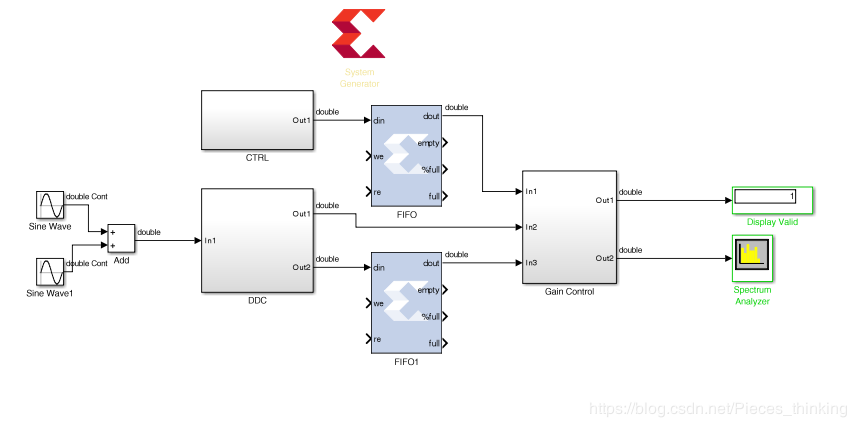

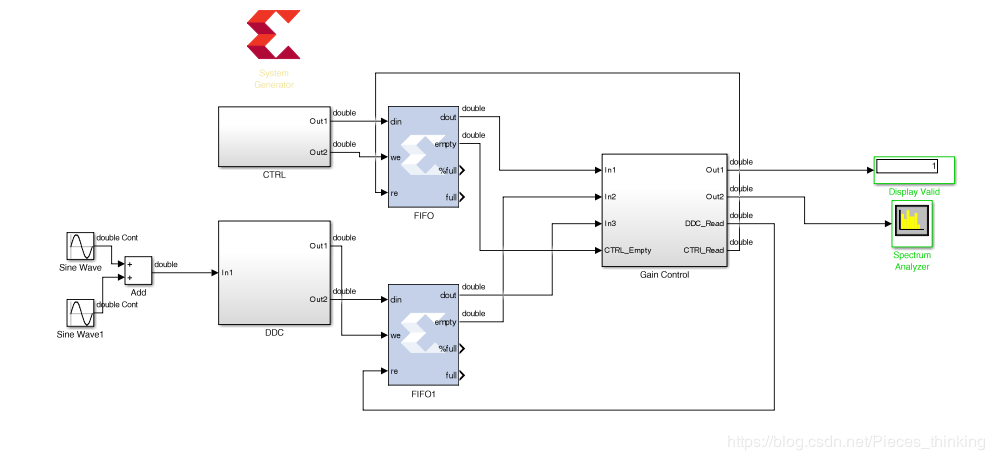

按照下图所示创建一个时钟域层次Model

PS:这部分例程在官方ug948-design-files.zipLab4中找到,由于官方在设计时将一些变量写到.m文件中了,所以需要先运行m文件,将参数输入到matlab工作空间,simulink会自动与工作空间进行交互,然后运行模型。

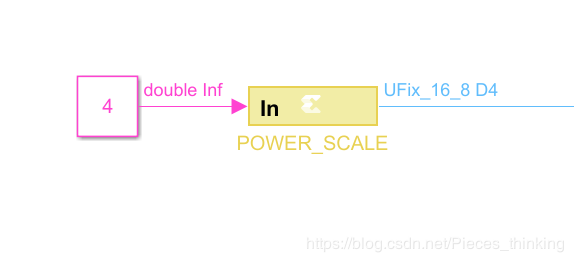

相关的FIX设置如下:

基本Block:

点击Run按钮进行仿真

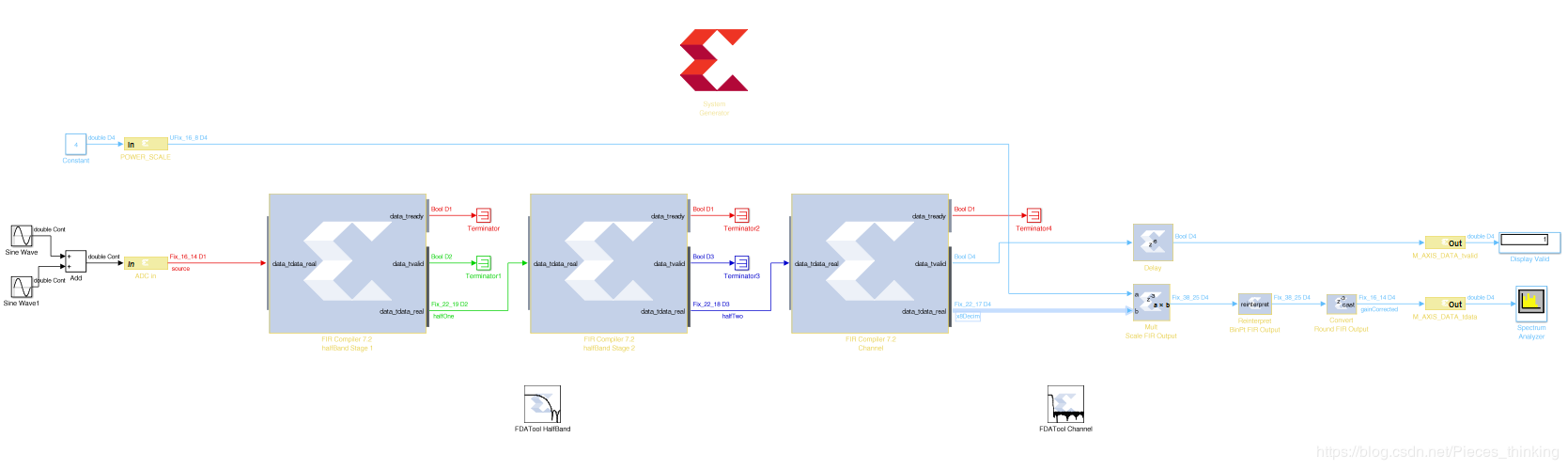

显示多速率运行

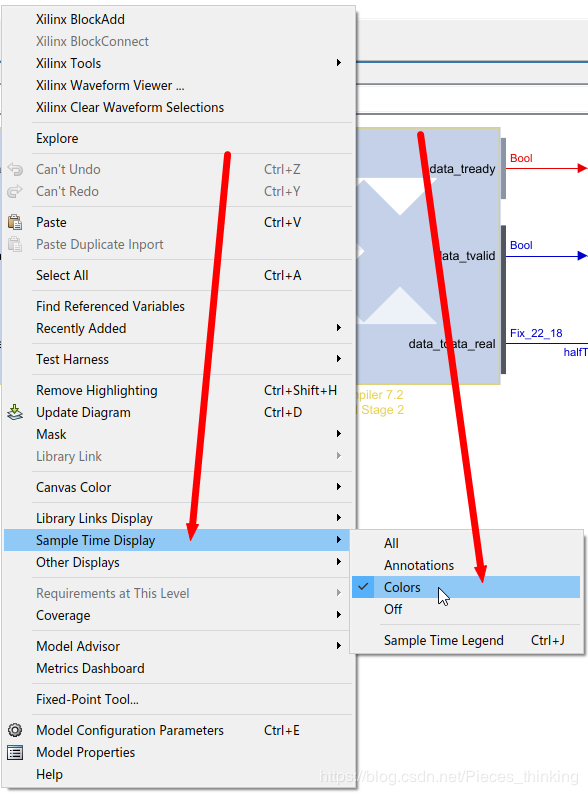

在下面的图中,使用颜色启用Sample Time Display(在背景右击>Sample Time Display>Colors)。

系统会针对不同速率进行颜色的分配。

当这样的多速率设计在硬件中实现时,最优的实现是使用与数据频率相同的时钟;然而,时钟在这种环境中被抽象出来。下面的方法将演示如何以最有效的方式创建以上理想的环境。

要使用System Generator有效地实现多速率(或多时钟)设计,应该使用自己的System Generator为每个层次结构分配相同的时钟频率, 然后将每个层次结构与FIFO链接,就是利用FIFO实现不同时钟域的连接。

多时钟域划分

目前的设计有两个明显、一个不太明显的时钟域:

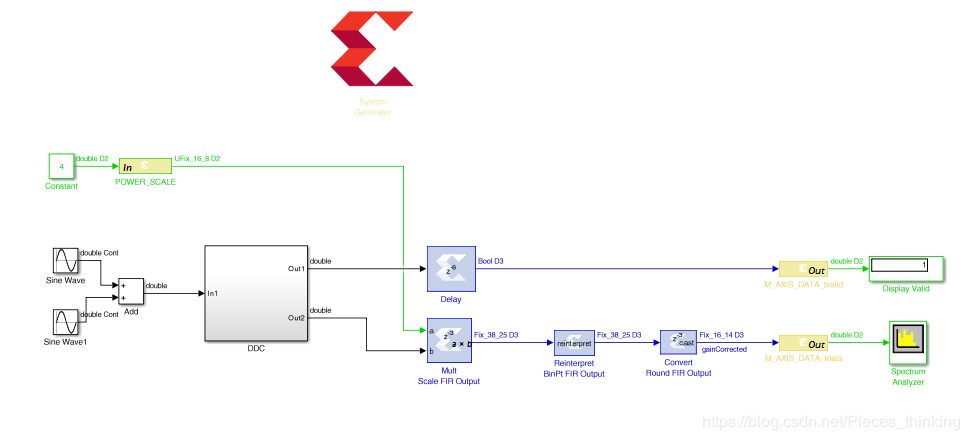

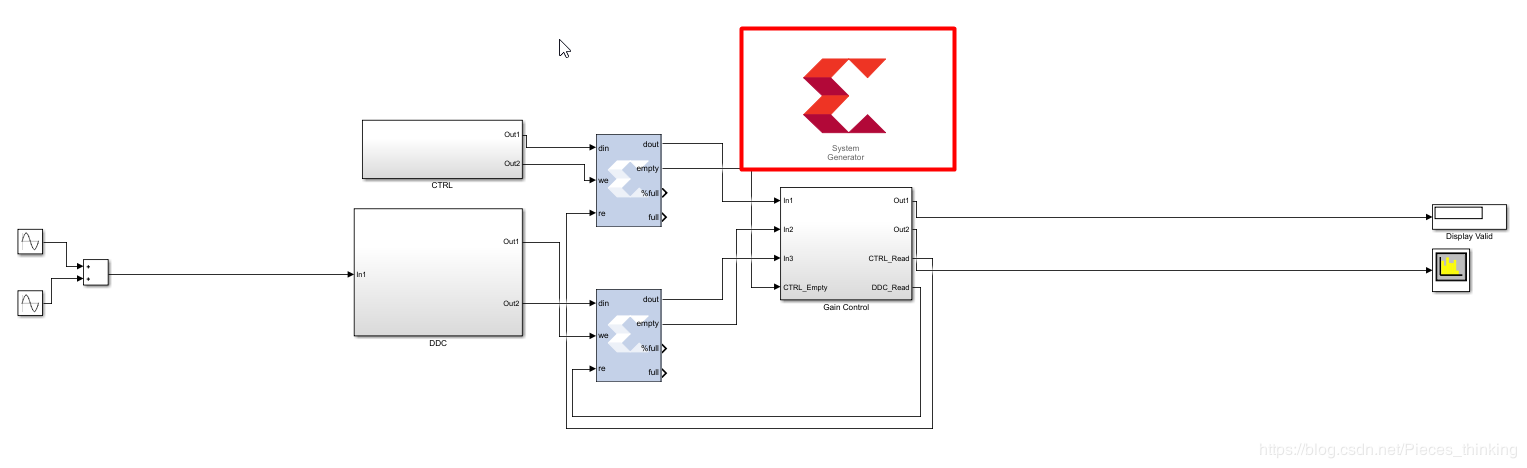

划分,创建subsystem

选择下图Block,右击–>Create Subsystem

重新命名DDC

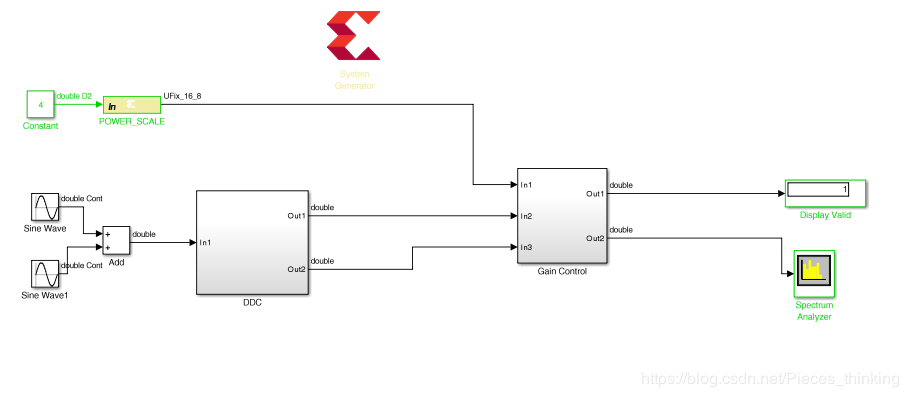

选择output path Block,右击–>Create Subsystem,;重新命名Gain Control

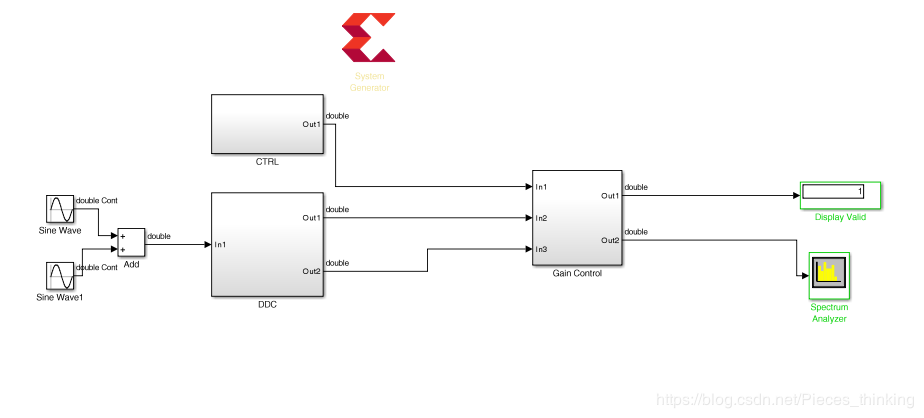

选择Gateway In instance POWER_SCALE and Constant,右击–>Create Subsystem,;重新命名CTRL

当此设计完成时,每个子系统内的逻辑将以不同的时钟频率执行, 时钟域可能彼此不同步。

3、创建异步通道

在此步骤中,您将使用FIFO在子系统之间实现异步通道。 FIFO中的数据以先进先出(FIFO)为基础运行,控制信号确保仅在存在有效数据时才读取数据,并且仅在有可用空间时写入数据。 如果FIFO为空或满,则控制信号将使系统停止。 在这种设计中,输入总是能够写入,并且不需要考虑FIFO满的情况。

两个地方需要FIFO:

如下(FIFO为Xilinx BlockAdd):

添加相关控制信号

下面的几个信号需要添加:

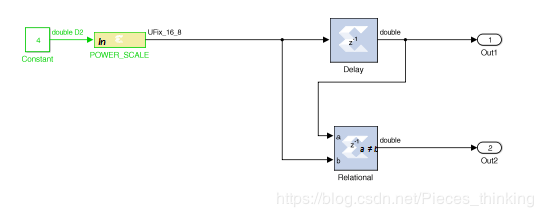

修改CTRL模块

按照下图进行连接

其中Relational block设置如下:

这将在Out2上创建一个输出选通,当输入改变时它将在一个周期内有效,并用作从CTRL到增益控制(顶层FIFO块)的写使能。

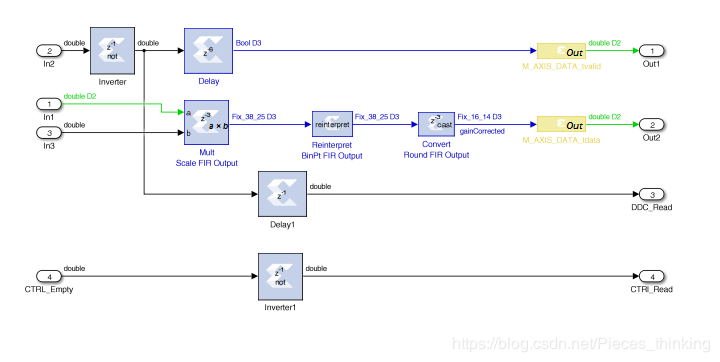

修改Gain Control模块

添加下诉模块和输入输出口:

按照如下方式连接:

来自顶层增益控制FIFO(FIFO)模块的FIFO空信号只是一个反相器模块,用于为顶层DDC FIFO(FIFO1)创建读使能。 如果FIFO不为空,则将读取数据。

同样,来自顶层DDC FIFO(FIFO1)的FIFO空信号被反转,以创建FIFO读使能。

此相同信号将用作新data_tvalid(为In2)。 但是,由于FIFO的延迟为1,因此必须延迟此信号以确保此控制信号与数据正确对齐(现在通过FIFO将其延迟1)。

创建好的结构如下:

FIFO Block的连接

a. Connect CTRL/Out2 to FIFO/we.

b. Connect FIFO/empty to Gain Control/CTRL_Empty.

c. Connect Gain Control/CTRL_Read to FIFO/re.

FIFO1 Block的连接

a. Connect DDC/Out1 to FIFO1/we.

b. Connect FIFO1/empty to Gain Control/In2.

c. Connect Gain Control/DDC_Read to FIFO1/re.

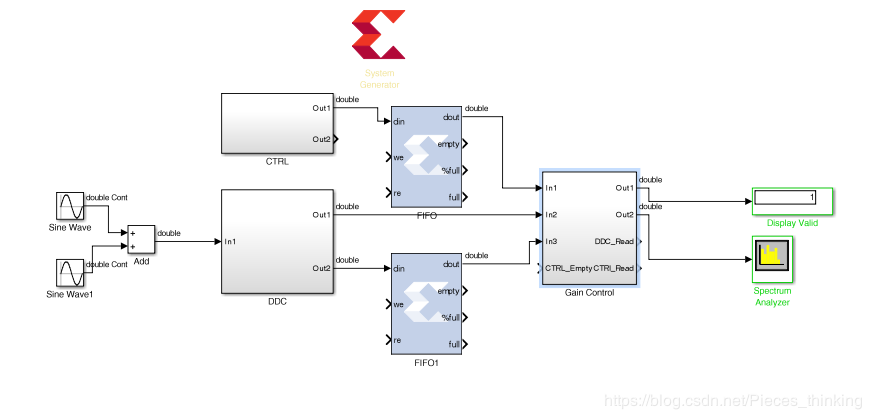

最终结果

运行仿真将得到与第一步相同的结果

3、指定时钟域

指定时钟域,主要利用顶层 System Generator token使能多时钟域,其他Subsystem内添加 System Generator token然后取消使能多时钟域,重新设置时钟。

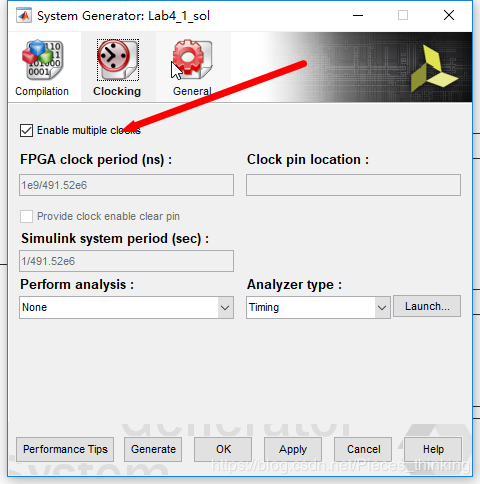

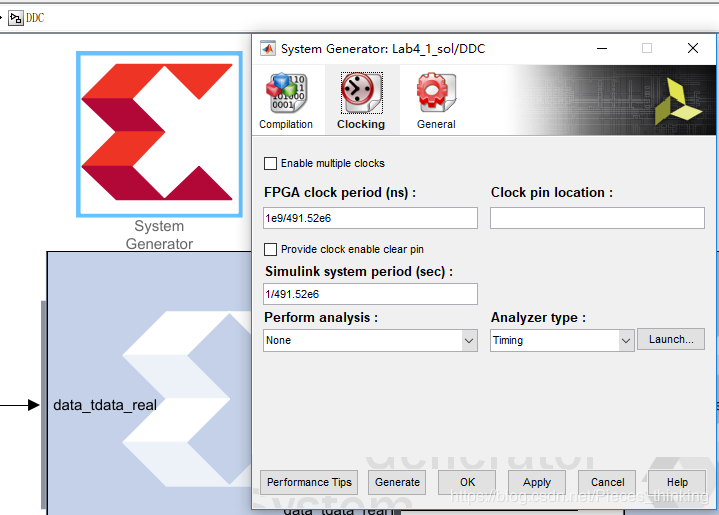

顶层 System Generator token使能Enable multiple clock

此时,请注意,FPGA时钟周期和Simulink系统周期现在变为灰色。 此选项通知System Generator将为每个层次结构单独指定时钟速率。 因此,最重要的是只包含子系统和FIFO; 在多速率设计中,顶层不应存在其他逻辑。

CTRL System Generator token不使能Enable multiple clock并设置相关时钟

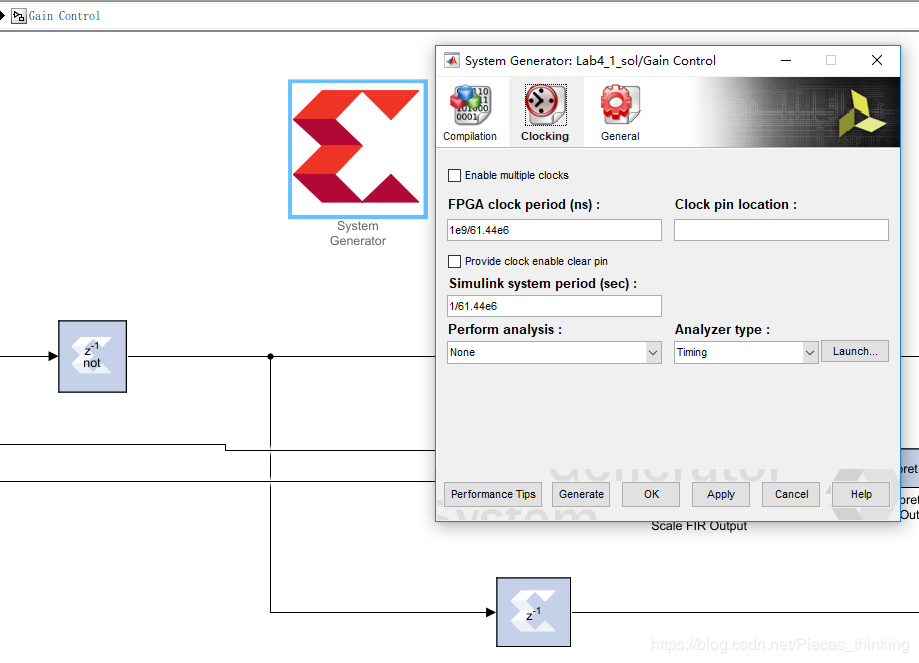

Gain Control System Generator token不使能Enable multiple clock并设置相关时钟

DDC System Generator token不使能Enable multiple clock并设置相关时钟

保存

运行仿真,将得到和之前相同的结果

---------------------

作者:碎碎思

来源:CSDN

原文: https://blog.csdn.net/Pieces_thinking/article/details/83758541