前端时间写过几篇关于FPGA通过SPI接口配置ADC的文章,收到了很多朋友的意见和建议,如今实现方式上又有了很大改进。因此笔者打算再更新几篇关于这方面的内容,并且为了不和以前的内容重复,这次主要以实际操作为主,一些基本的概念就不介绍了。

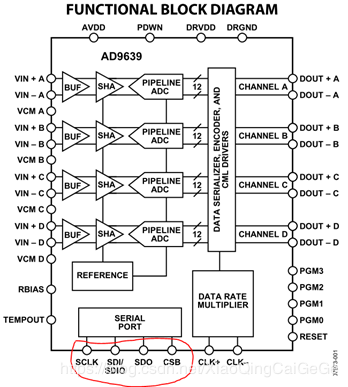

本篇以ADI公司的多通道高速ADC—AD9639为实例,向大家演示FPGA是如何通过SPI协议向该ADC读写寄存器配置数据的。如下图所示为AD9639的功能框图,不难发现其SPI接口既可以实现三线模式也可以实现四线模式,本篇将演示4线模式,三线模式的读写控制咱们下篇见~

既然是实例操作,就必须与硬件相结合。如下图所示为本人以前设计的一款8通道、150MHz采样频率的数据采集卡:8路模拟信号通过SMA连接头接入、系统时钟采用TI的LMK03系列的时钟控制芯片来产生任意频率的时钟供给FPGA和ADC。配置的工程将采用ISE14.7来建立,配置的代码为verilog。

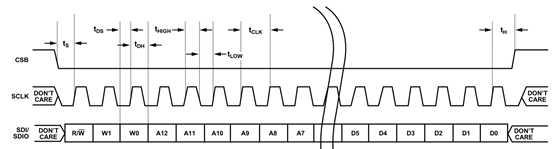

该款ADC和ADI公司其他ADC的SPI配置方式相同,其数据传输的结构如下图所示:

每次事件传输24bit数据,MSB为读/写控制位,接下来2bit为一次传输数据的大小,一般写0即可,A12-A0为地址位,D7-D0为数据位。

当FPGA向ADC读写配置数据时,就需要完成上图的时序功能,每配置一个寄存器,就执行上图的逻辑功能一次,如果是配置多个寄存器,则反复执行上述逻辑即可。

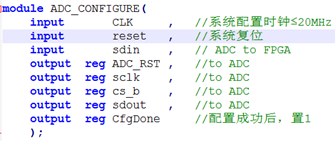

本次的4线配置逻辑的顶层逻辑接口如下图所示:

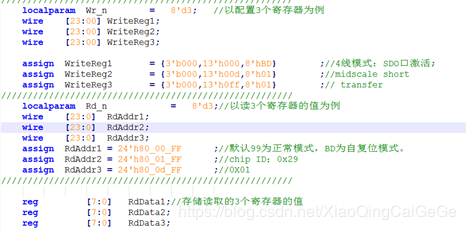

本例程实现了3个寄存器的写和读:如下图所示:

当然,配置个数可以任意改动,只要改变Wr_n这个写参数和Rd_n读参数个数即可。RdData1~3为存储读到的3个寄存器的值,方便chipscope观察。

根据AD9639的手册说明,当配置WrtieReg1后,该寄存器地址读到的数据应该为8’h18;当配置WrtieReg2后,该寄存器地址读到的数据也应该为8’h01;同样读芯片的ID号,结果应该与手册给的8’h29一致。这里大家如果不太清楚,可以查阅芯片手册的配置地址和数据部分章节,里面已经详细说明。

接下里咱们就说下如何用代码具体实现读写过程,首先咱们先介绍FPGA如何向ADC写入配置数据,请看如下代码:

该代码目的是实现一个24bit的寄存器地址+数据的写入,但是咱们要写3个寄存器的数据,而有的ADC可能需要写入更多的配置数据,总不能将代码复制很多遍吧,那样效率太低了,这里咱们就用了一个循环,里面的n值就代表写入的个数,具体如何循环请看如下代码:

该段代码就实现了循环写的功能,因此整个ADC的配置过程只需要4个状态,即可完成全部的配置,是不是很方便呢?

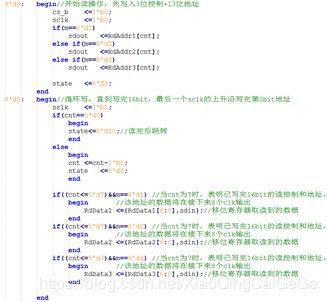

接下来咱们将写入ADC的数据再读出来看看是否配置正确吧,请看如下代码:

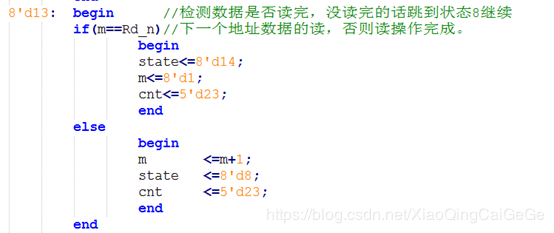

上面的代码就实现了1次寄存器的读操作,咱们需要读3个寄存器的值甚至更多的时候,不可能一次次的读,所以这里也用循环的操作,使代码尽可能简洁,下图代码的功能就是让上图的代码循环m次:

循环m次后,将得到m个寄存器的值,这个例程里是3个值,将这3个值与预期值比较,如果相同,则配置成功,如果不同,则说明哪地方出问题了,需要仔细检查~如下图所示:

这样4线SPI的配置过程就完成了,总共用了15个状态,其中好几个等待状态都是冗余的,实际应用中大家去掉也没事。用上面介绍的代码在ise14.7上运行,并下载到电路板上,咱们观察chipscope吧!

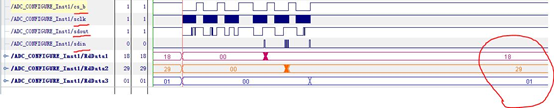

如下图所示为分别读写3个寄存器的时序图,可以看到最终咱们读到的寄存器值分别为8’h18、8’h29、8’h01,与预期值完全一致,配置成功!

咱们再看看逻辑实现的写过程的具体时序图吧,下图所示为写WrtieReg2的实际时序,写入的数据为8’h01:

咱们再看读该寄存器的时序图,如下图所示:可以看到读到的数据也为8’h01,OK!

AD9639的实际操作就这样完成了,介绍性的东西写的较少,以前的几篇都写过,所以本篇直接拿出干货供大家参考。如果一开始不明白的地方,大家可以好好琢磨,毕竟代码也就那么几行,还有注释,搞明白了以后ADI公司的4线ADC的SPI配置就都没问题了~

3线的SPI配置稍微复杂一些,涉及到FPGA的I/O的控制,体现在配置逻辑里则稍微麻烦一点,但也和4线SPI配置大同小异,下篇将介绍~

---------------------

文章来源:XiaoQingCaiGeGe的博客

声明:本文由原创博主授权转发,如需转载请联系博主