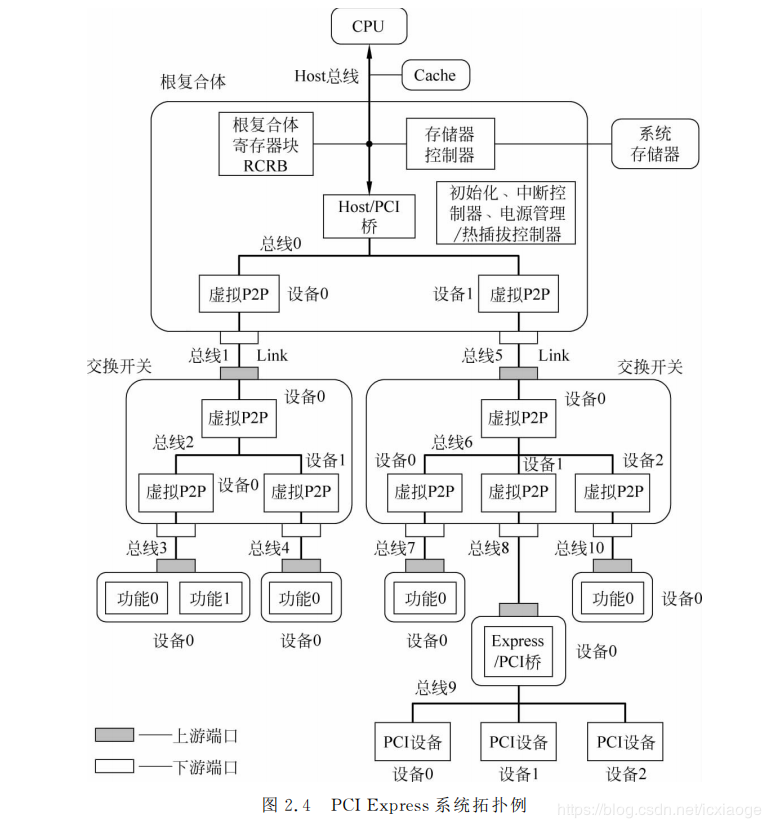

1、PCIE的拓扑结构

RC端通过配置TLP读写EP端PCIE的BAR0/1寄存器,确定EP端PCIE的存储空间。其中配置TLP需要用到总线号,设备号,以及功能号。此类概念如下图。

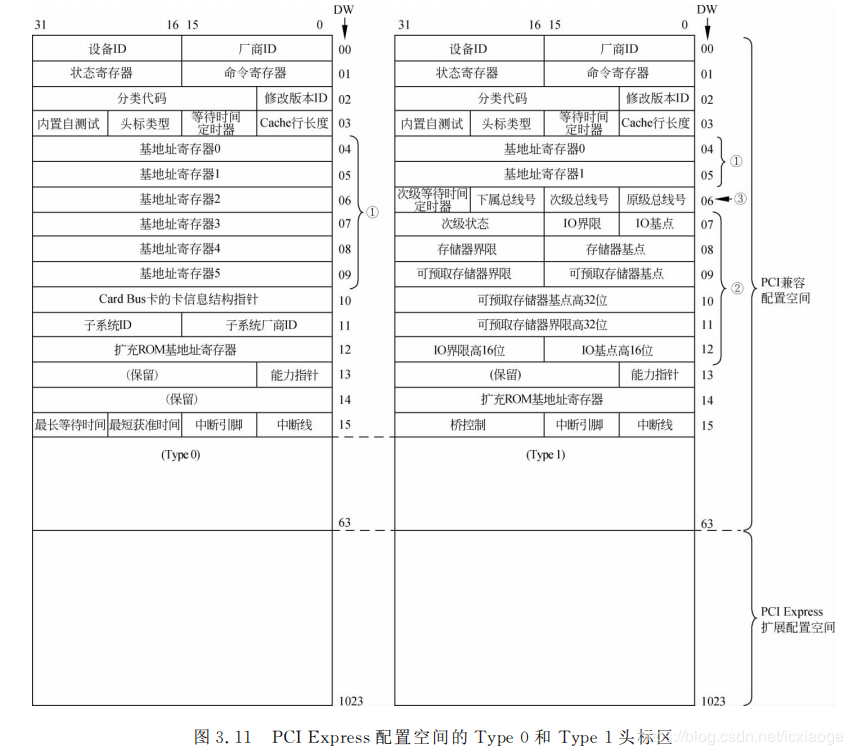

2、PCIE的配置空间

PCIE支持基本的PCI兼容配置空间(256B、64DW)和PCIE扩展配置空间(扩展4KB,1024DW),其中PCI兼容配置空间的头16个DW称之为配置空间头标区,非桥设备使用Type0头标区格式,上图左侧所示。桥设备(包含根复合体和交换开关中的虚拟桥)使用Type1的头标区格式,上图右侧所示。

3、用来配置BAR0/1的配置TLP是如何构成的。

RC端PCIE使用ID路由来配置EP端PCIE的BAR0/1,以确定EP端PCIE的存储空间。

在PCIE拓扑结构中,配置TLP如何选择目标PCIE的BAR0/1是由配置TLP中的Bus Number、Device Number、Function Number以及register number字段来确定的。

如上图所示为3DW格式的配置TLP格式。

Requester ID[15:0]

用来标识配置TLP的请求者,以便对应完成能够返回。在Requester ID[15:0]中,位[15:8]为总线号,位[7:3]为设备号,位[2:0]为功能号,ID号是多少是由请求者在PCIE 拓扑结构中的位置确定的,如图1所示。

Completer ID[15:0](即Bus Number、Device Number、Function Number)

配置请求头标中的字节8~9是该配置周期目标设备的ID:总线号、设备号和功能

号。目标设备在每一个Type0配置写周期中都要“捕获”这个字段中的总线号和设备号。配置EP端就需要将EP端PCIE的ID填写在此字段。

扩展寄存器号Extended Register Number[3:0]和寄存器号register number[5:0]

这两个字段对应着图2中的配置地址。

4、参考文献截图来源

[1]PCI、PCI-X和PCIExpress的原理及体系结构-马鸣锦

版权声明:本文为CSDN博主「IC小鸽」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/icxiaoge/article/details/88773788