增量编译对于电路设计之后的调试非常重要,每次也许只修改了一行代码,改了某个值,如果没有增量编译,就只能重新跑一边项目,对于小项目貌似没有太大影响,但是对于一个大项目,每次改一点内容就要重新进行一遍综合,实现,生成比特流,这个过程及其浪费时间,所以增量编译是很必要的。

下面是官方对于增量编译的描述:

增量编译:

使用增量编译满足最后时刻 HDL 变动需求,仅针对已变动逻辑进行布局布线,从而可节省时间。

- P&R 数据重复使用为时序驱动,可在不影响性能的情况下,加速运行时间。

- 平均速度比标准布局布线快 1 倍。

- 设计收敛保存可减少并加速迭代。

如何进行增量编译:

1、首先完成非增量编译,获得参考的布局布线dcp文件;

2、当逻辑修改小于5%,需重新出版本,采用增量编译;

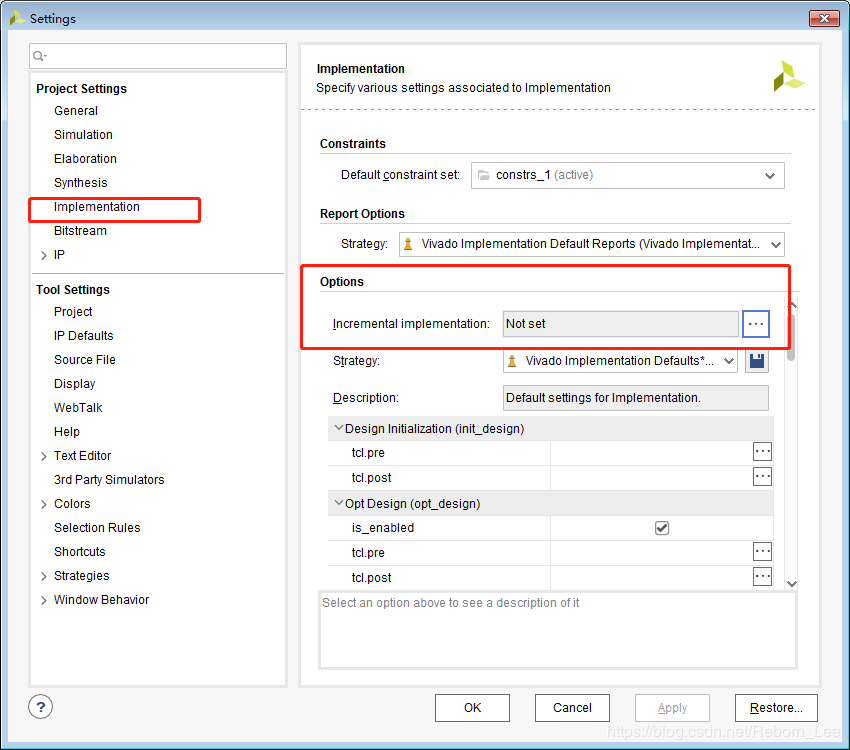

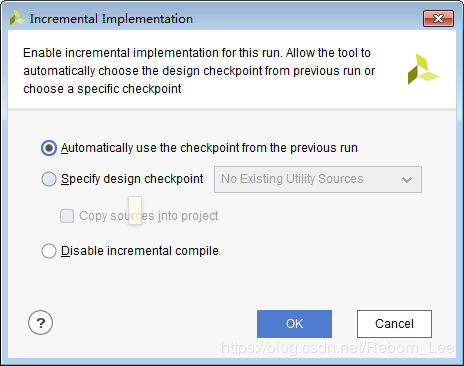

3、按步骤打开:implementation setting——options——incremental compile,浏览文件

4、选择.runs / impl_1 / *.dcp

5、点击run implementation,等待结果

参考链接:增量编译速度提升一倍

哎,实践证明,也节省不了多少时间。

版权声明:本文为CSDN博主「Reborn Lee」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/Reborn_Lee/article/details/99470435