作者:csdn博主红色闪电007

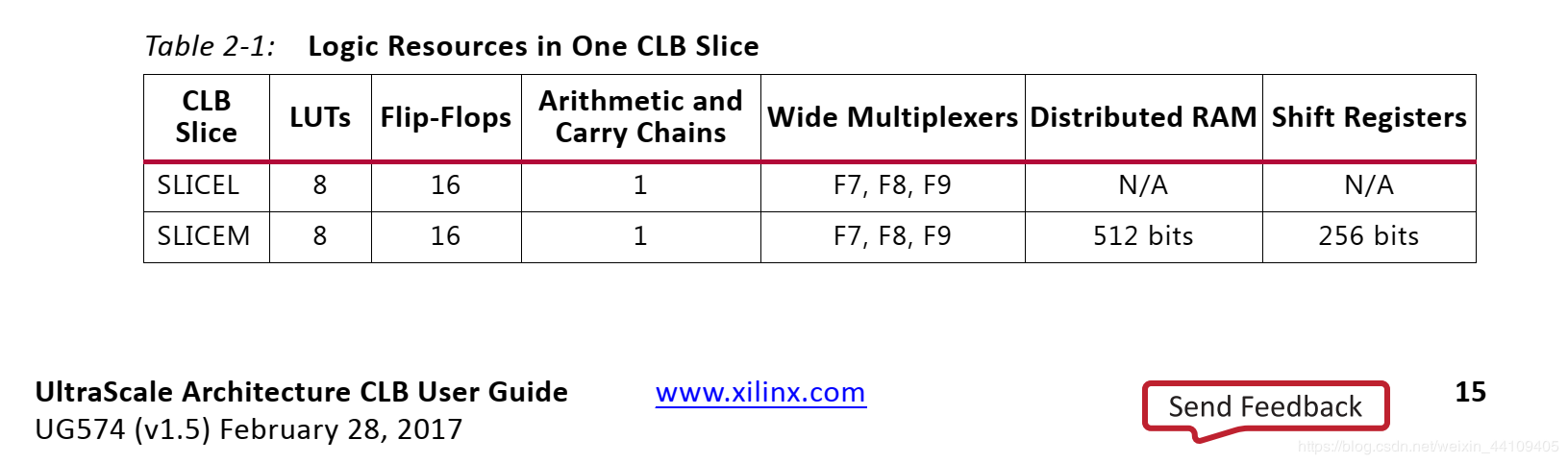

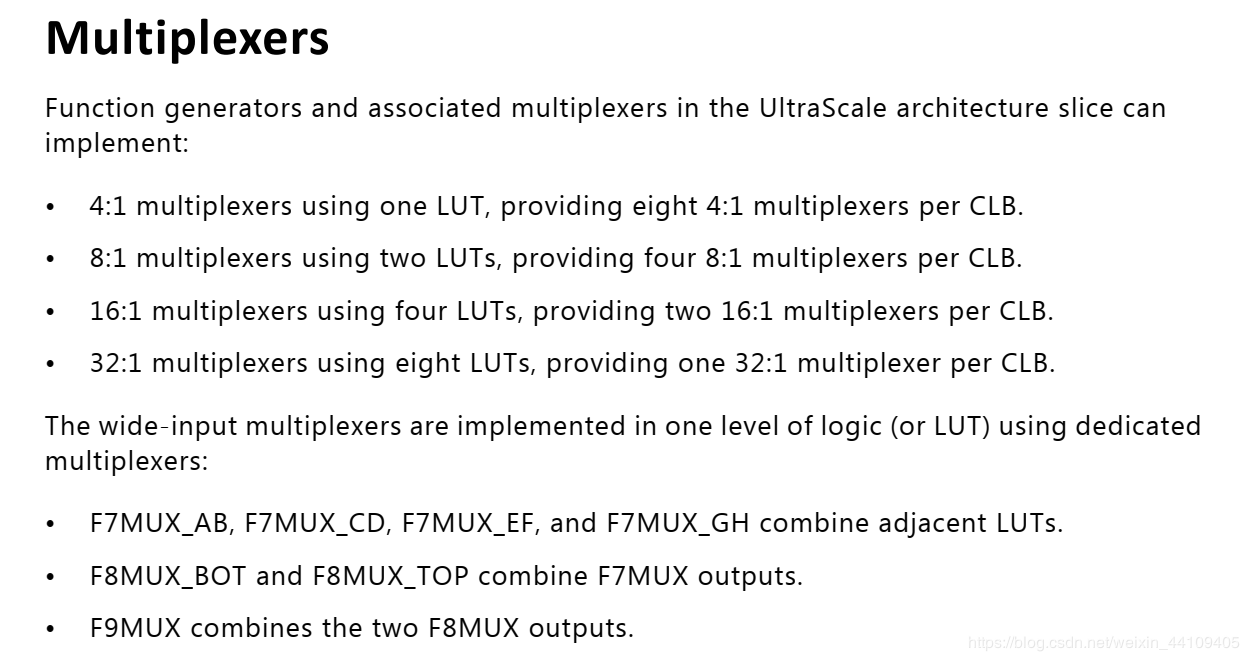

最近用了赛灵思最新UltraScale系列芯片,然后就拿着赛灵思的UG好好研究了一番。发现这个这个系列的FPGA跟ZYNQ相比有了改变,原来ZYNQ是一个CLB包含2个SLICE,然后每个SLICE同时又包含4个6输入LUTS。ZYNQ里面的SLICE包含SLICEL和SLICEM,SLICEL只能做ROM,而SLICEM可以做ROM也可以做RAM,同时也可以完成移位寄存器等功能。但是UltraScale系列芯片里面他是这么描述的。一个CLB包含一个SLICEL或者SLICM。一个SLICE包含8个LUT。所以SLICEL和SLICEM不在成对出现,所以数量不相等也是可能的。同时可以看到在多路复选器中出现了F9。这是因为每个SLICE有8个LUT,如果实现级联就需要4个F7,2个F8和1个F9。

所以可以看到这样的架构就可以实现32:1的功能。

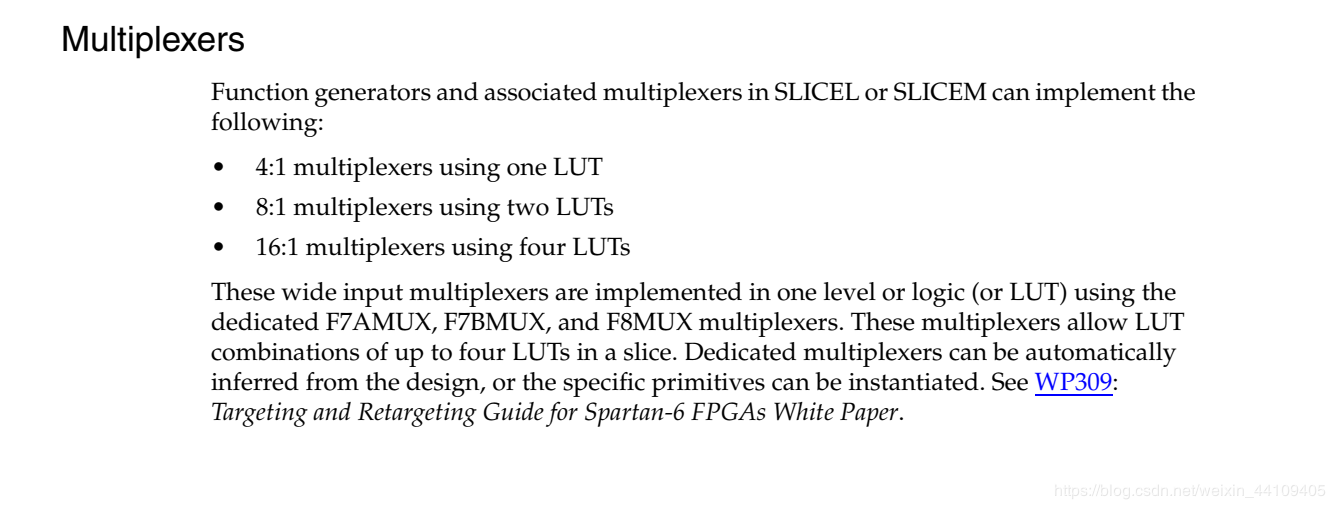

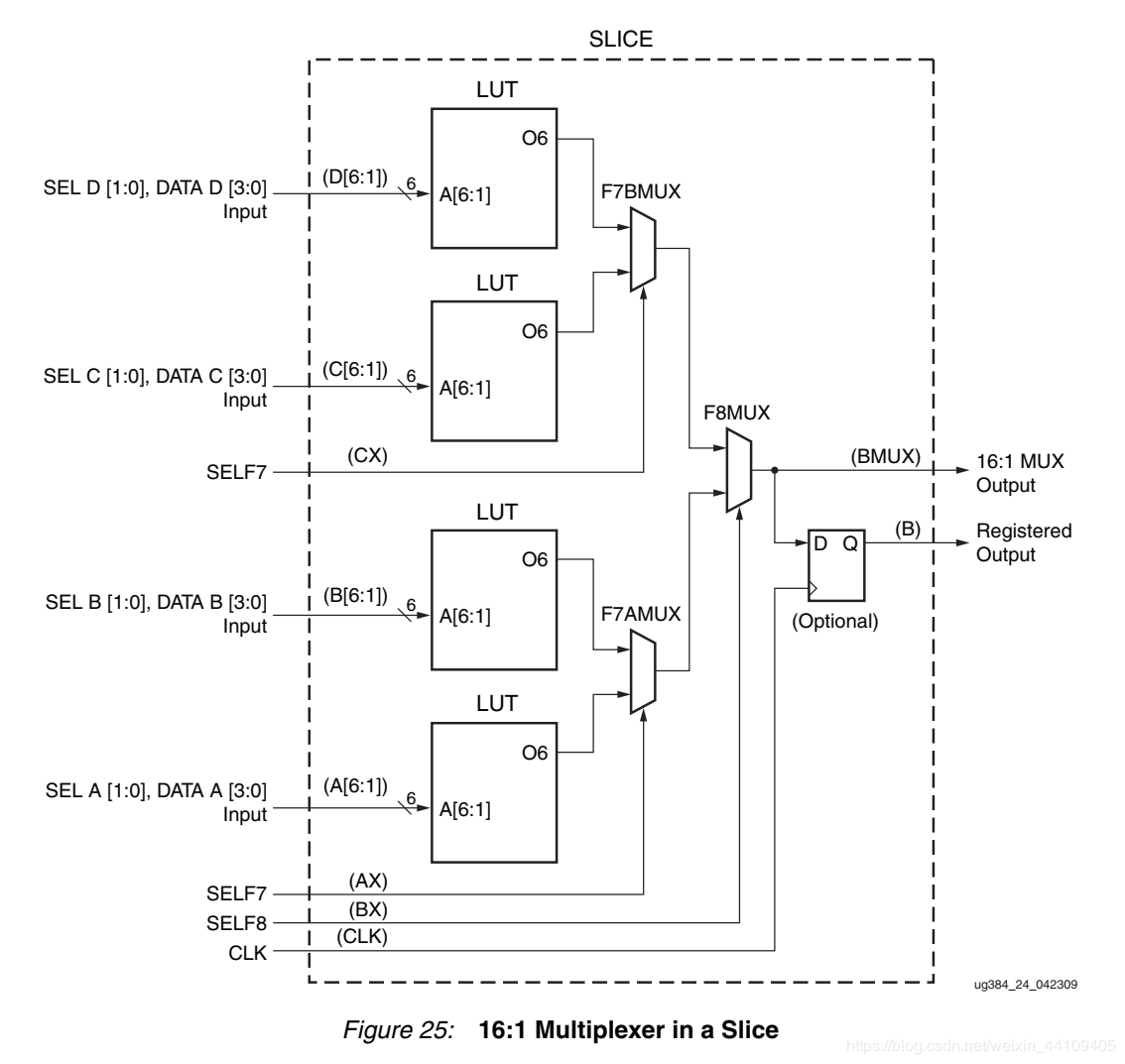

而原先的架构一个SLICE只能实现最多16:1的功能。

或许你会说,他一个CLB包含有2个SLICE,但是要实现32:1的功能他必然还需要一个SLICE去实现F9的功能。

再来两张32:1和16:1的图片。

以上是博主的一些见解,如有问题欢迎回复指正,共同交流。

版权声明:本文为CSDN博主「红色闪电007」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_44109405/article/details/103507418