作者:猫叔 来源:科学计算technomania微信公众号

Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。

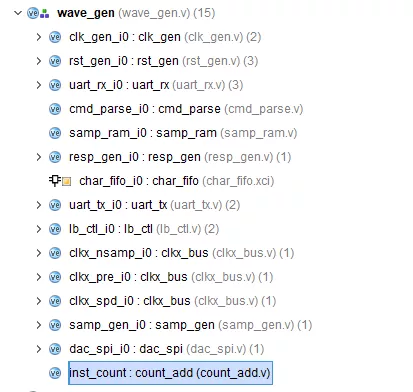

这里我们使用的Vivado版本是2017.2,使用的例程是Vivado自带的wavegen工程,并在工程中增加一个计数器模块,如下图所示

这个模块的代码也很简单,就是加1计数

module count_add(

input clk,

input rst,

output reg [7:0] res

);

always @ (posedge clk ) begin

if(rst)

res <= 8'b0;

else

res <= res + 1'b1;

end

endmodule

我们要把这个模块当做Reconfiguration Module,把它替换成另外一个module: count_sub,就是每个周期减1计数。

module count_sub(

input clk,

input rst,

output reg [7:0] res

);

always @ (posedge clk ) begin

if(rst)

res <= 8'b0;

else

res <= res - 1'b1;

end

endmodule

下面开始进行Partial Reconfiguration的配置

首先打开工程,并将其中一个Reconfiguration Module添加到工程中即可,这里我们选择将count_add添加到工程中,选择Tools->Enable Partial Reconfiguration

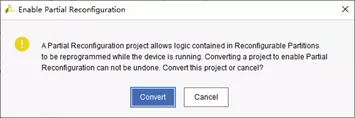

出现下面的对话框,点击Convert。该对话框是指如果使能了Partial Reconfiguration模式,是不能返回到普通模式的。

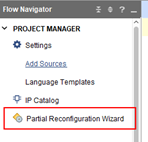

此时在Flow Navigator的PROJECT MANAGER下面就会出现Partial Reconfiguration Wizard的选项

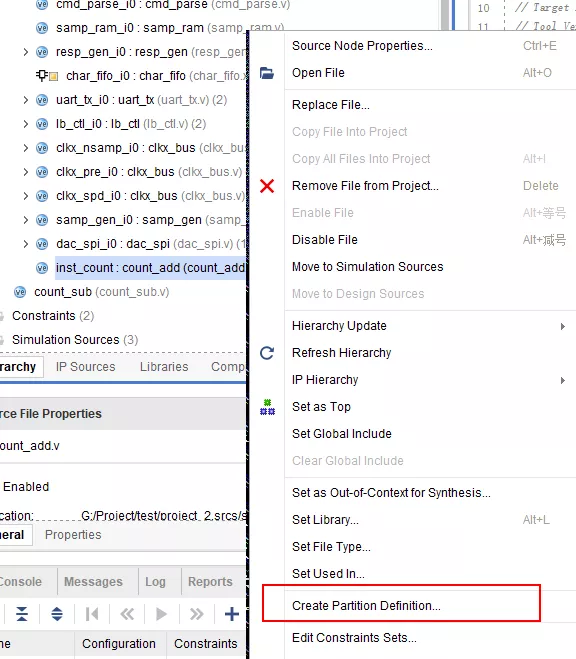

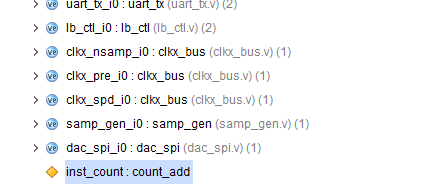

右键要reconfiguration的模块,即inst_count,并选择Create Partition Definition

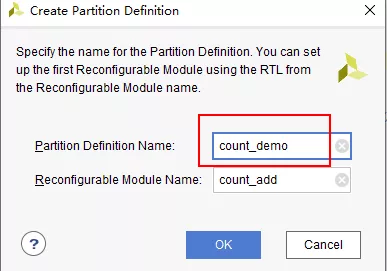

此时,弹出对话框提示我们输入创建的Partition的名字,我们起名为count_demo,点击OK

这时我们可以看到该模块的图标发生了变化,变成了黄色的棱形,如下图所示

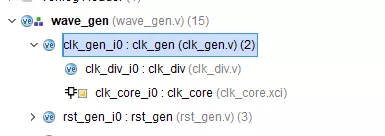

在这一步我们需要提醒一下,通常我们需要进行PR的模块都是比较复杂的模块,里面很可能会包含IP Core,那样的话我们就不能直接这样操作,比如我们要对该工程中的clk_gen_i0模块进行PR,可以看到,这个模块中包含了clk_core_i0这个IP

当我们在clk_gen_i0这个模块上右键选择Create Partition Definition时,会提示下面的对话框:

module with out-of-context child module cannot be made into partition definition

这个意思是包含有ooc子模块的模块,是不能做成partiton的,Vivado中所有的IP Core都是ooc的模块,因此我们需要把clk_gen_i0这个模块导出成dcp后再使用,具体可以参考我的另一篇文章。

Vivado中模块封装成edif和dcp

简单来讲,就是先将这个模块设为top,综合后导出dcp,使用的tcl脚本是

write_checkpoint -noxdef

我看网上也有的教程是直接对整个工程进行综合,然后单独导出RM模块的dcp,使用下面的tcl

write_checkpoint -cell

。

另一点需要注意的是,如果使用了dcp文件,我们也添加一个wrapper.v到工程中,因此dcp文件是不能直接进行Create Partition Definition操作的。

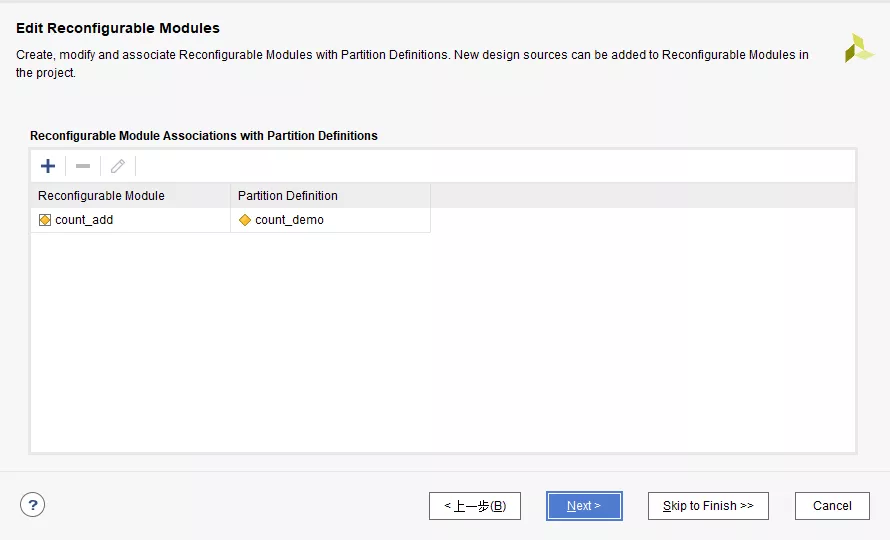

选择左侧导航栏的Partial Reconfiguration Wizard,开始添加RM

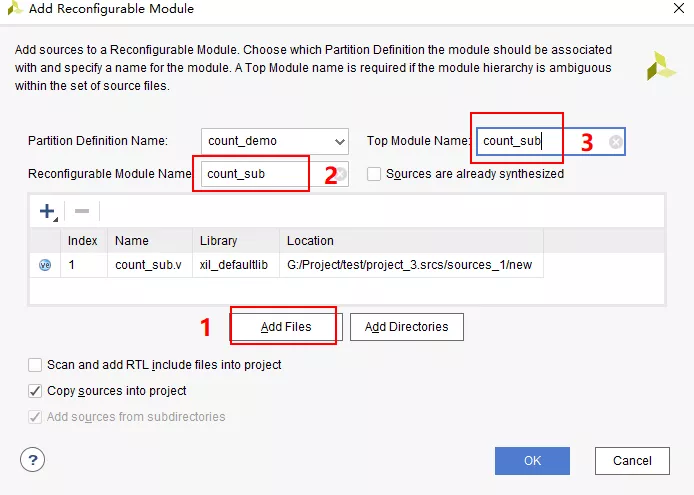

这里,点击+号按钮,出现下面对话框,首先点击Add Files,选择count_sub.v;然后输入Reconfiguration Module Name,由于我们只有一个模块,因此top的name可以不填;如下图,Next

在这一步如果我们使用dcp文件和wrapper文件的话,需要把它们都添加进来

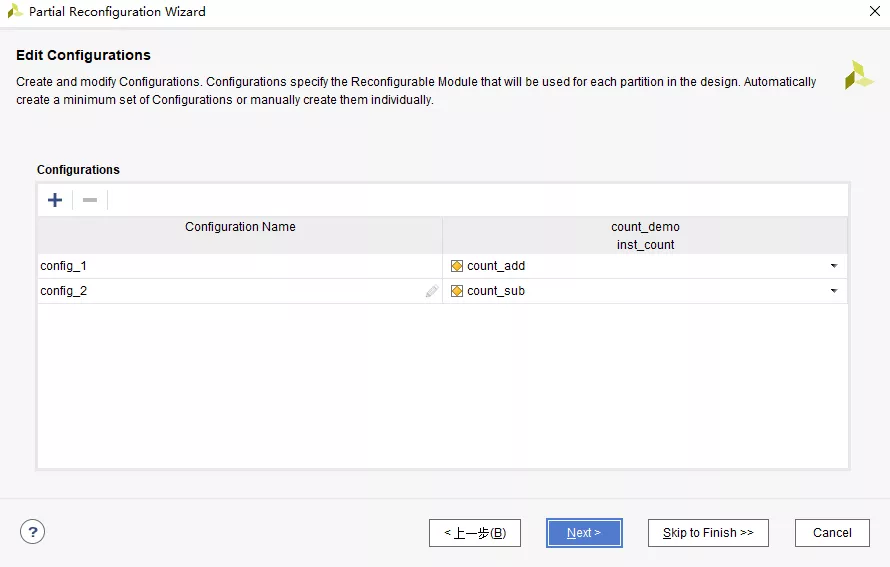

编辑配置,点击automatically create configurations,如果在这个界面没看到这个auto…按钮,就先返回到上一步,再next到这个界面,总会出现的;点击后出现下面的界面:

我们修改配置的名字如下,next

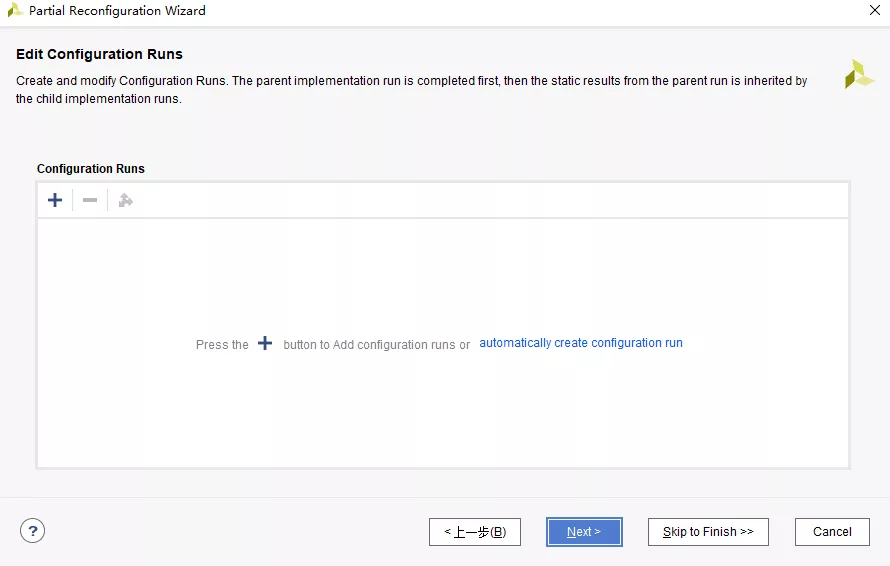

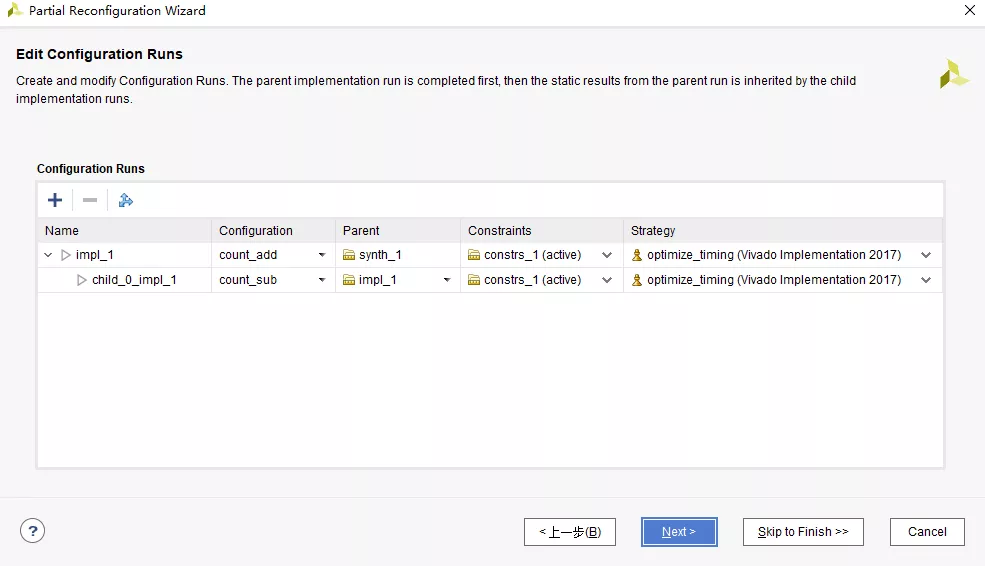

配置runs,也是先点击automatically create configuration run

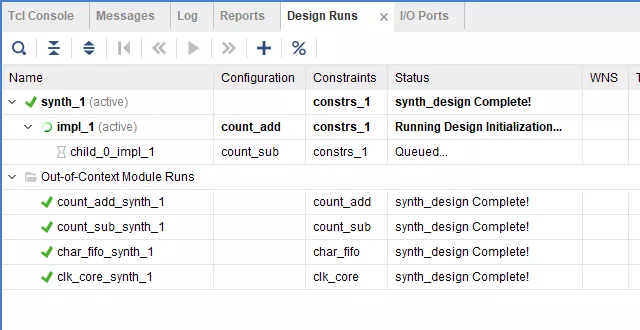

这个图意思是工程中有两个implention runs,第一个叫impl_1,这个里面跑的是包含有count_add模块的程序;第一个叫child_0_impl_1,这个里面跑的是包含count_sub模块的程序。Next到Finish。

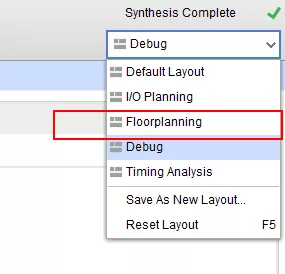

开始综合,完成后点击Open Synthesized Design,并在Vivado右上角,切换到Floorplanning视图

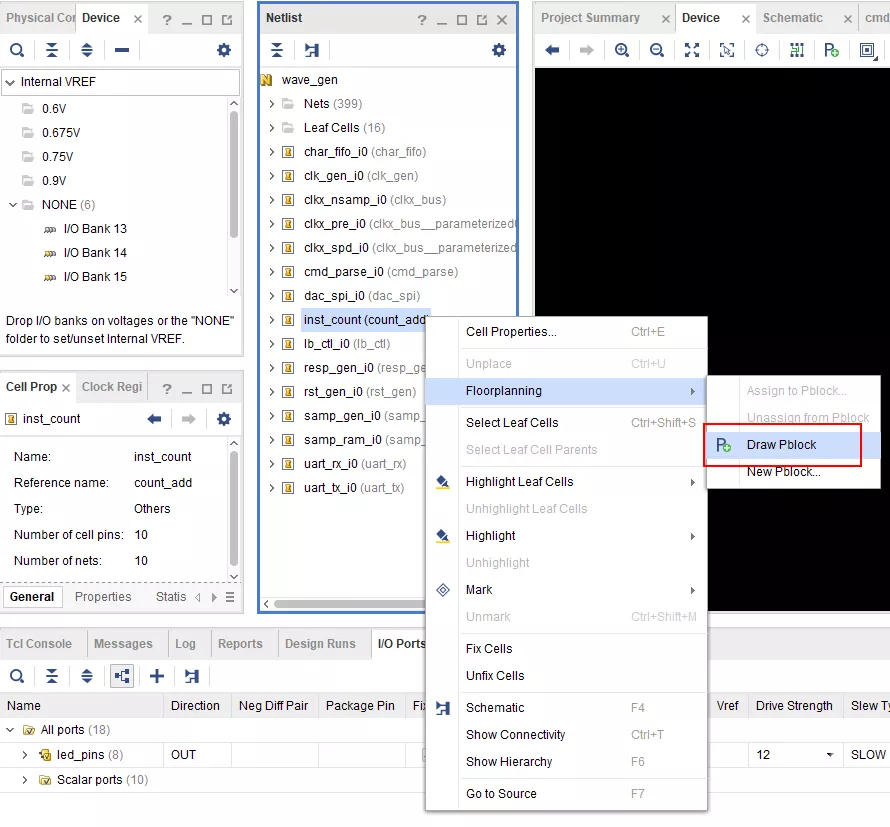

邮件inst_count并点击Draw Pblock

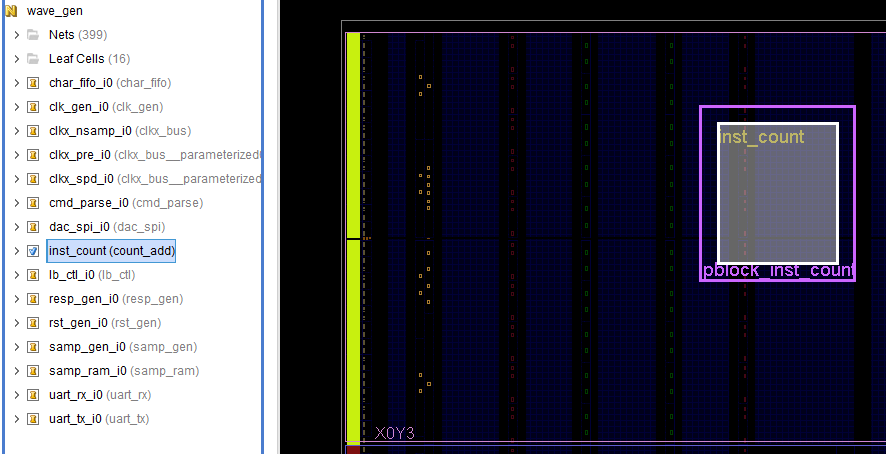

选择一个区域作为Pblock

绘制Pblock是有讲究的,其中最简单的两个规则就是:

当然,还有很多其他的规则,这里就不一一介绍了,如果Pblock没画好,很可能导致后面的DRC和Implementation不过。

关于该更多Pblock的说明,可以参考UG909手册UG909

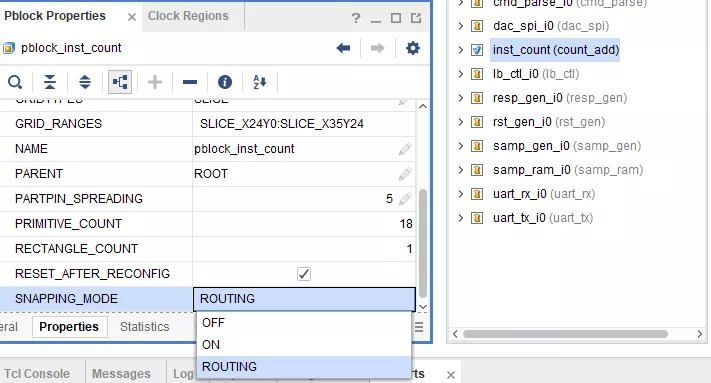

选中框之后,改一下框的属性,将RESET_AFTER_RECONFIG的勾选中,意思是重新配置后,会复位这个Pblock里面的内容;再将SNAPPING_MODE改为Routing(或者设为On),意思是如果我们的边界选的不太好,Vivado会自动处理,选off的话,就是完全按照我们指定的边界。

点击Tools->Report->Report DRC

只选择PR即可

如果提示No Violations Found,则说明上面的操作过程没有问题。

Run Implementation,可以看到有两个runs需要进行

补充小知识:Vivado中jobs和threads的区别?选择多个jobs能加快实现速度么?

Generate Bitstream,OK

在这一步进行前,Vivado会自动执行pr_verify,并生成

对于7系列的FPGA,会在impl_1文件夹下生成两个bit文件:

wave_gen.bit和inst_count_count_add_partial.bit,第一个bit文件是整个工程且包含count_add模块的bit文件,第二个bit文件是当我们需要进行Partial Reconfiguration的时候需要下载的bit文件;在child_0_impl_1文件夹下会生成一个bit文件inst_count_count_sub_partial.bit,是当我们需要进行Partial Reconfiguration的时候需要下载的bit文件。

对于UltraScale系列的FPGA,会在生成*_partial.bit的同时多出来一个*_partial_clear.bit,意思是在进行Partial Reconfiguration的时候,先下载*_partial_clear.bit把那一部分的内容先清空,再下载*_partial.bit进行配置。

使用Project模式的好处就是比较简单,敲的指令也比较少,如果是Non-Project模式,在这中间还需要很多操作,虽然麻烦,但对我们理解它的工作模块很有帮助,有兴趣的同学可以再用Non-Project模式下操作一遍。