本文转载自:Joker-han的博客

本例程主要使用Vivado 调用ROM IP核,用含有正弦曲线的.coe文件初始化ROM,最终通过仿真实现波形的显示。

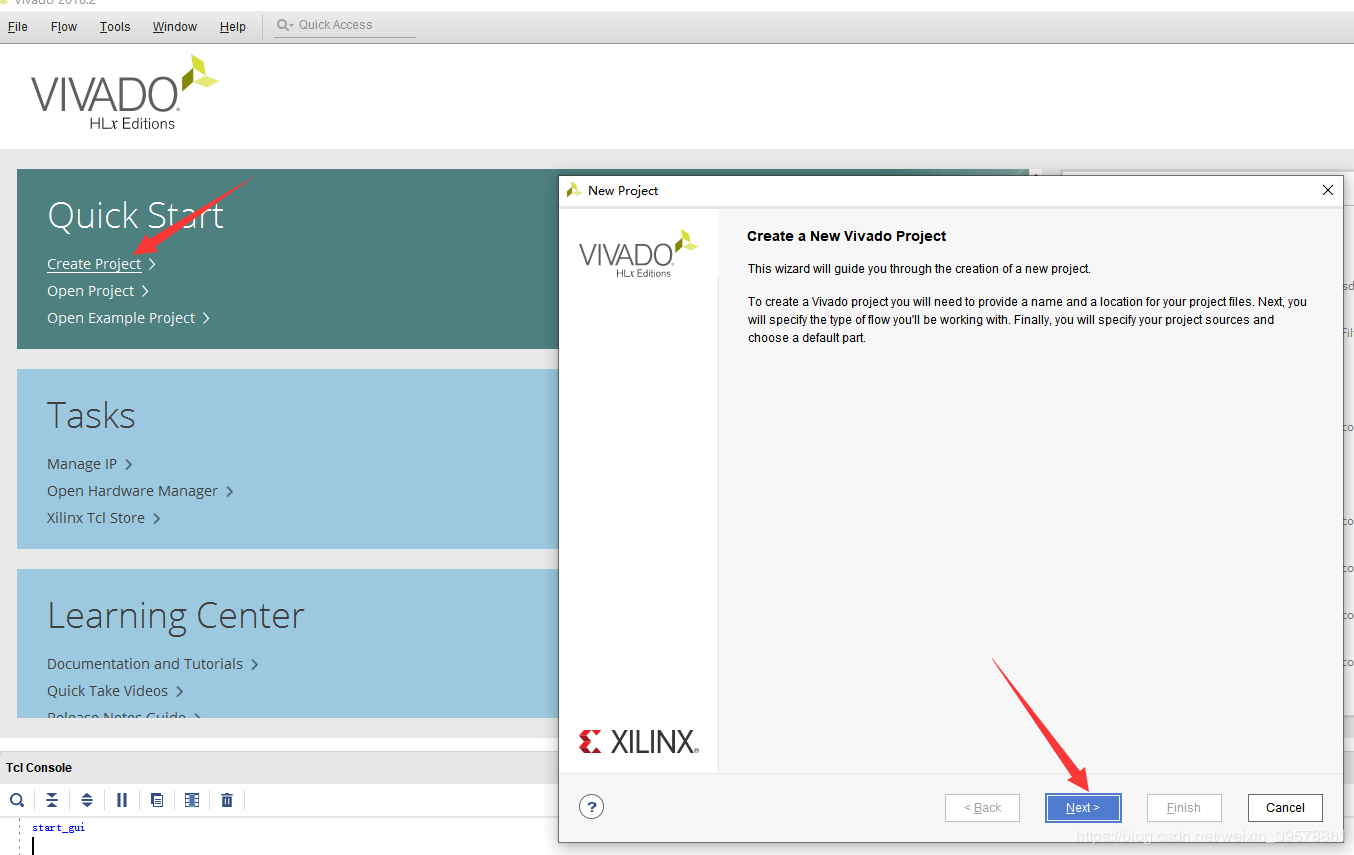

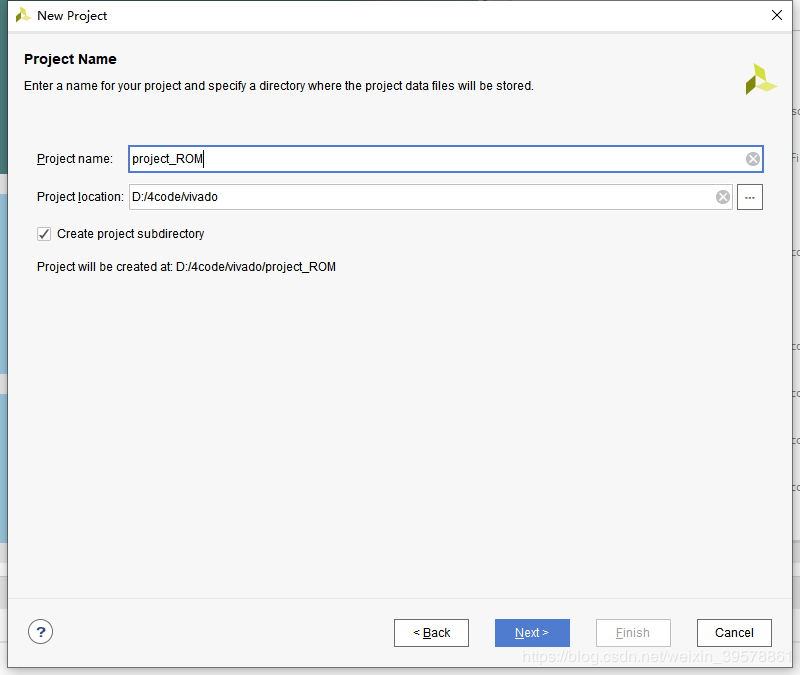

一、首先建立工程

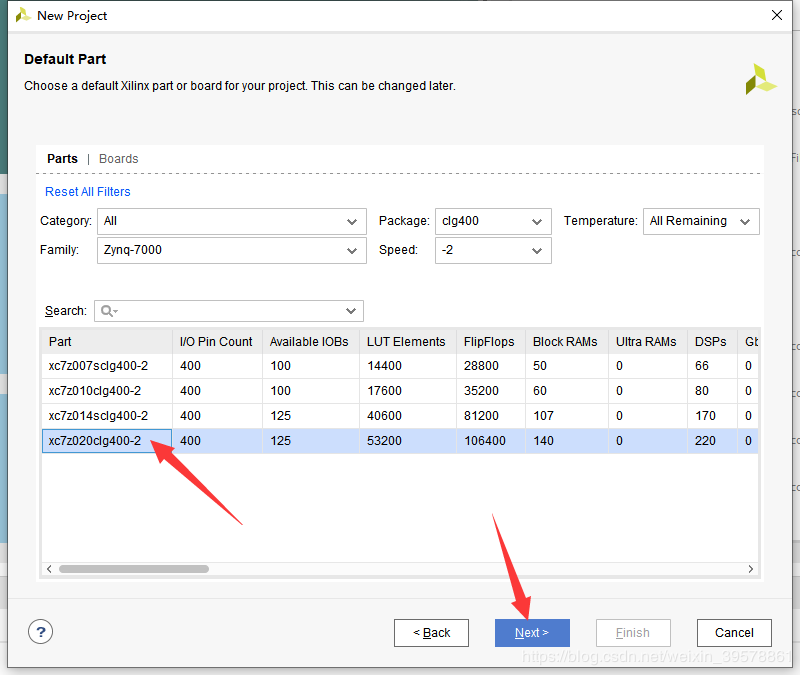

二、选择芯片的型号

我使用的是zynq7020

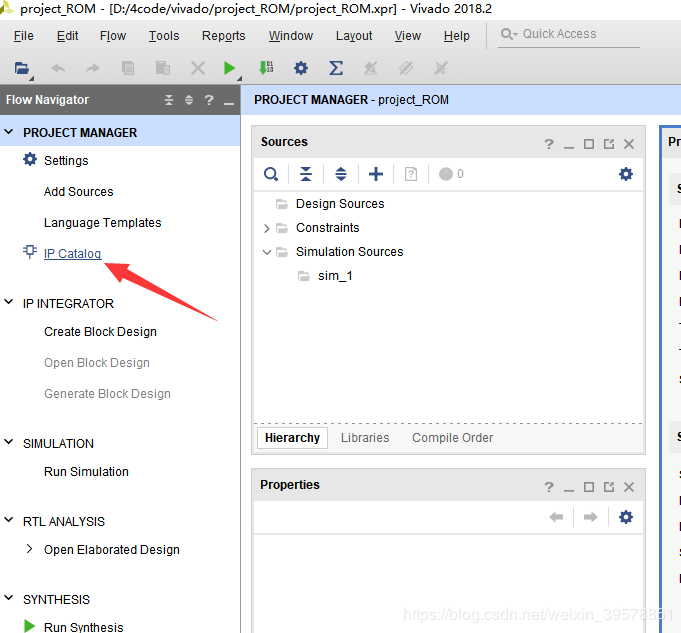

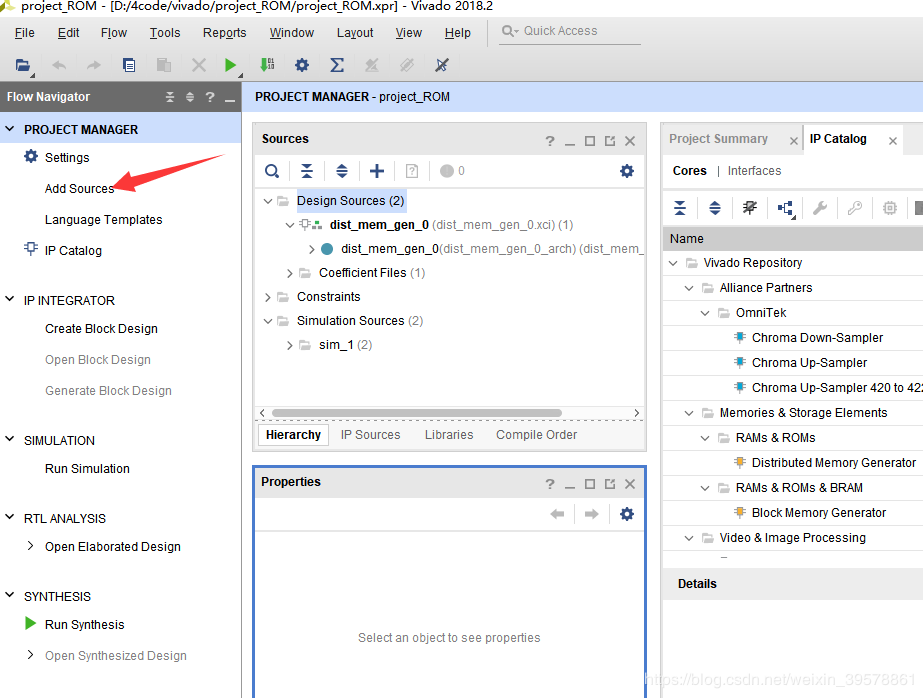

三、调用ROM IP核 这里选择Distributed Memory Generate

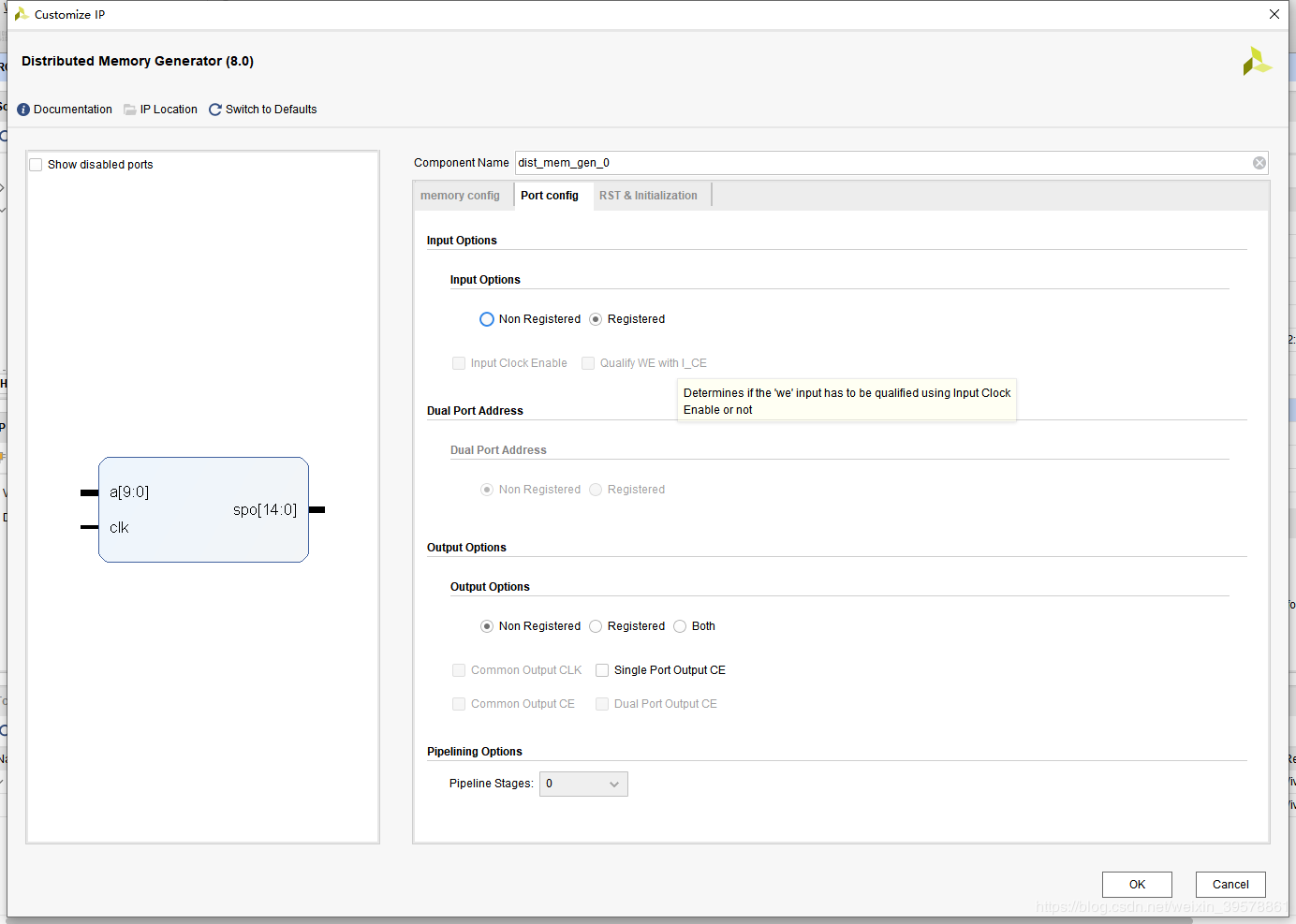

四、打开IP核,进行IP核设置

这里根据初始化文件内容选择所需要的深度和位宽,我们这里选用深度1024,因为文件中有900个数据,数据的宽度我们选择15位

这里将准备好的.coe文件加入ROM中,.coe用我上个博客里面的程序生成 https://blog.csdn.net/weixin_39578861/article/details/89646035

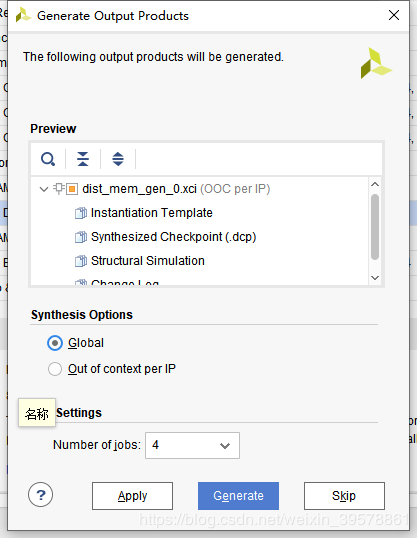

生成IP核

五、添加程序

代码:

`timescale 1ps / 1ps

module sin_lut(

input sclk,

input rst_n,

output q_out

);

parameter DW = 15;

parameter AW = 10;

parameter ADDR_MAX = 900;

parameter CONST_HALF_PI = ADDR_MAX - 1;

parameter CONST_PI = ADDR_MAX * 2 - 1;

parameter CONST_DOUBLE_PI = ADDR_MAX * 4 - 1;

reg [AW-1:0] address;

wire [DW-1:0] data;

wire [DW-1:0] q_data;

wire [DW-1:0] q_out;

reg [AW+2-1:0] address_tmp;

reg [DW+1-1:0] data_tmp;

dist_mem_gen_0 rom1 (

.a(address), // input wire [9 : 0] a

.clk(sclk), // input wire clk

.spo(data) // output wire [13 : 0] spo

);

always @ (posedge sclk or negedge rst_n)

if(!rst_n)

address_tmp <= {AW+2{1'b0}};

else if(address_tmp == CONST_DOUBLE_PI)

address_tmp <= {AW+2{1'b0}};

else

address_tmp <= address_tmp + 1;

always @ (posedge sclk or negedge rst_n)

if(!rst_n)

address <= {AW{1'b0}};

else if(address_tmp <= CONST_HALF_PI)

address <= address_tmp[AW-1:0];

else if(address_tmp <= CONST_PI)

address <= CONST_PI - address_tmp;

else if(address_tmp <= (CONST_PI + CONST_HALF_PI))

address <= address_tmp - CONST_PI;

else if(address_tmp <= CONST_DOUBLE_PI)

address <= CONST_DOUBLE_PI - address_tmp;

always @ (posedge sclk or negedge rst_n)

if(!rst_n)

data_tmp <= 1'b0;

else if(address_tmp <= CONST_PI)

data_tmp <= {1'b0,data};

else if(address_tmp <= CONST_DOUBLE_PI)

data_tmp <= {DW+2-1{1'b0}} - {1'b0,data};

assign q_out = data_tmp[DW-1:0];

endmodule

ROM例化文件的方法:点击IP Sources 按照如图所示即可

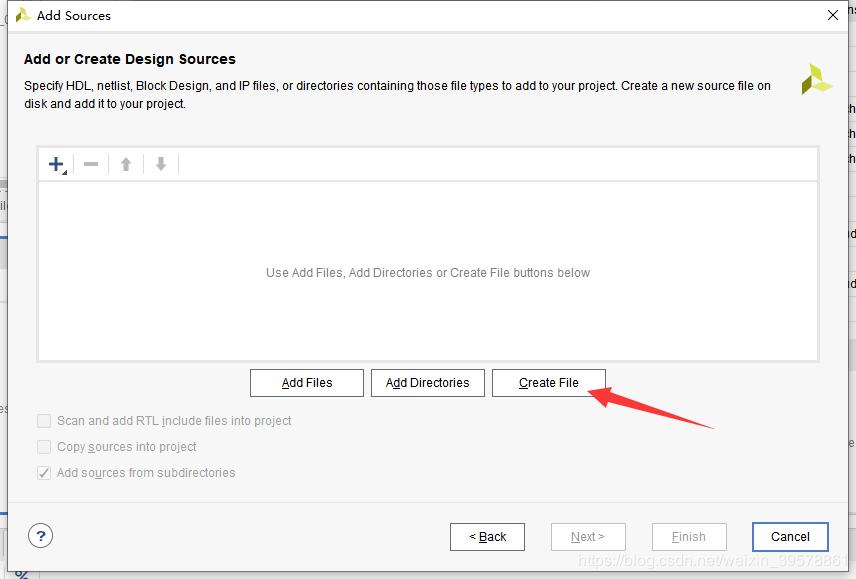

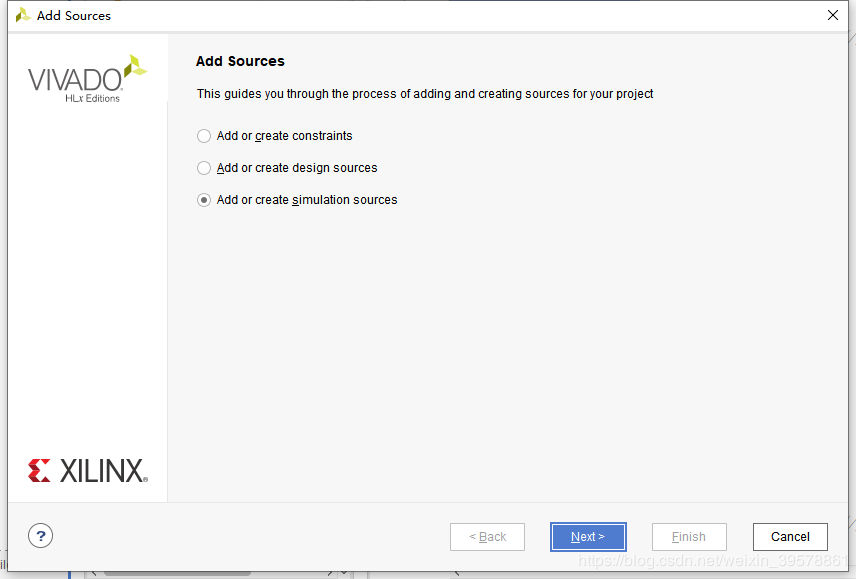

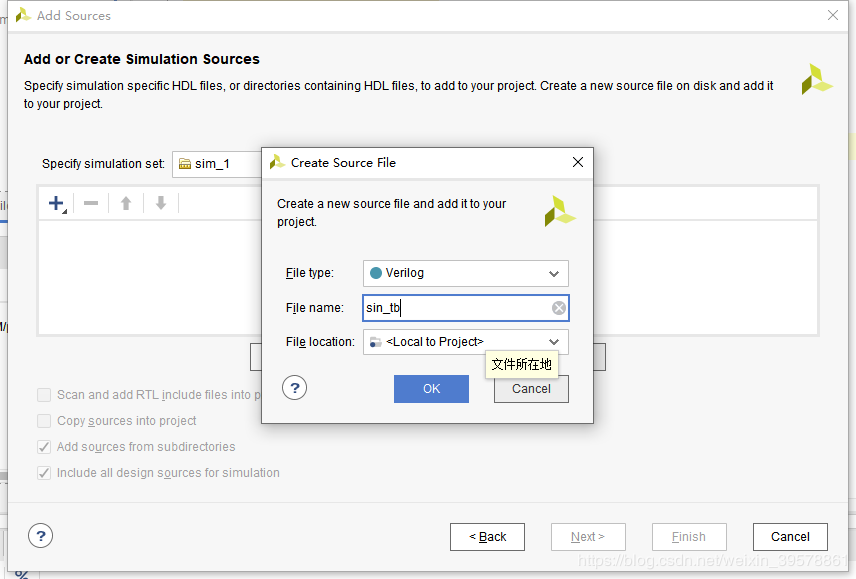

六、测试文件:

代码

`timescale 1ps / 1ps

module sin_tb;

parameter DW = 15;

reg sclk;

reg rst_n;

wire [DW-1:0] q_data;

initial begin

#50 sclk <= 1'b0;

#50 rst_n <= 1'b0;

#50 rst_n <= 1'b1;

end

always #50 sclk = ~sclk;

sin_lut sin(

.sclk(sclk),

.rst_n(rst_n),

.q_out(q_data)

);

endmodule

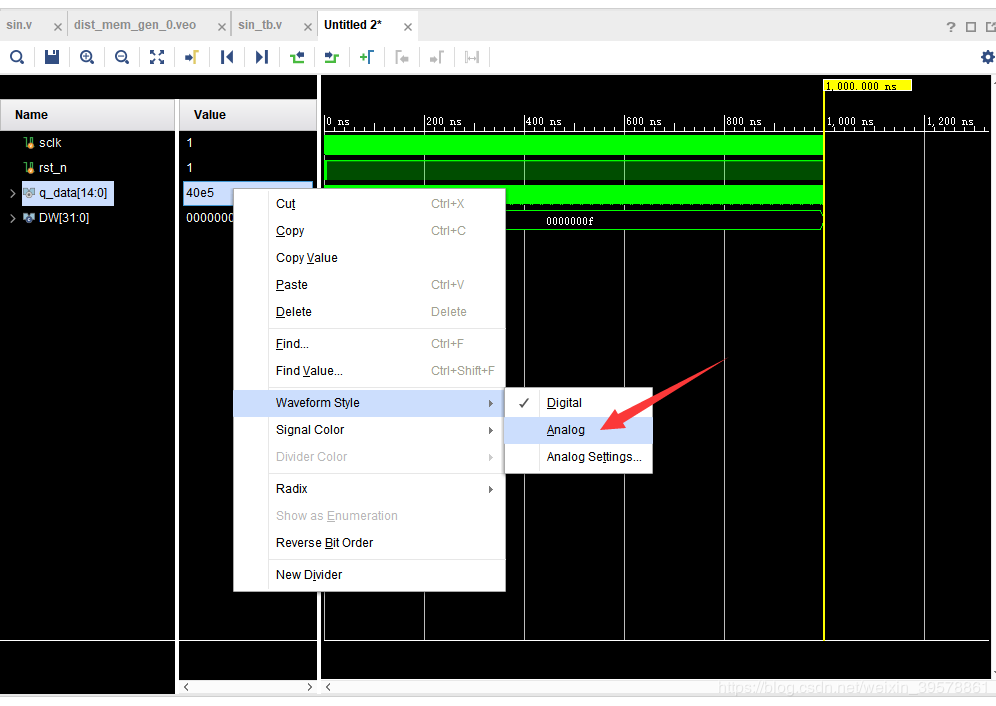

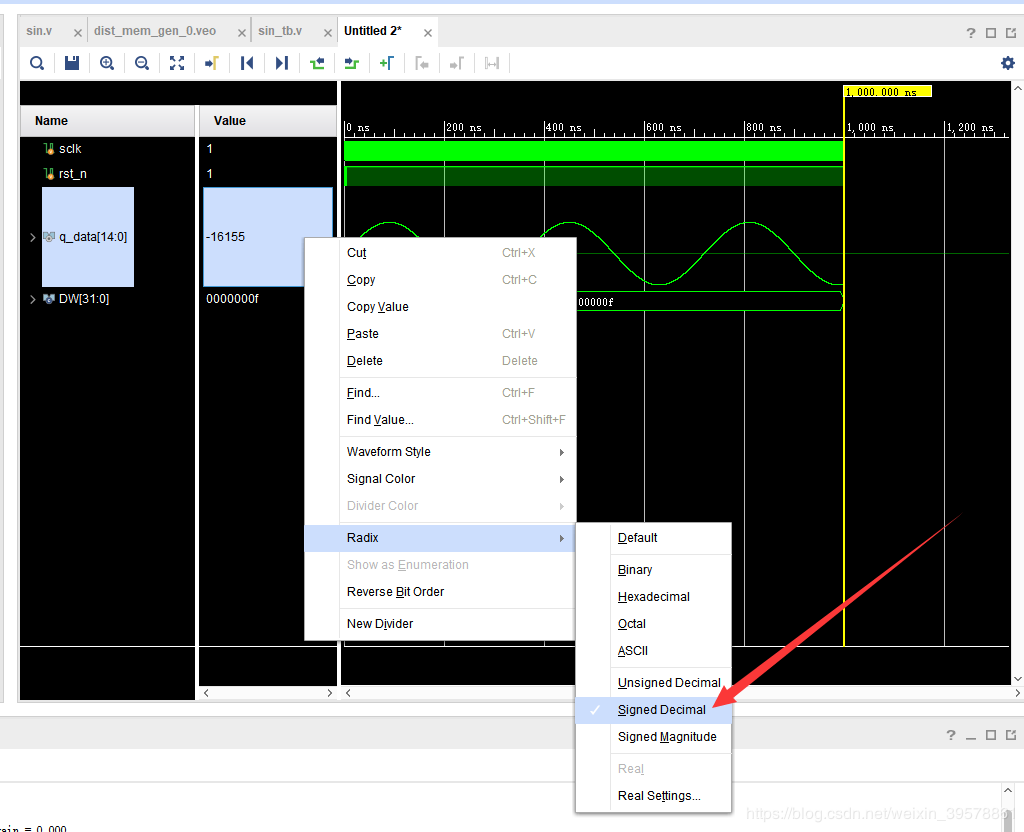

七、仿真波形