作者:小墨,文章转载自:ZYNQ微信公众号

SPI 总线控制器支持与各种外设通信,例如存储器、温度传感器、压力传感器、模拟转换器、实时时钟、显示器和任何支持串行模式的SD卡等等。

SPI 控制器可以在主模式、从模式或多主模式下工作。Zynq-7000 器件包括两个 SPI 控制器,该控制器基于 Cadence SPI 内核。

在主模式下,控制器驱动串行时钟和从选择,并提供支持 SPI 多主模式的选项。串行时钟源自 PS 时钟子系统,控制器使用最多 3 个可外部扩展的独立从站选择 (SS) 输出信号启动消息,控制器通过向 32 位读/写数据端口寄存器写入字节来读取和写入从设备。

在多主模式下,控制器在控制器未激活时将其输出信号设为三态,并在启用时检测错误。通过复位 SPI 使能位,输出立即变为三态,中断状态寄存器指示模式故障。

在从机模式下,控制器从外部设备接收串行时钟,并使用 SPI_Ref_Clk 同步数据捕获,从模式包括一个可编程的启动检测机制,当控制器被启用而 SS 被断言时。

读和写 FIFO 在 SPI I/O 接口和通过 APB 从接口为控制器提供服务的软件之间提供缓冲, FIFO 用于从设备和主设备 I/O 模式。

控制器有什么特点

每个 SPI 控制器都是独立配置和控制的,它们包括以下功能:

四线总线 – MOSI、MISO、SCLK 和 SS

多达 3 个从选择用于主模式

全双工操作提供同步接收和发送

通过 APB 从接口进行 32 位寄存器编程

用于 Rx/Tx FIFO 的存储器映射读/写数据端口(字节宽)

128 字节读取和 128 字节写入 FIFO

可编程 FIFO 阈值状态和中断

主 I/O 模式

手动和自动启动数据传输

手动和自动从选择 (SS) 模式

从站选择信号可直接连接从站设备或外部扩展

可编程 SS 和 MOSI 延迟

从机 I/O 模式

可编程启动检测模式

多主 I/O 能力

如果控制器未启用,则将 I/O 缓冲器驱动为三态

当检测到另一个主机时产生模式故障中断

当 I/O 信号路由到 MIO 引脚时,50 MHz SCLK 时钟频率

当 I/O 信号通过 EMIO 接口路由到 PL 引脚时为 25 MHz SCLK

可编程时钟相位和极性(CPHA、CPOL)

可编程中断驱动设备或轮询状态

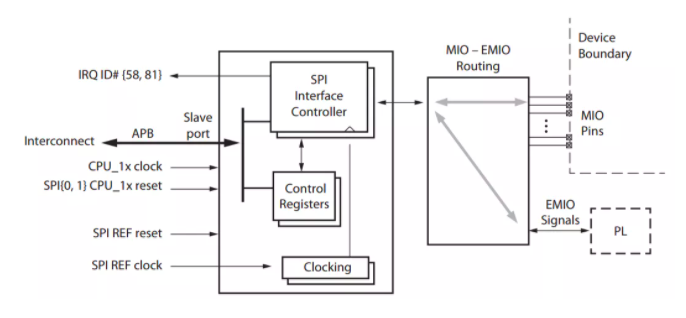

系统视图

SPI 控制器的系统视点图如图所示。

SPI接口控制器

有两个独立的 SPI 接口控制器(SPIx;其中 x = 0 或 1),每个独立控制器的 I/O 信号可以路由到 MIO 引脚或 EMIO 接口,每个控制器也有单独的中断信号到 PS 中断控制器和一个单独的复位信号, 每个控制器都有自己的一组控制和状态寄存器。

时钟

PS 时钟子系统为 SPI 控制器提供参考时钟, SPI_Ref_Clk 时钟用于控制器逻辑并由波特率发生器用于为主模式创建 SCLK 时钟。

MIO-EMIO

SPI I/O 信号可以路由到 MIO 引脚或 EMIO 接口到 PL。

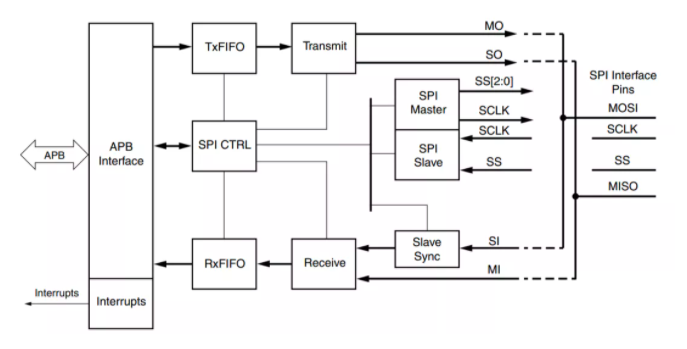

功能模块框图

SPI 控制器的功能框图如图所示。

APB 从机接口

32 位 APB 从接口响应寄存器读取和写入,包括用于从 FIFO 读取和写入命令和数据的数据端口,所有寄存器事务都是 32 位的,数据端口使用这些端口的位 [7:0]。配置和状态寄存器列在附录 B,寄存器详细信息中。

SPI 主模式

当控制器工作在主模式时,它驱动SCLK时钟和最多3个从选择输出信号,MOSI上的SS和传输开始可由软件手动控制或由硬件自动控制。

SPI 从模式

当控制器在从模式下运行时,它使用单个从选择输入 (SS 0), SCLK 与控制器参考时钟 (SPI_Ref_Clk) 同步。

Tx 和 Rx FIFO

每个 FIFO 为 128 字节,软件使用寄存器映射的数据端口寄存器读取和写入这些 FIFO。

FIFO 桥接两个时钟域, APB 接口和控制器的 SPI_Ref_Clk,软件写入 APB 时钟域中的 TxFIFO,控制器读取 SPI_Ref_Clk 域中的 TxFIFO。

控制器填充 SPI_Ref_Clk 域中的 RxFIFO,软件读取 APB 时钟域中的 RxFIFO。

小结

本文简单介绍了Zynq的SPI控制器、支持的SPI协议以及如何路由到MIO或EMIO,SPI是串行外设接口(Serial Peripheral Interface)的缩写,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,越来越多的芯片集成了这种通信协议。