作者: 硬码农二毛哥,文章来源: 硬码农二毛哥微信公众号

在zynq开发过程中,AXI总线经常遇到,每次看到AXI总线相关的信号时都一头雾水,仔细研究一下,将信号分分类,发现其实也不难。

AXI 结构

AXI协议通道

• Read address, which has signal names beginning with AR.

• Read data, which has signal names beginning with R.

• Write address, which has signal names beginning with AW.

• Write data, which has signal names beginning with W.

• Write response, which has signal names beginning with B

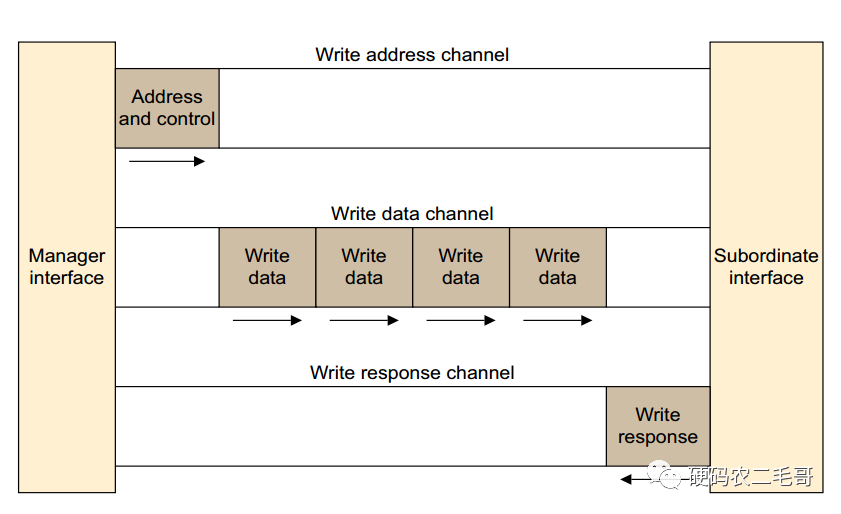

write transaction

使用 write address, write data, and write response channels

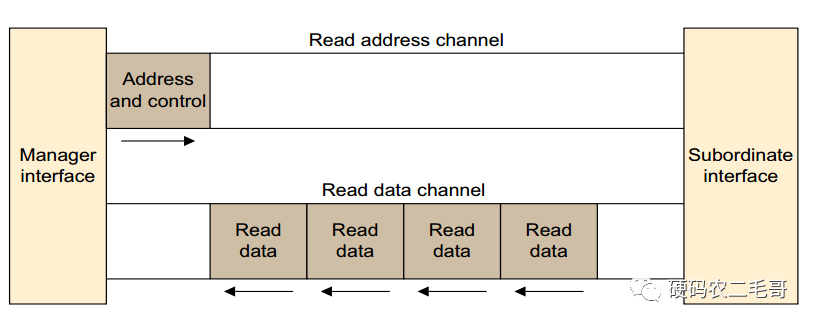

read transaction

使用 the read address and read data channels.

信号描述

时钟和复位

input ARESETN,

input ACLK,

写地址通道信号

output [0:0] M_AXI_AWID,

output [31:0] M_AXI_AWADDR,

output [7:0] M_AXI_AWLEN,

output [2:0] M_AXI_AWSIZE,

output [1:0] M_AXI_AWBURST,

output M_AXI_AWLOCK,

output [3:0] M_AXI_AWCACHE,

output [2:0] M_AXI_AWPROT,

output [3:0] M_AXI_AWQOS,

output [0:0] M_AXI_AWUSER,

output M_AXI_AWVALID,

input M_AXI_AWREADY,

写数据通道信号

output [63:0] M_AXI_WDATA,

output [7:0] M_AXI_WSTRB,

output M_AXI_WLAST,

output [0:0] M_AXI_WUSER,

output M_AXI_WVALID,

input M_AXI_WREADY,

写反馈通道信号

input [0:0] M_AXI_BID,

input [1:0] M_AXI_BRESP,

input [0:0] M_AXI_BUSER,

input M_AXI_BVALID,

output M_AXI_BREADY,

读地址通道信号

output [0:0] M_AXI_ARID,

output [31:0] M_AXI_ARADDR,

output [7:0] M_AXI_ARLEN,

output [2:0] M_AXI_ARSIZE,

output [1:0] M_AXI_ARBURST,

output [1:0] M_AXI_ARLOCK,

output [3:0] M_AXI_ARCACHE,

output [2:0] M_AXI_ARPROT,

output [3:0] M_AXI_ARQOS,

output [0:0] M_AXI_ARUSER,

output M_AXI_ARVALID,

input M_AXI_ARREADY,

读数据通道信号

input [0:0] M_AXI_RID,

input [63:0] M_AXI_RDATA,

input [1:0] M_AXI_RRESP,

input M_AXI_RLAST,

input [0:0] M_AXI_RUSER,

input M_AXI_RVALID,

output M_AXI_RREADY,

Basic read and write transactions

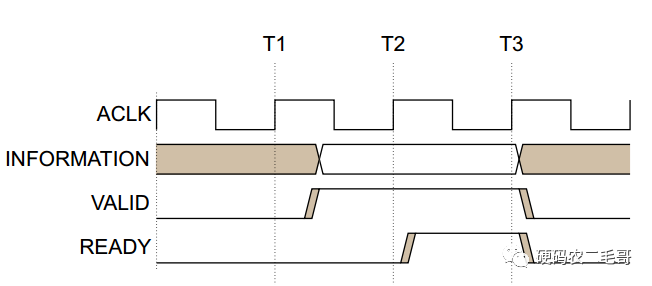

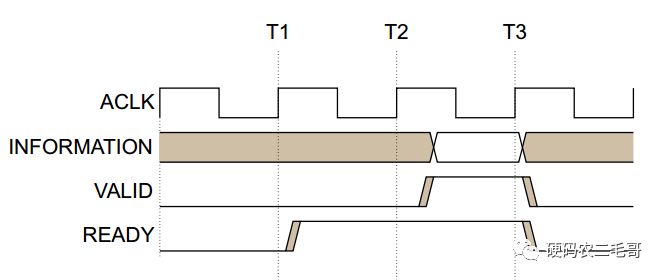

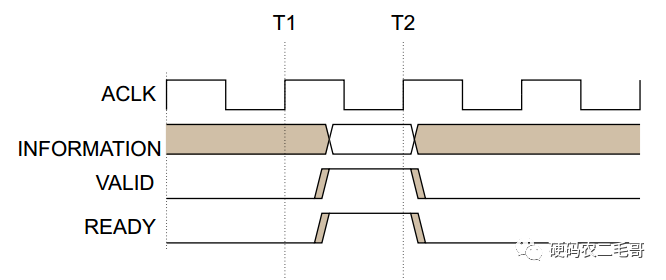

握手过程

每个通道都有VALID/READY 信号,VALID有效时输出地址、数据和控制信息。READY 信号有效表示可以接收信息。只有当VALID和READY 都有效时才可以进行通信。

主机发出VALID,从机发出READY ,当VALID和READY都为高时,握手成功。

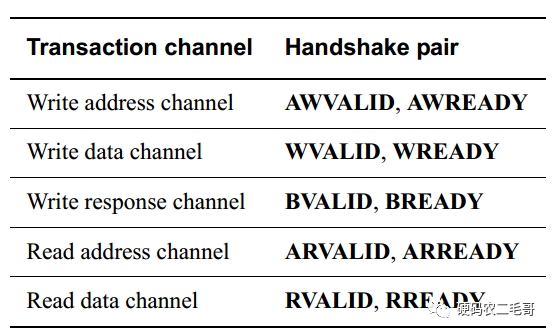

通道握手信号

通道信号要求

write transaction

写地址通道

主机输出有效地址和控制信息时将AWVALID 信号置1,AWVALID 置1后必须等待从机AWREADY 置1。完成写地址操作,进入写数据操作。

写数据通道

在写数据操作时,输出有效数据时将WVALID 置1。WVALID 置1后等待从机WREADY 置1。在写入最后一个数据时,将WLAST信号置1。之后主机等待从机写反馈。

写反馈通道

主机接收到从机发出BVALID信号时,将BREADY 信号置1,接收从机反馈信息。主机BREADY 信号可以默认为1。

以上过程完成主机到从机发送数据流程。

read transaction

读地址通道

主机输出有效地址和控制信息时将ARVALID信号置1,ARVALID 置1后必须等待从机ARREADY 置1。完成读地址操作,进入读数据操作。

读数据通道

当从机输出有效数据时将RVALID置1,RVALID置1后等待主机RREADY置1,从机发送最后一个数据时将RLAST置1。

以上过程完成接收数据流程。