作者: 碎碎思,文章来源: OpenFPGA微信公众号

FPGA高层次综合HLS(一)-Vitis HLS介绍

Vitis HLS介绍及工作流程

高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。

对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

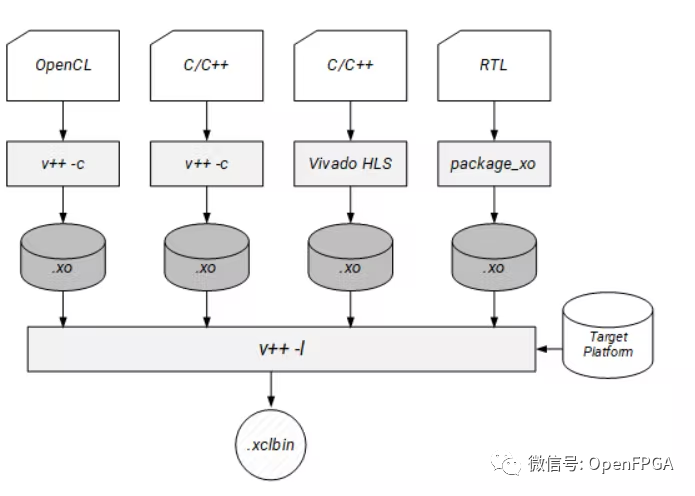

为了创建可编程逻辑内核,Vitis V++ 编译器能够将 OpenCL、C/C++ 和 RTL 编译到AMD Xilinx对象 (.xo) 文件中,然后将它们链接到AMD Xilinx二进制 (.xclbin) 中用于可编程逻辑。

FPGA bit流创建流程

与主机开发流程(正常开发流程)结合使用时,我们可以使用 Vitis IDE 对我们的应用程序进行自上而下的加速。

但是,查看 FPGA bit流创建流程,我们还可以使用 HLS 或 RTL 从下到上创建加速内核。

这种自下而上的流程使我们能够专注于复杂的内核算法,验证其性能并确保可编程逻辑实现过程的优化 途径是最佳的。

这种方法还可以更好地与团队方法一起使用,并且可以创建可跨多个项目使用的加速内核库(IP)。另一个优点是应用于可编程逻辑实现的优化驻留在 .xo 文件中,无需在每次使用算法时重新进行优化。

Vivado HLS 正是为此流程而构建,Vitis HLS包含在 Vitis 安装的 bin 目录中。

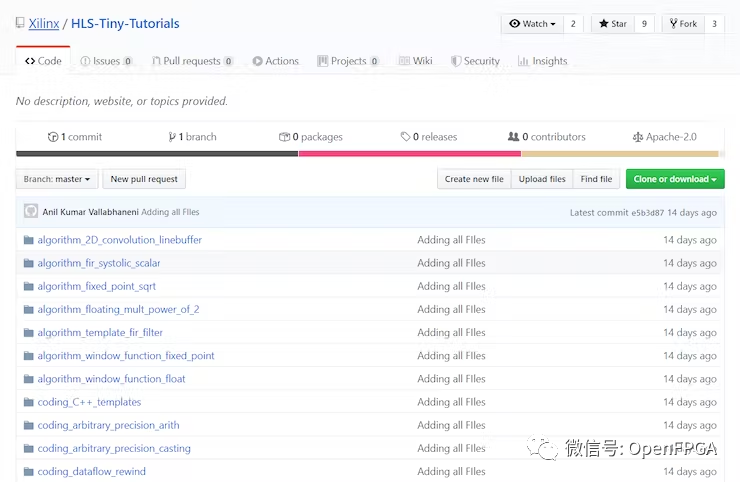

同时Xilinx GitHub (https://github.com/Xilinx/HLS-Tiny-Tutorials)上还有许多 Vitis HLS 教程项目。

GitHub教程

这些教程涵盖了开始开发有效内核所需的一切,包括算法开发、编码风格、接口和内存架构等方面。

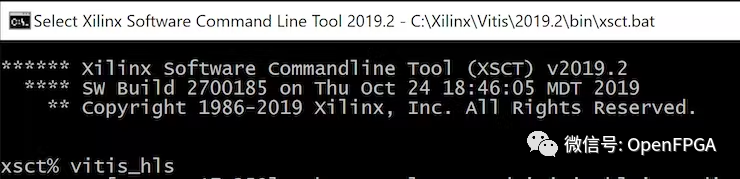

如果我们使用的是 Windows,我们可以通过输入以下命令从 Xilinx 软件命令行工具调用 Vitis HLS:

vitis_hls

在 Linux 系统中,在运行安装目录中的设置脚本settings64.sh后,我们可以在终端窗口中使用相同的命令。

调用Vitis HLS

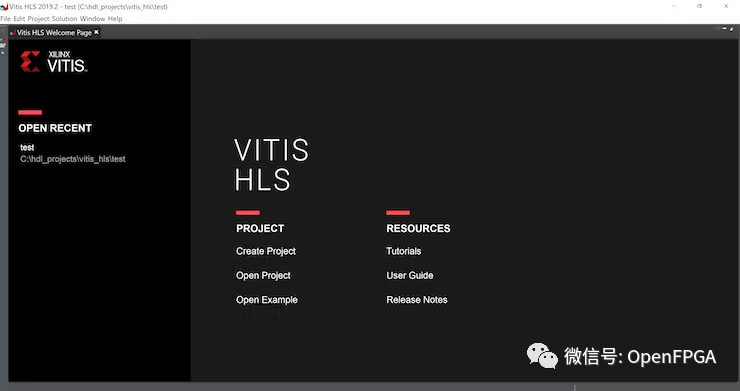

Vitis HLS 加载和欢迎页面。

Vitis HLS 加载和欢迎页面

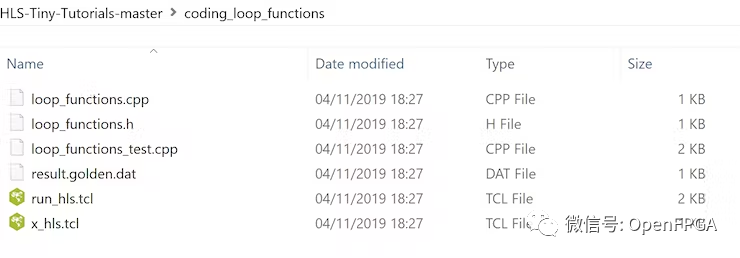

我们可以通过从 GitHub 克隆或下载 ZIP 文件来使用这些示例。如果我们探索一个示例库,我们将找到支持该示例的源代码和 TCL 文件。

循环函数示例的内容

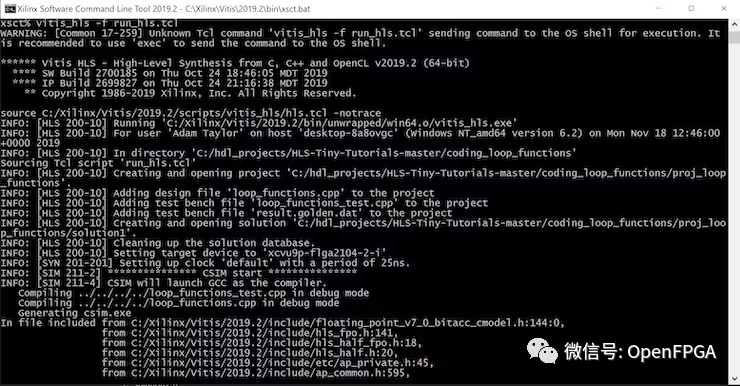

我们可以通过切换到该目录并从 Linux 终端或 XSCT (windows)运行这些示例:

vitis_hls -f run_hls.tcl

这将以命令行模式运行该项目并综合。

运行Vitis HLS示例

命令运行完成后,将看到一个包含解决方案和项目文件的新目录(Vitis HLS工程)。

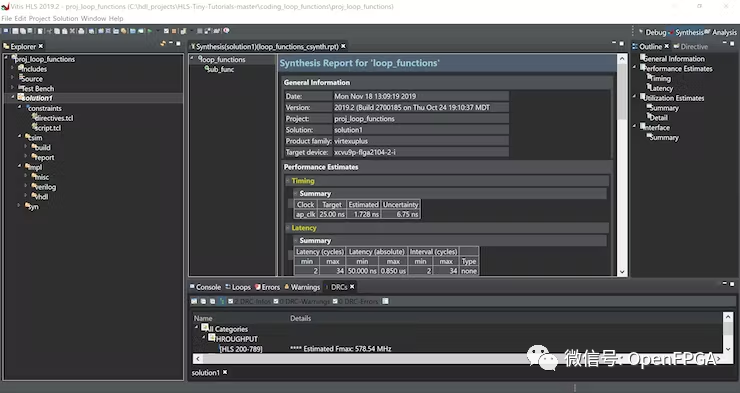

要探索设计,我们可以使用已打开的 Vitis GUI 导航到示例项目目录。

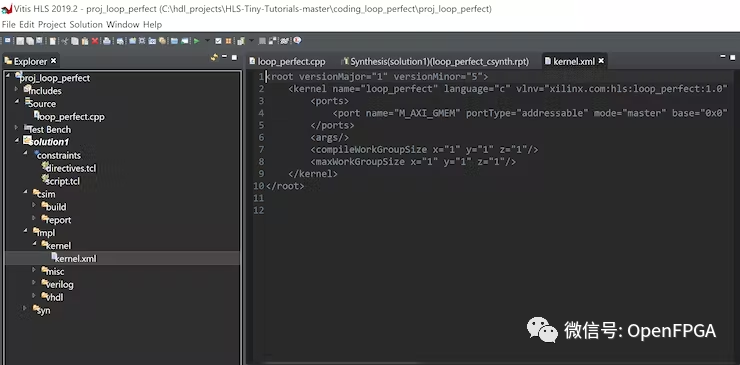

打开 GUI 后,将看到一个基于 Eclipse 的工作区,它看起来类似于 Vivado HLS,但存在细微差别。

Vitis HLS图形界面

在 GUI 中,我们可以浏览综合报告、调试应用程序并分析RTL的实现。

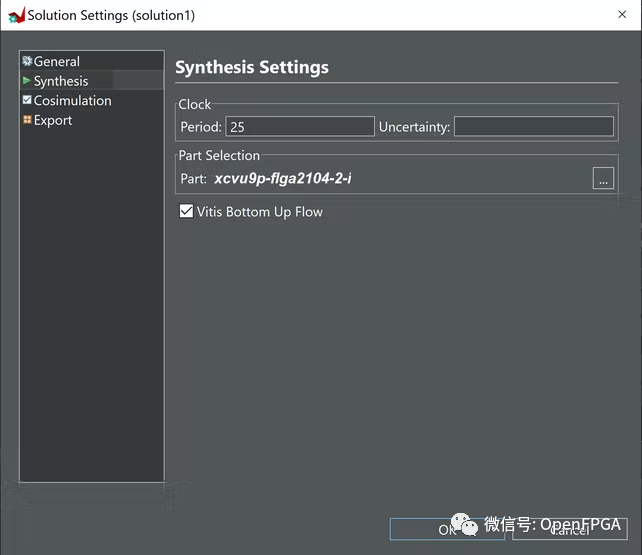

默认情况下,实现过程将设置为生成基于 RTL 的解决方案,但如果我们希望使用自下而上的流程,并在 Vitis 中实现加速功能并生成 Xilinx 对象,我们应该怎么做?

我们可以检查解决方案设置下的选项- Vitis 自下而上设计。

设置Vitis HLS自下而上流程

当我们接下来执行综合时,我们不仅会看到 Verilog 和 VHDL 实现,还会看到包含内核描述的 XML 文件。

一旦我们对算法的性能感到满意,我们就可以导出 Xilinx需要的对象。在这种情况下,我们使用了教程项目中的一个简单示例,它非常简单且很小。

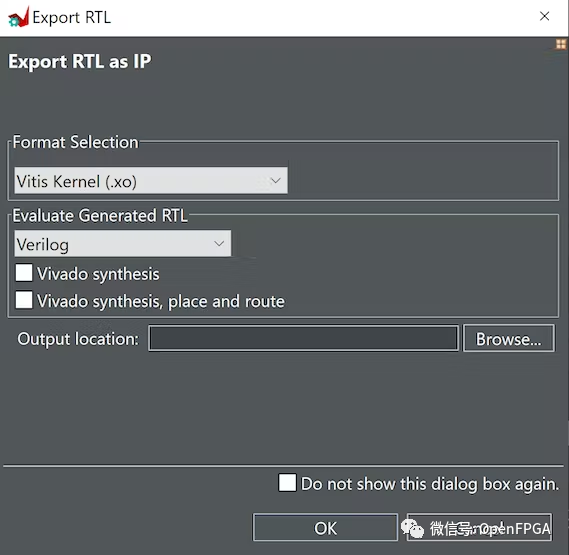

从导出 RTL 对话框中,选择 Vitis 内核选项来代替正常的 Vivado IP。

导出内核

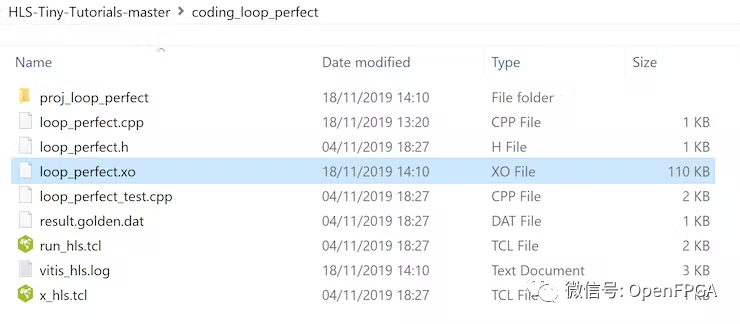

Xilinx 对象将导出到设置的位置。

xo文件导出

现在我们可以将获取的 XO 文件包含在我们的一个或多个 Vitis 设计中。当然,如果我们需要硬件实现,我们也可以将 IP 导出到 Vivado。

RTL与HLS强强联合打造FPGA新开发之路

从上面的一个示例我们看到了,Vitis大大方便了整个FPGA开发流程,减少了设计周期,虽然目前与Verilog/SV/VHDL实现的硬件在资源方面还是有很大差距,但是很多公司一直在致力于这方面的实现,毕竟这是一个趋势。那么目前HLS真的一无用处吗?

答案是否定的,合理运用HLS的强大数据处理能力,能达到事倍功倍的效果,毕竟目前FPGA资源都是过剩的。

RTL与HLS强强联合打造FPGA新开发之路:只需要把两者结合好;RTL做控制,HLS做数据流计算这样的组合才跑得欢快~

PS:不知道大家注意没,Vivado中很多官方/第三方IP都是使用HLS搭建的,尤其在视觉图像、数字信号处理等方面。

总结

这是《FPGA高层次综合HLS》系列教程开篇,后面会按照专题继续更新,文章有什么问题,欢迎大家批评指正~感谢大家支持。