上一篇我们讲过set_input_delay:set_input_delay如何约束?

什么是output_delay?

顾名思义,output_delay就是指输出端口的数据相对于参数时钟边沿的延时。

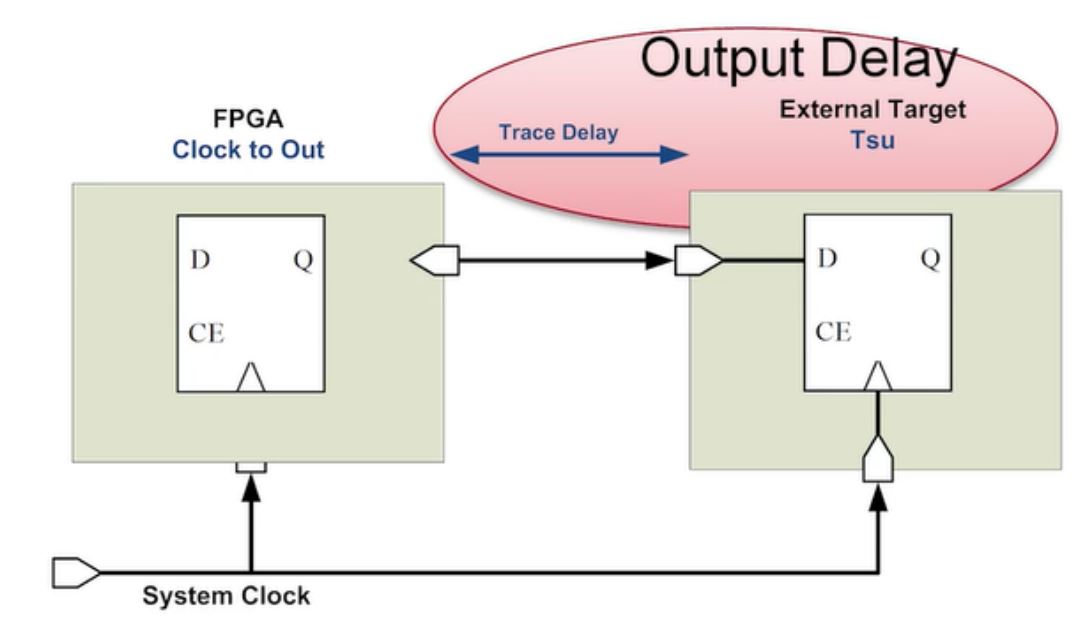

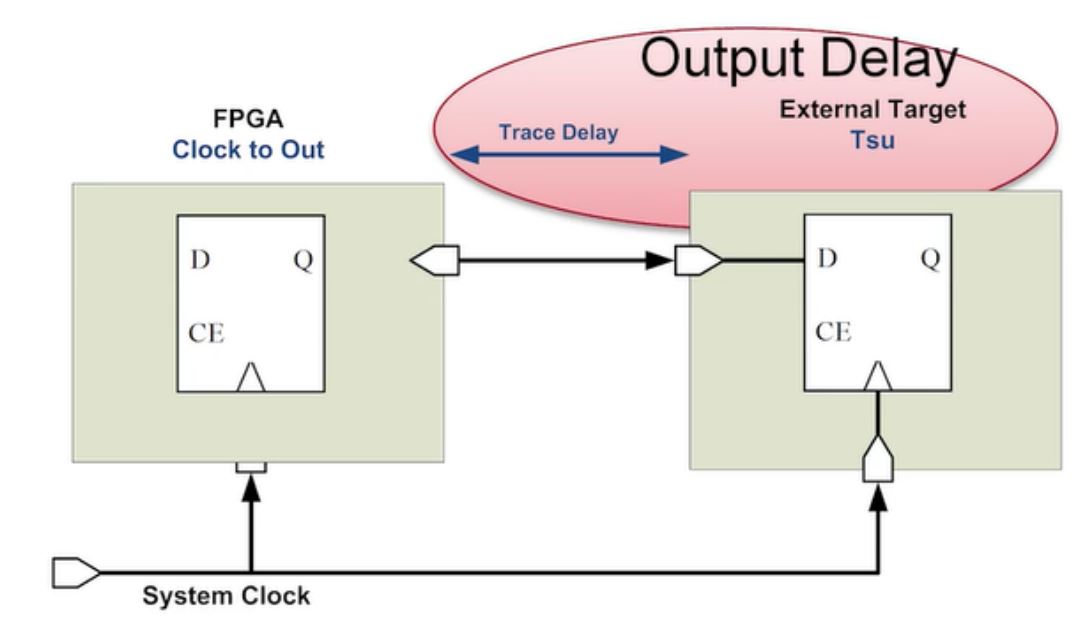

对于系统同步,FPGA和下游器件是同一个时钟源,output delay的设置方式如下图所示:

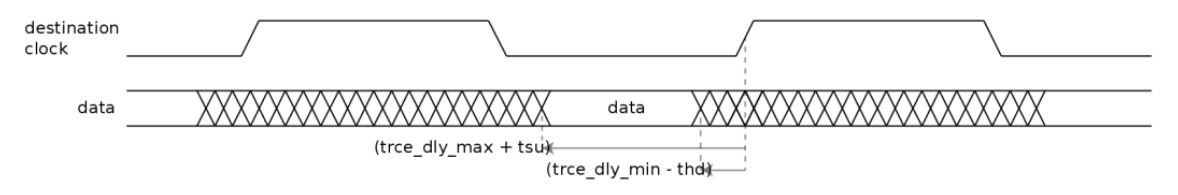

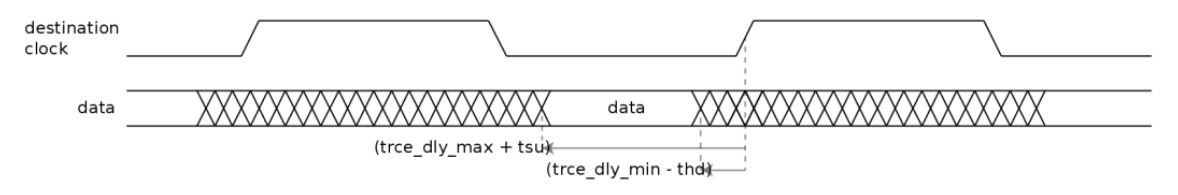

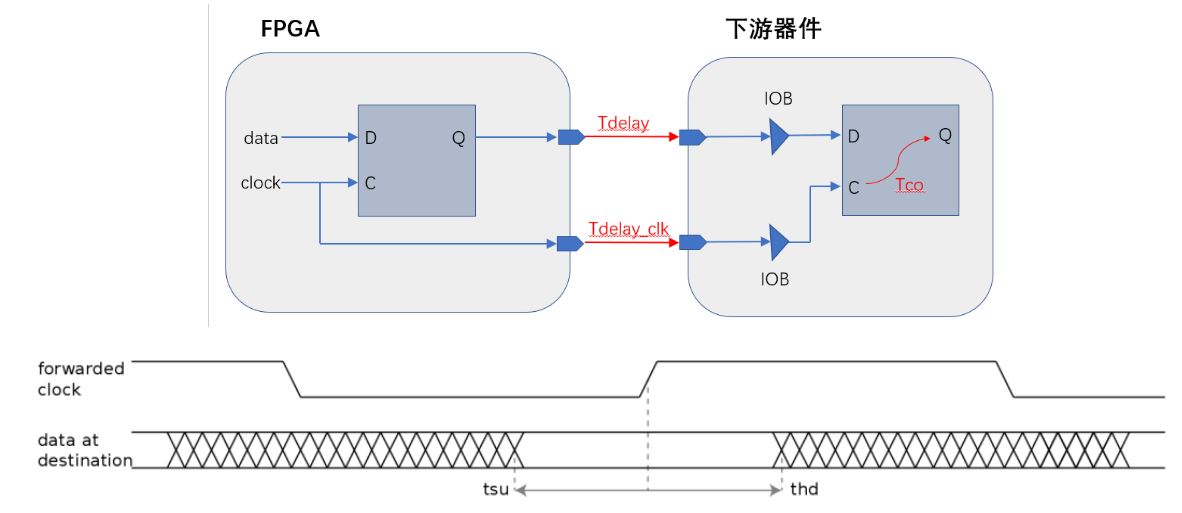

对于我们常用的源同步场景,output delay的设置方式如下图所示:

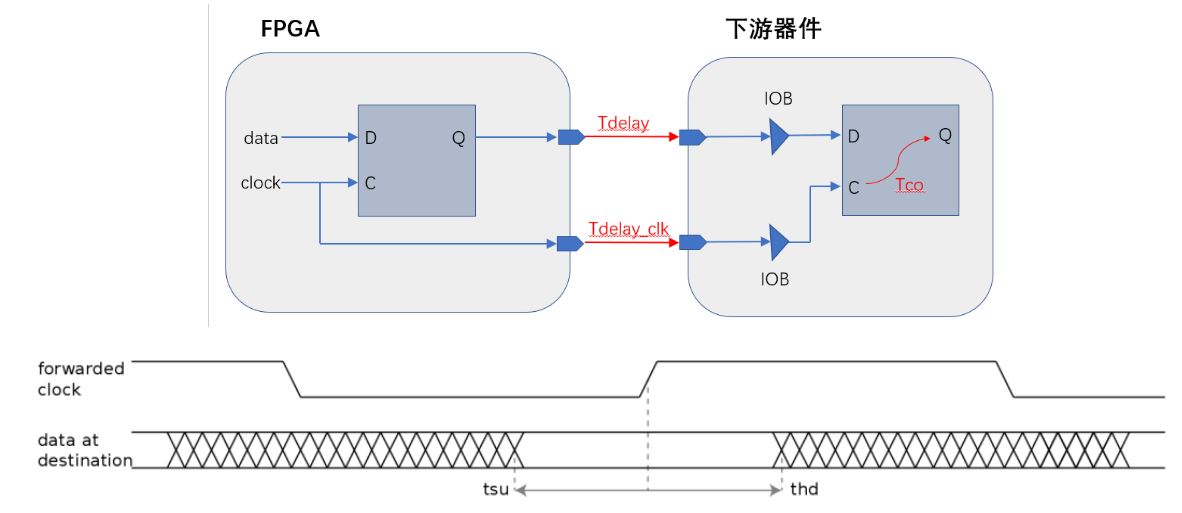

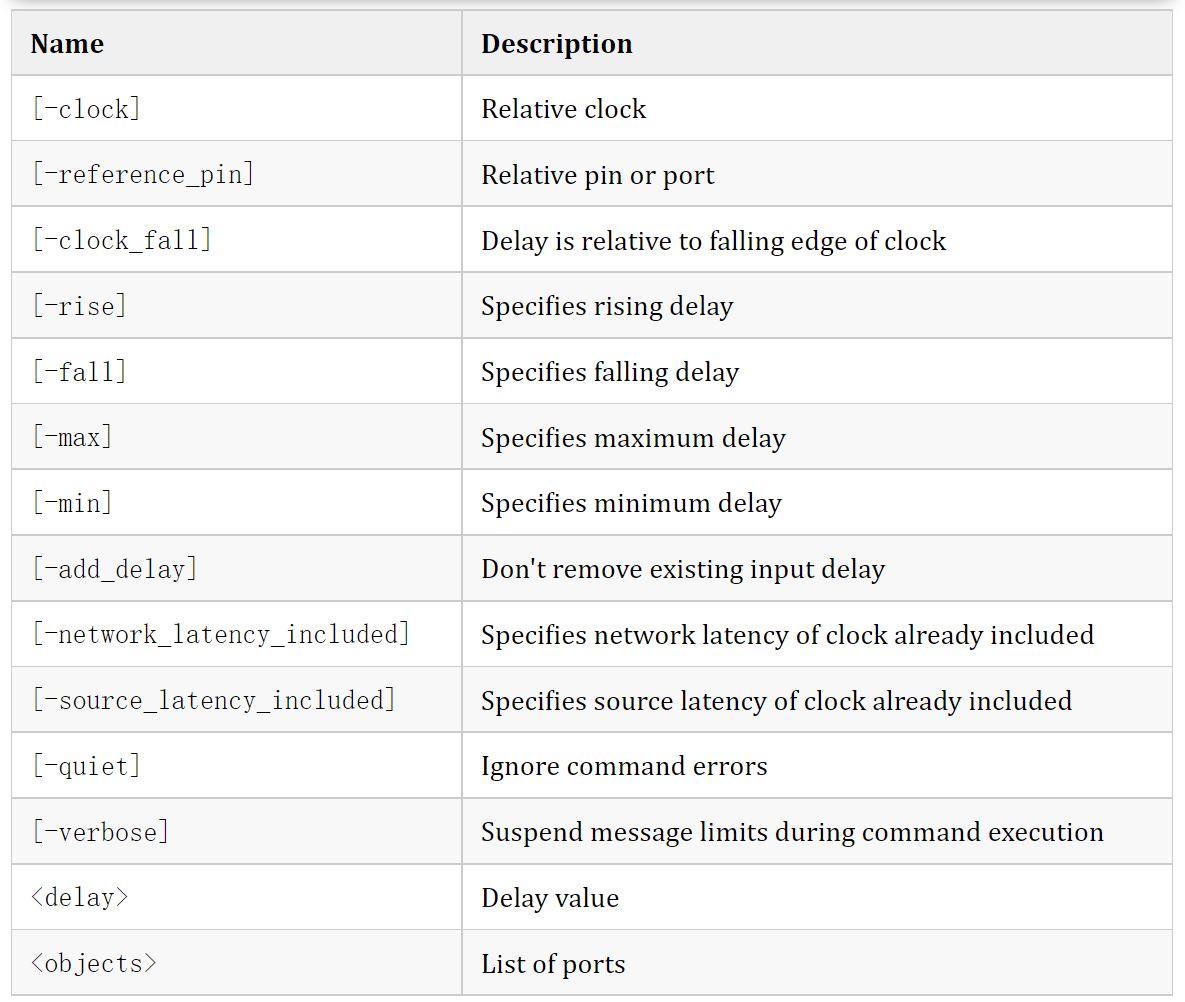

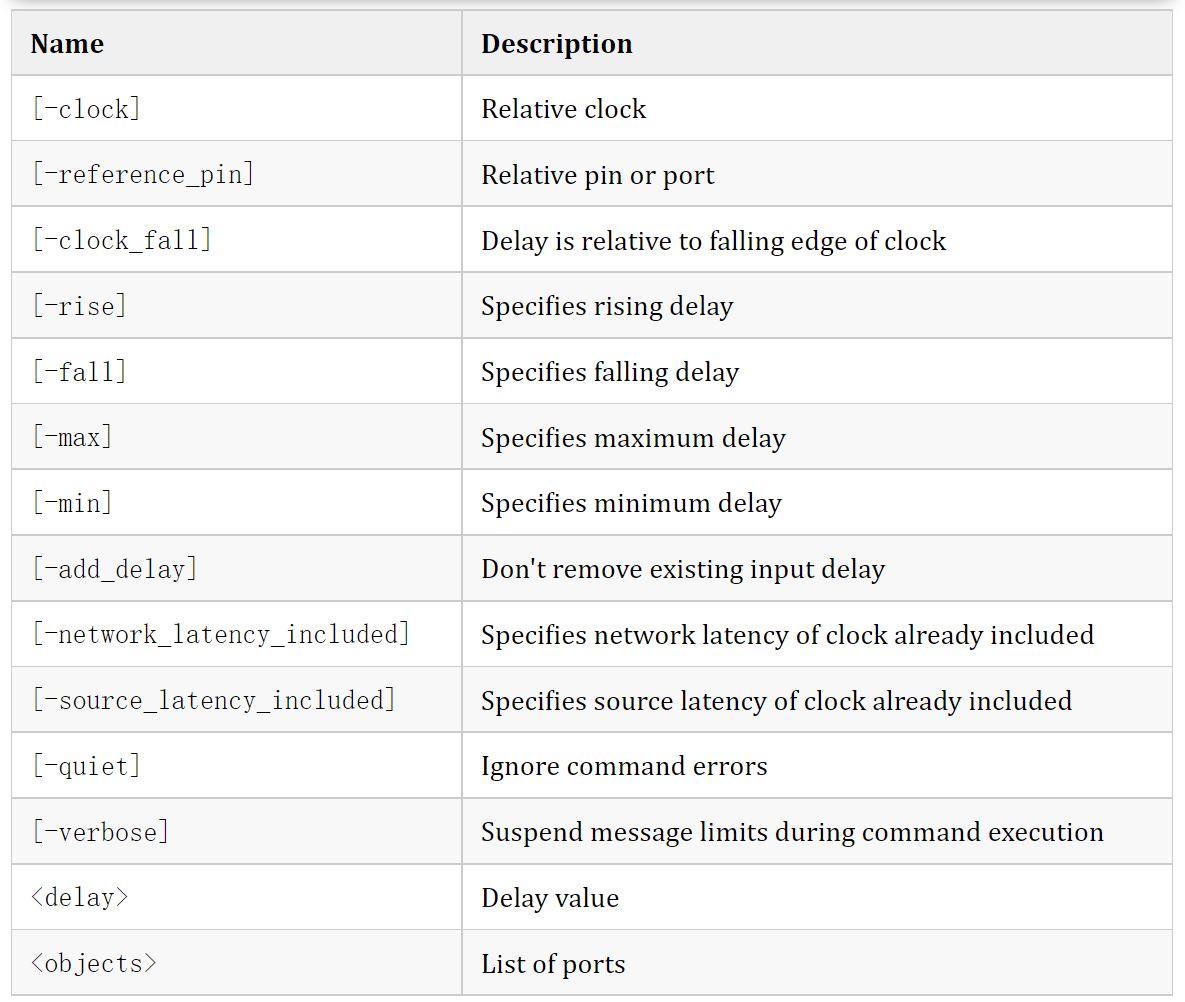

set_output_delay语法

set_output_delay [‑clock ] [‑reference_pin ] [‑clock_fall]

[‑rise] [‑fall] [‑max] [‑min] [‑add_delay] [‑network_latency_included]

[‑source_latency_included] [‑quiet] [‑verbose]

下面来详细说明一下:

-clock:input_delay一般是相对时钟而言的,而且默认是相对于上升沿,我们可以通过clock_fall参数来指定下降沿,这里的时钟可以是虚拟时钟;

-reference_pin:指定相对于某个pin上的时钟边沿,跟-clock的参数其实是一个意思,毕竟时钟也是通过pin输入进来的;

-clock_fall:指定相对于时钟下降沿

-rise:指定端口的上升转换的输入延迟

-fall:指定端口的下降沿的输入延迟

-max:最大延迟

-min:最小延迟,我们做input delay主要就是约束这两个参数

-add_delay:以增量的方式添加延迟,如果不加该参数,默认行为是替换现有的延时

-network_latency_included:表示参考时钟的网络延迟也包含在延迟中

-source_latency_included:跟上一个参数类似的含义,该参数表示时钟的源端延迟包含在延时中

-quiet:忽略指令的错误信息,即便指令错了也依然返回TCL_OK

-verbose:命令执行期间忽略消息数量的限制,就是说会返回该指令的所有的message

delay:延迟值

objects:端口列表

Vivado Timing Constraints Wizard

还是一样通过Vivado的Timing Constraints Wizard工具来进行约束会方便很多:

下面来详细说明一下:

-clock:input_delay一般是相对时钟而言的,而且默认是相对于上升沿,我们可以通过clock_fall参数来指定下降沿,这里的时钟可以是虚拟时钟;

-reference_pin:指定相对于某个pin上的时钟边沿,跟-clock的参数其实是一个意思,毕竟时钟也是通过pin输入进来的;

-clock_fall:指定相对于时钟下降沿

-rise:指定端口的上升转换的输入延迟

-fall:指定端口的下降沿的输入延迟

-max:最大延迟

-min:最小延迟,我们做input delay主要就是约束这两个参数

-add_delay:以增量的方式添加延迟,如果不加该参数,默认行为是替换现有的延时

-network_latency_included:表示参考时钟的网络延迟也包含在延迟中

-source_latency_included:跟上一个参数类似的含义,该参数表示时钟的源端延迟包含在延时中

-quiet:忽略指令的错误信息,即便指令错了也依然返回TCL_OK

-verbose:命令执行期间忽略消息数量的限制,就是说会返回该指令的所有的message

delay:延迟值

objects:端口列表

Vivado Timing Constraints Wizard

还是一样通过Vivado的Timing Constraints Wizard工具来进行约束会方便很多:

对应的约束如下:

set_output_delay -clock [get_clocks {clk}] -min -add_delay -1.0 [get_ports {led[*]}]

可以看出,对于源同步系统,output delay其实就是下游器件的建立时间和保持时间的要求。

Examples

1.输出数据比时钟延迟3ns的delay:

create_clock -name clk -period 10 [get_ports clk_in]

set_output_delay -clock clk 3 [get_ports DOUT]

2.输入数据相对于时钟的下降沿有2ns的delay:

set_output_delay -clock_fall -clock clk 2 [get_ports DOUT]

3.设置延迟5ns,同时参数时钟的网络延迟也包含在内:

set_output_delay 5.0 -clock clk -network_latency_included [get_ports DOUT]

4.双沿时钟的约束,对上升沿和下降沿都需要进行约束

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_OUT]

set_output_delay -clock clk_ddr -max 2.1 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -max 1.9 [get_ports DDR_OUT] -clock_fall -add_delay

set_output_delay -clock clk_ddr -min 0.9 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -min 1.1 [get_ports DDR_OUT] -clock_fall -add_delay

具体案例

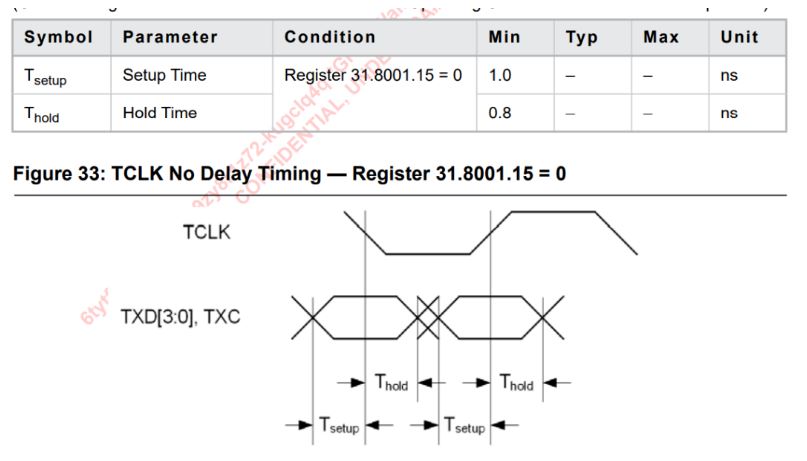

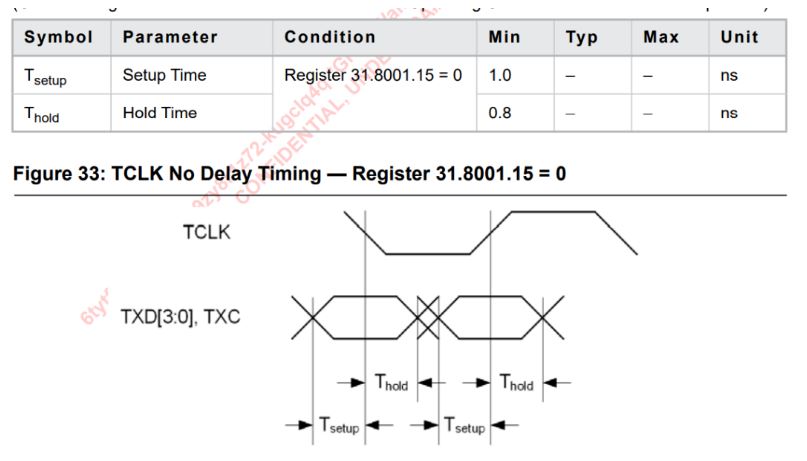

比如某器件手册的输出时钟与数据的setup和hold要求如下图:

对应的约束如下:

set_output_delay -clock [get_clocks {clk}] -min -add_delay -1.0 [get_ports {led[*]}]

可以看出,对于源同步系统,output delay其实就是下游器件的建立时间和保持时间的要求。

Examples

1.输出数据比时钟延迟3ns的delay:

create_clock -name clk -period 10 [get_ports clk_in]

set_output_delay -clock clk 3 [get_ports DOUT]

2.输入数据相对于时钟的下降沿有2ns的delay:

set_output_delay -clock_fall -clock clk 2 [get_ports DOUT]

3.设置延迟5ns,同时参数时钟的网络延迟也包含在内:

set_output_delay 5.0 -clock clk -network_latency_included [get_ports DOUT]

4.双沿时钟的约束,对上升沿和下降沿都需要进行约束

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_OUT]

set_output_delay -clock clk_ddr -max 2.1 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -max 1.9 [get_ports DDR_OUT] -clock_fall -add_delay

set_output_delay -clock clk_ddr -min 0.9 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -min 1.1 [get_ports DDR_OUT] -clock_fall -add_delay

具体案例

比如某器件手册的输出时钟与数据的setup和hold要求如下图:

该时钟双沿采样,在时钟边沿到来后,结合output_delay的最大最小延迟的定义,可以知道:

最大延迟为Tsetup

最小延迟为-Thold

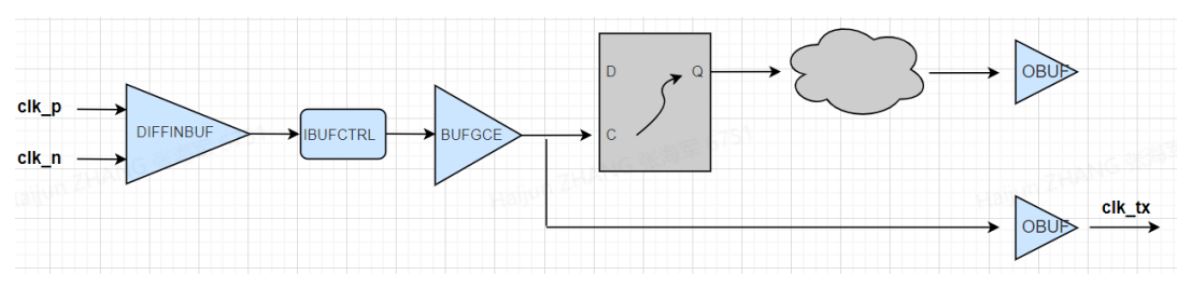

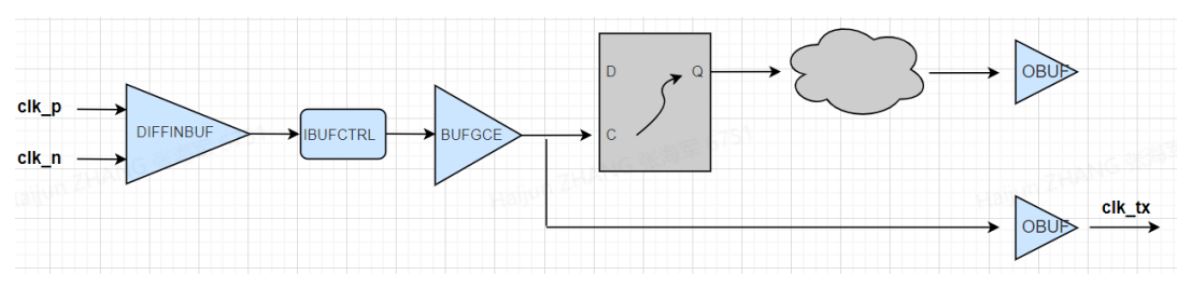

但需要注意的是,输出延迟的时钟位置,一般输出时钟都会经过一级BUFG,再作为数据的随路时钟输出,那我们就需要在输出的pad上先create_generate一个时钟,然后output delay是相对于该时钟进行的。

该时钟双沿采样,在时钟边沿到来后,结合output_delay的最大最小延迟的定义,可以知道:

最大延迟为Tsetup

最小延迟为-Thold

但需要注意的是,输出延迟的时钟位置,一般输出时钟都会经过一级BUFG,再作为数据的随路时钟输出,那我们就需要在输出的pad上先create_generate一个时钟,然后output delay是相对于该时钟进行的。

因此output delay的约束如下:

crate_clock -name clk_in -period 10 [get_ports clk_p]

create_generated_clock -name {tx_clk} -source [get_ports {clk_tx}] -multiply_by 1 -divide_by 1 {get_ports clk_p} -master_clock [get_clocks {clk_in}] -add_delay

set_output_delay -clock [get_clocks clk_tx] -min -0.8 [get_ports DOUT] -add_delay

set_output_delay -clock [get_clocks clk_tx] -max 1.0 [get_ports DOUT] -add_delay

set_output_delay -clock [get_clocks clk_tx] -min -0.8 [get_ports DOUT] -clock_fall -add_delay

set_output_delay -clock [get_clocks clk_tx] -max 1.0 [get_ports DOUT] -clock_fall -add_delay

因此,只要记住:

min_delay就是下游器件的 -hold time

max_delay是下游器件的setup time

如果是双沿的话,就是半个时钟周期,而且还需要对时钟的下降沿进行约束

因此output delay的约束如下:

crate_clock -name clk_in -period 10 [get_ports clk_p]

create_generated_clock -name {tx_clk} -source [get_ports {clk_tx}] -multiply_by 1 -divide_by 1 {get_ports clk_p} -master_clock [get_clocks {clk_in}] -add_delay

set_output_delay -clock [get_clocks clk_tx] -min -0.8 [get_ports DOUT] -add_delay

set_output_delay -clock [get_clocks clk_tx] -max 1.0 [get_ports DOUT] -add_delay

set_output_delay -clock [get_clocks clk_tx] -min -0.8 [get_ports DOUT] -clock_fall -add_delay

set_output_delay -clock [get_clocks clk_tx] -max 1.0 [get_ports DOUT] -clock_fall -add_delay

因此,只要记住:

min_delay就是下游器件的 -hold time

max_delay是下游器件的setup time

如果是双沿的话,就是半个时钟周期,而且还需要对时钟的下降沿进行约束