本文转载自:十年老鸟的CSDN博客

前言

前面我们已经研读了transceiver的参考时钟和复位的相关内容。 但是随着内容的深入,越来越多的信号出现在我的面前。

例如

TXOUTCLK、TXUSERCLK、TXUSERCLK2

RXOUTCLK、RXUSERCLK、RXUSERCLK2

一堆这样的定义,之前不去理解的话那都是云里雾里,现在专门来缕缕这些时钟到底是哪来的,以及要起什么作用,尽量搞清楚其来龙去脉。

TXOUTCLK

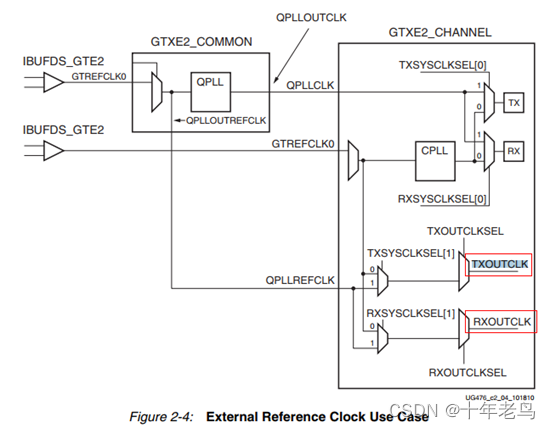

手册中初遇 TXOUTCLK是在这个图,这个图在transceiver参考时钟的文章中也贴出来了

很显然,这两个时钟源头也是来自于参考时钟,但具体定义是在GTXE2_CHANNEL 通道中

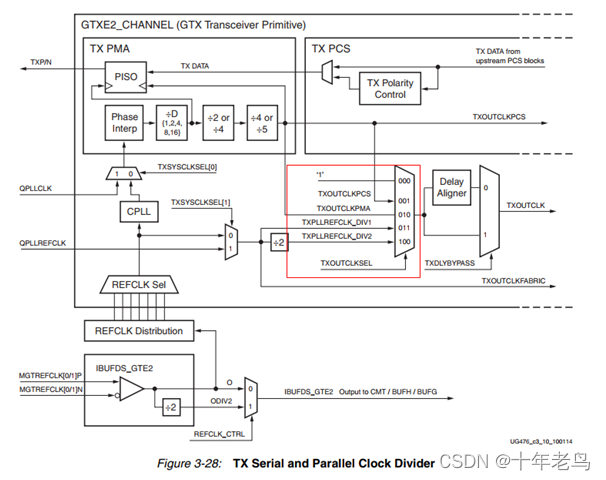

下面这张图是一个更具体的定义:

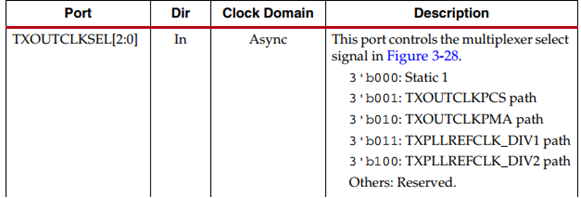

我们来看看TXOUTCLK时钟源的选择说明:

手册是推荐使用 3’b011 或者3’b100。

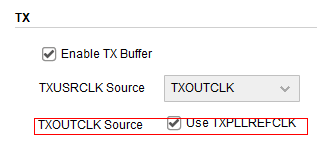

IP和设置中位于此,默认是勾选的

自动生成的代码中

.TXOUTCLKSEL (3'b011),

从图中,我们看到TXOUTCLKPCS和TXOUTCLKFABRIC也引出去了,但手册告诉我们:

TXOUTCLKPCS and TXOUTCLKFABRIC are redundant outputs. Use TXOUTCLK for new designs.

TXOUTCLKPCS and TXOUTCLKFABRIC是多余的,要我们使用TXOUTCLK

总之一句话,在我们一般的应用中,TXOUTCLK的来源是TXPLLREFCLK_DIV1。也就是TXOUTCLKSEL = 3’b011的情况,这个时候TXOUTCLK与参考时钟的频率一致。

RXOUTCLK

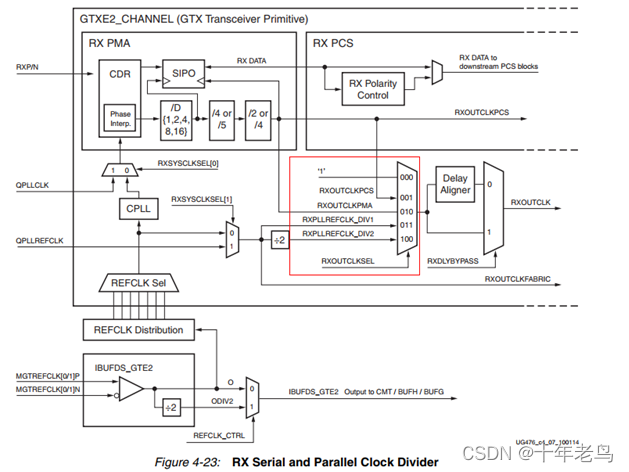

同样的,我们看这个图:

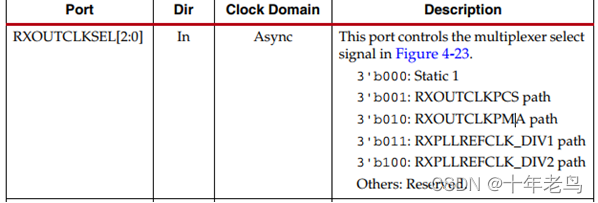

我们来看RXOUTCLK时钟源的选择说明

跟TXOUTCLK不同的是,RXOUTCLKSEL = 3’b010 选择的是RXOUTCLKPMA是恢复时钟,是可以输出到FPGA逻辑中的。恢复时钟适用于某些不需要时钟补偿机制和要求时钟与数据同步的状态(这正是我们目前所用的场景),这个时钟用来时钟驱动下级逻辑模块。它也用于RX PCS模块。

RXOUTCLKSEL = 3’b011和RXOUTCLKSEL = 3’b100的时候,用于不需要输出恢复时钟到逻辑的时候。RXPLLREFCLK_DIV1 or RXPLLREFCLK_DIV2可以做系统时钟,但通常是将TXOUTCLK用作系统时钟。

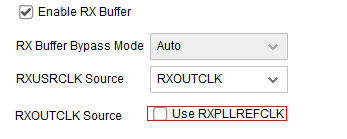

P和设置中位于此,默认是不勾选的

这里特别要注意

自动生成的代码中

.RXOUTCLKSEL (3'b010),

从图中,我们看到RXOUTCLKPCS和RXOUTCLKFABRIC也引出去了,但同样的,手册告诉我们:

RXOUTCLKPCS and RXOUTCLKFABRIC are redundant outputs. RXOUTCLK should be used for new designs. RXOUTCLKPCS and RXOUTCLKFABRIC是多余的,要我们使用RXOUTCLK

总之,在我们目前的应用中,RXOUTCLK的来源是RXOUTCLKPMA。也就是TXOUTCLKSEL = 3’b010的情况,这个时候RXOUTCLK输出的就是恢复时钟。