本文转载自:FPGA技术实战的CSDN博客

引言: 高速串行收发器在5G通信、机器视觉、图像处理及数据中心等众多领域广泛应用,FPGA开发人员熟练掌握该接口使用能够提升自己的专业竞争力。本系列文章针对Xilinx 7系列FPGA GTX/GTH收发器的架构进行介绍,参考文档主要为官方UG476。作为系列开篇,本博文主要对GTX/GTH收发器进行总体概述。通过该文档,了解以下内容:

1. 概述及7系列FPGAG特性

1.1收发器速率及特性

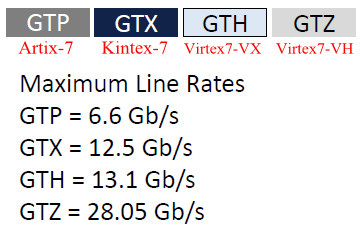

Xilinx公司的收发器主要包括以下四种,如图1所示。四种收发器支持的最大线速率不同,每种收发器位于的器件也不同。

图1、Xilinx 7系列FPGA收发器种类

GTX/GTH收发器具有高度可配置性,并与FPGA的可编程逻辑资源紧密集成。7系列FPGA GTX/GTH收发器特性如表1-1所示。

表1-1:FPGA GTX/GTH收发器特性

第一次使用收发器的开发者推荐阅读《High-Speed Serial I/O Made Simple》(有需要的可以关注私信我,中文版)文献,其描述了高速串行收发器技术和应用。Xilinx开发工具CORE Generator™工具提供了一个自动配置GTX/GTH收发器向导(如图6),可以实现不同协议的用户应用。

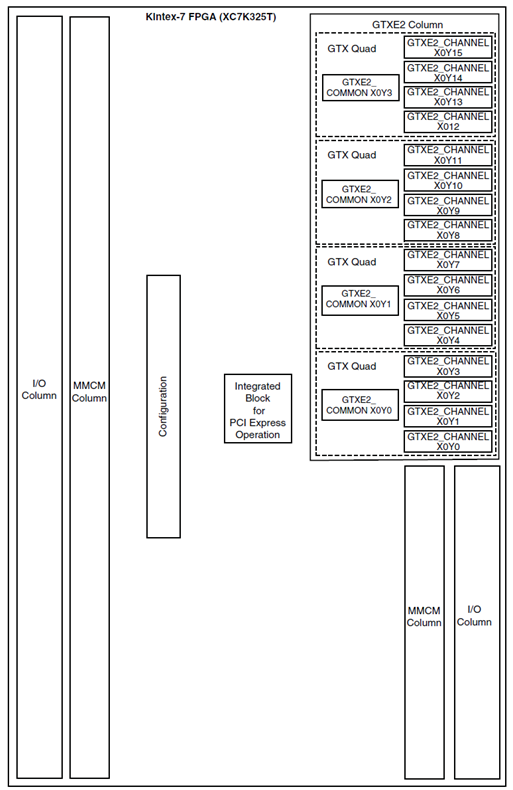

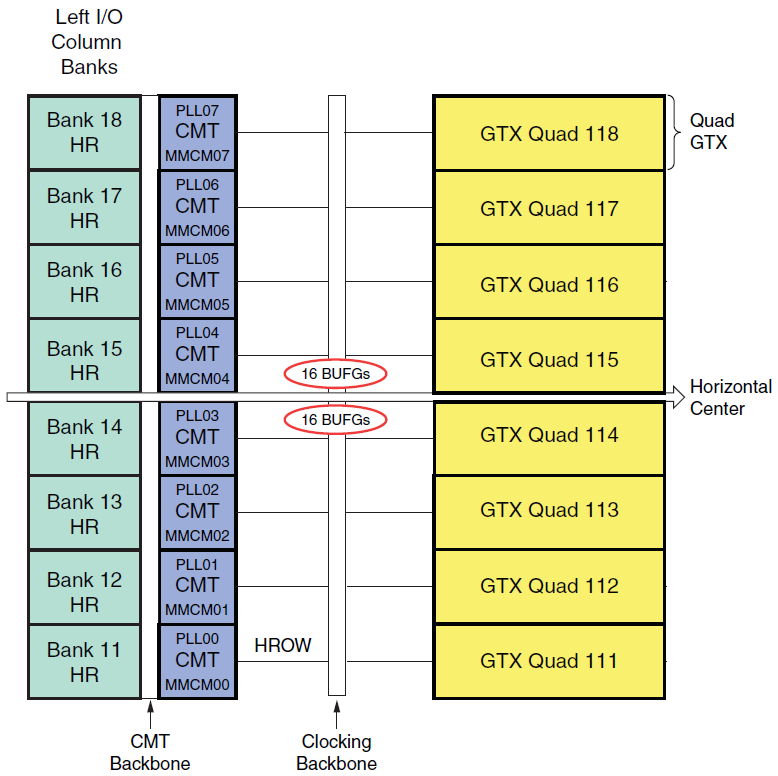

图1举例了XC7K325T器件GTX收发器布局,该系列器件具有16个收发器。图中只显示了TOP部分的8个收发器,BOT部分还有对称的8个收发器。

图2、XC7K325T器件GTX收发器布局

在Xilinx FPGA中,收发器按照Quad进行组织结构。4个GTXE2_CHANNEL原句和一个GTXE2_COMMON原句成为一个Quad。图3举例了一个Quad内收发器结构。

图3、Quad内收发器结构

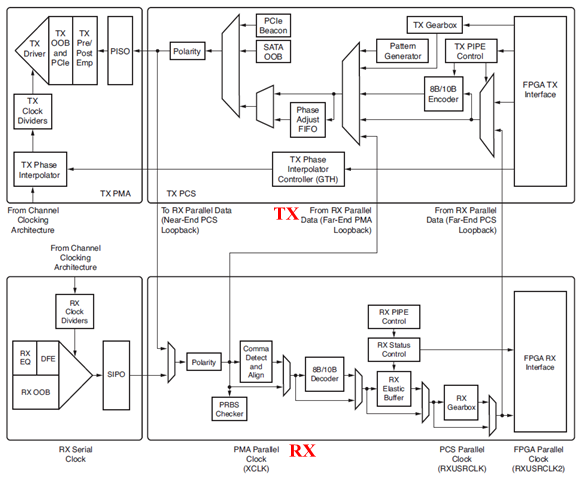

图4给出了GTXE2_CHANNEL原句内部结构,从图中可以看到收发器通道包括发送(TX)和接收(RX)两部分,对于该部分内容详细介绍,将在后续文章介绍。

图4、GTXE2_CHANNEL原句内部结构

1.2收发器IP核支持的常见协议

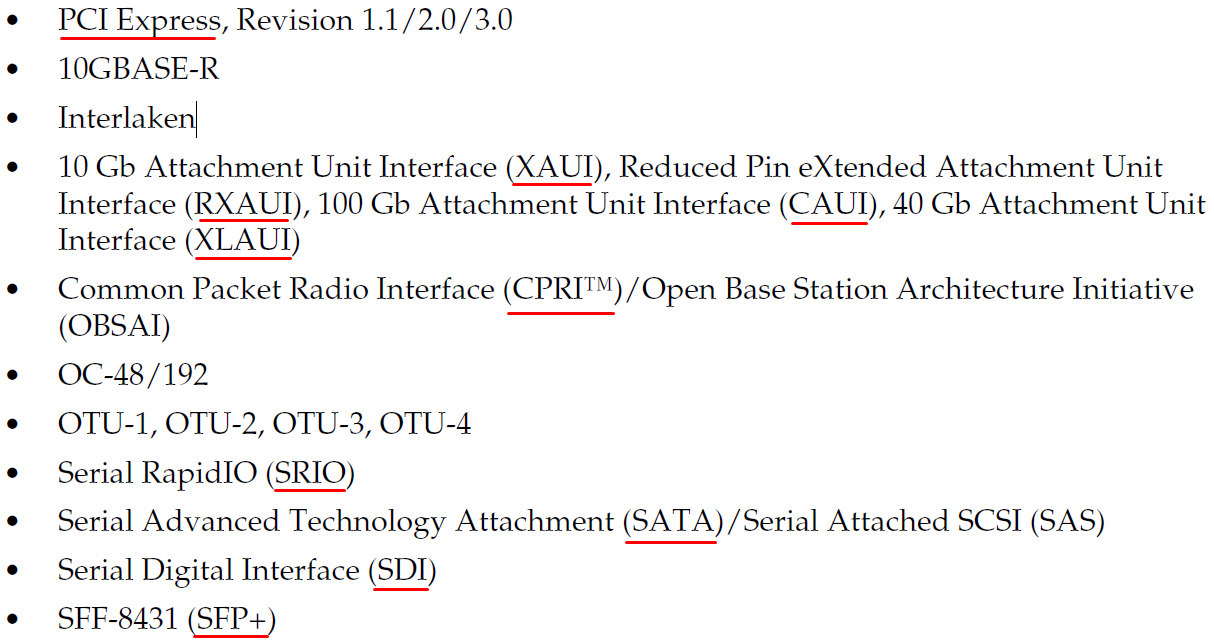

IP核支持的常见协议如图5所示。

图5、IP核支持的常见协议

2. FPGA收发器向导

7系列FPGAs收发器向导(以下称为向导)是生成封装文件(wrapper)以及实例化GTX/GTH收发器原语的首选工具。向导位于CORE Generator™工具中。

图6、GTX/GTH收发器向导

3. 仿真

该部分内容,在后续收发器设计实例相关文章中,会给大家做详细介绍,本概述中暂不介绍。

4. 实现

4.1 功能描述

在设计早期定义GTX/GTH收发器Quad的位置是推荐的设计原则,以确保时钟资源的正确使用,并便于在电路板设计期间进行信号完整性分析。实现过程通过在XDC中使用位置约束来完成Quad位置分配验证。

该部分介绍映射7系列GTX/GTH收发器到器件资源所需的信息,主要包括三部分:

每个GTX/GTH收发器信道和COMMON原语的位置由描述列号和该列内相对位置的XY坐标系指定(如图7)。目前所有的7系列器件家族中,GTX/GTH收发器Quads都位于单一的列中,并且位于芯片Die的一侧。

图7、收发器在FFG900封装布局

有两种方法可以为GTX/GTH收发器的创建XDC约束:

4.2 串行收发器器件封装

该部分内容可以参照官方UG475文档,7 Series FPGAs Packaging and Pinout Specification,该文档描述了Xilinx器件管脚命名规则,器件信号布局等封装信息,对于FPGA原理图及PCB设计人员具有非常重要的作用。图7和图8位该文档重要信息举例。

图7、收发器Bank举例

图8、收发器Pinout封装布局举例