本文转载自:FPGA技术实战的CSDN博客

引言:

我们之前的几篇文章介绍完了FPGA收发器的共享资源。从本文开始,我们介绍Xilinx 7系列收发器TX的功能和结构,学会如何进行配置和使用该部分资源。本文介绍以下内容:

GTX/GTH收发器TX结构

GTX/GTH收发器TX接口配置和时钟方案

1.FPGA收发器TX概述

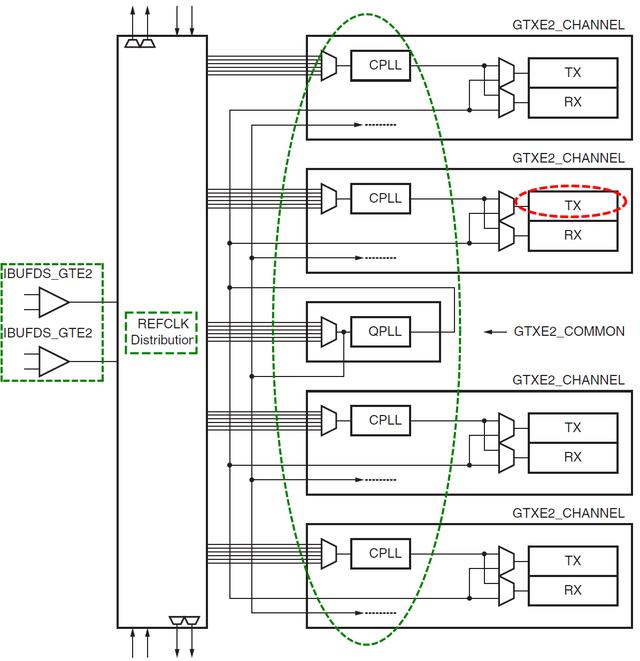

如图1所示,我们前面几篇文章已经介绍完图中绿色虚线圈住的FPGA资源。从图中可以看到Xilinx公司的收发器按照Quad进行组织,一个Quad包括4个收发器、一个QPLL时钟和相应的时钟输入及时钟分配资源。一个收发器内部又包括一个CPLL、收发器接收通道和收发器发送通道。Xilinx将一个收发器内部的发送通道和接收通道简称为TX和RX。本文及后面文章我们详细介绍TX的结构和功能,并结合实际案例介绍这些资源是如何使用的以及如何影响我们的FPGA设计。

图1、7系列FPGA收发器Quad结构

图2展示了收发器TX内部结构框图。TX内部主要分为11部分资源:FPGA TX接口、TX 8B/10B编码器、TX速率变换、TX Buffer、TX PRBS产生器、TX极性控制、TX时钟输出控制、TX相位控制器、TX驱动器、TX PCIe检测支持和TX OOB信号支持。

图2、GTX/GTH收发器TX模块图(点击看大图)

2.FPGA TX接口

2.1接口位宽配置

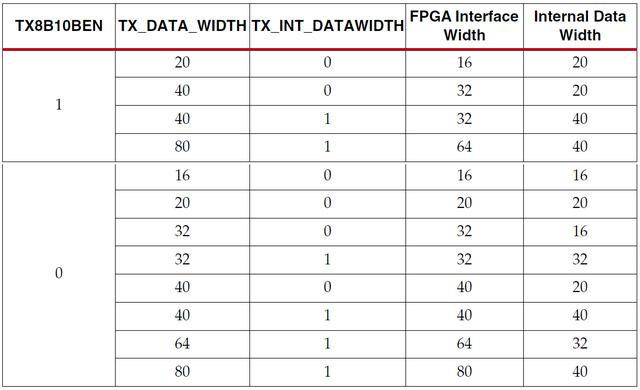

用户通过FPGA TX接口在TXUSRCLK2的上升沿将数据写到TXDATA端口。TXDATA端口可以配置为2、4或者8字节宽度。TXDATA端口字节宽度由TX_DATA_WIDTH和TX_INT_DATAWIDTH属性以及TX8B10BEN端口决定。FPGA TX接口数据路径配置如图3所示。

图3、FPGA TX接口数据路径配置

当不使用8B/10B编码器时,TXDATA端口位宽需要做位宽展宽,比如TXDATA端口16bit扩展为20bits,32扩展为40bit,64扩展为80bits,展宽格式如4所示。

图4、TXDATA端口位宽展宽格式(点击看大图)

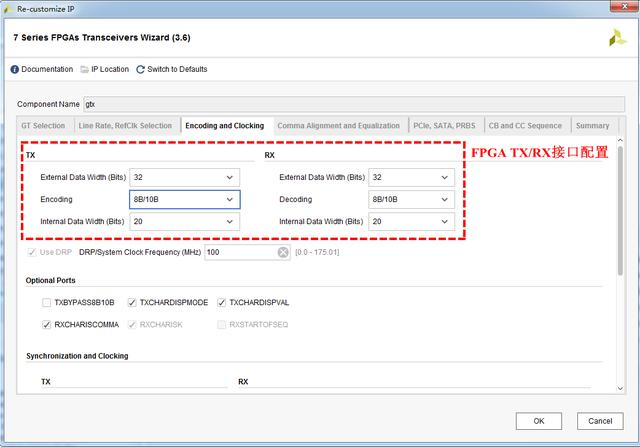

GTX/GTH收发器IP核TX/RX接口配置如图5所示。

图5、GTX/GTH收发器IP核TX/RX接口配置

2.2 TXUSRCLK和TXUSRCLK2时钟产生

FPGA TX接口包括两个并行时钟:TXUSRCLK和TXUSRCLK2。TXUSRCLK为GTX/GTH内部TX PCS逻辑时钟。图6中式-1显示了TXUSRCLK时钟的计算。

图6、TXUSRCLK时钟计算公式

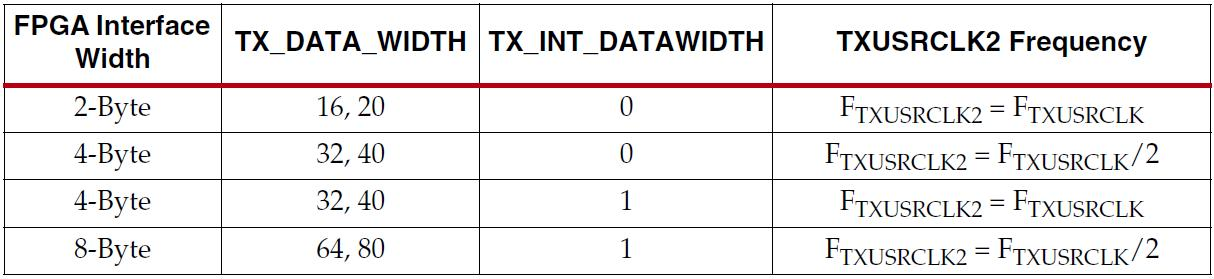

TXUSRCLK2为进入TX侧所有信号的采样时钟,大部分信号在TXUSRCLK2的上升沿采样。TXUSRCLK和TXUSRCLK2之间存在固定的关系,如图7所示。

图7、TXUSRCLK和TXUSRCLK2频率关系

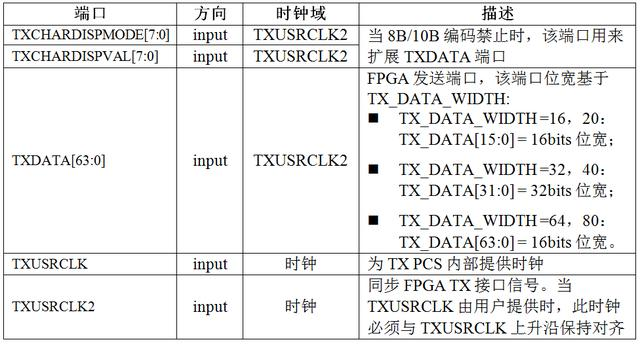

2.3 FPGA TX接口定义

FPGA TX接口定义如图8所示。

图8、FPGA TX接口定义

2.4 FPGA TX接口时钟设计

FPGA TX接口时钟TXUSRCLK2有4中时钟设计方案,这些时钟方案中,TXOUTCLK时钟来自MGTREFCLK0[P/N]或者MGTREFCLK1[P/N],并且设置TXOUTCLKSEL=3'b011选择TXPLLREFCLK_DIV1路径。

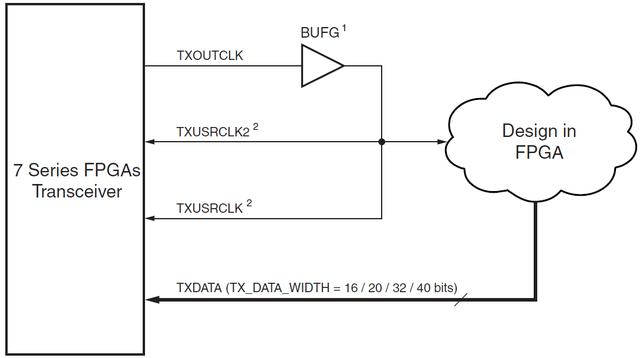

第1种:2字节或4字节TXDATA位宽下TXOUTCLK驱动FPGA TX接口(单个Lane)

如图9所示,此种情况下,TXUSRCLK时钟和TXUSRCLK2时钟频率相同。

图9、单个Lane时TXOUTCLK驱动TXUSRCLK2(2字节或4字节)

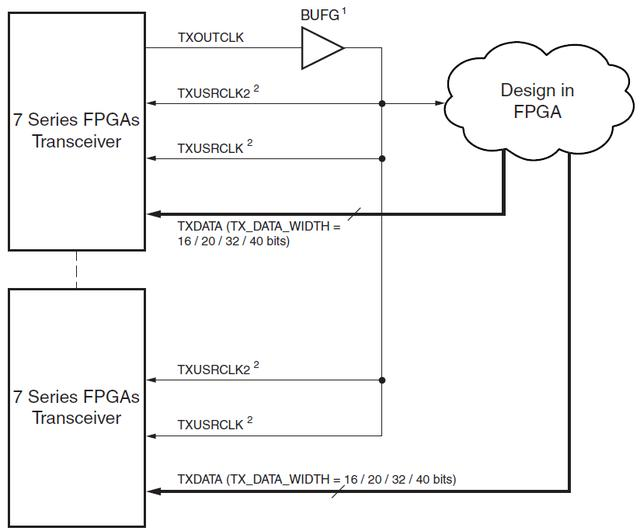

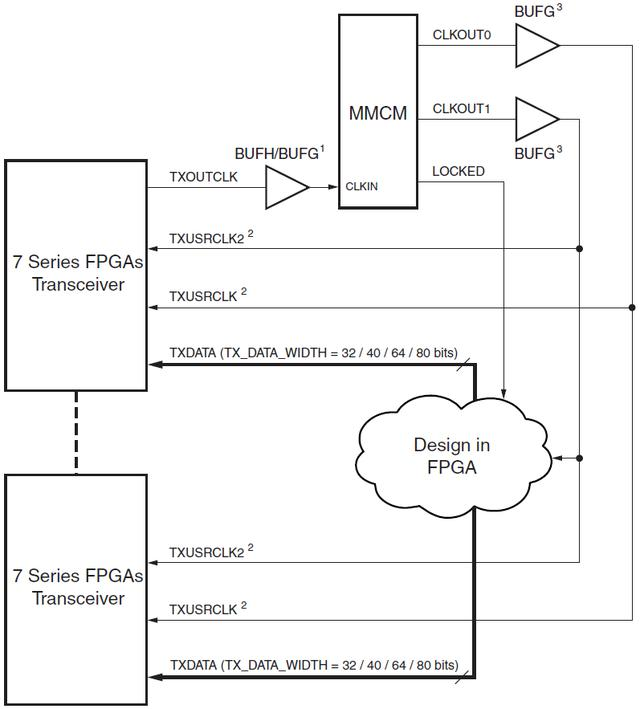

第2种:2字节或4字节TXDATA位宽下TXOUTCLK驱动FPGA TX接口(多个Lane)

如图10所示,此种情况下,TXUSRCLK时钟和TXUSRCLK2时钟频率相同。

图10、多个Lane时TXOUTCLK驱动TXUSRCLK2(2字节或4字节)

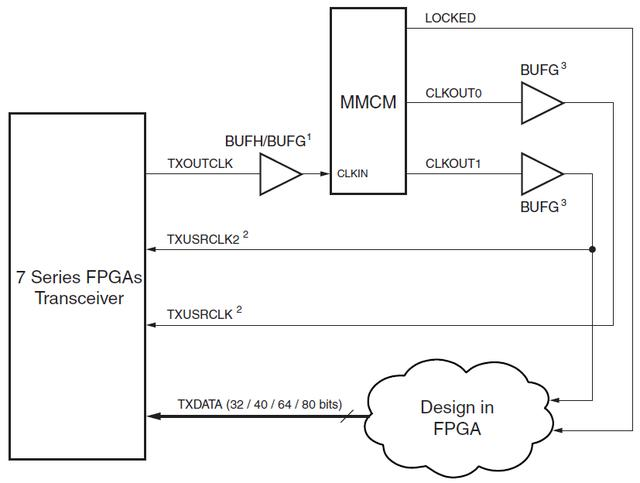

第3种:4字节或8字节TXDATA位宽下TXOUTCLK驱动FPGA TX接口(单个Lane)

如图11所示,此种情况下,TXUSRCLK时钟为TXUSRCLK2时钟频率的2倍。

图11、单个Lane时TXOUTCLK驱动TXUSRCLK2(4字节或8字节)

第4种:4字节或8字节TXDATA位宽下TXOUTCLK驱动FPGA TX接口(多个Lane)

如图12所示,此种情况下,TXUSRCLK时钟为TXUSRCLK2时钟频率的2倍。

图12、多个Lane时TXOUTCLK驱动TXUSRCLK2(4字节或8字节)

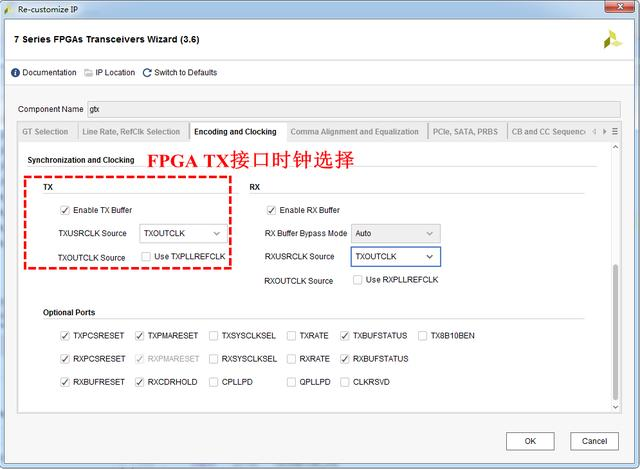

图13显示了配置GTX/GTH收发器IP核时,FPGA TX接口时钟选择界面。

图13、GTX/GTH收发器FPGA TX接口时钟选择界面