本文转载自:FPGA技术实战的CSDN博客

引言:前面几篇文章,我们介绍了7系列FPGA收发器TX的FPGA接口、8B/10B 编码器、变速模块以及TX管脚极性控制。通过本文可以学习以下内容:

TX Buffer(缓冲器)的结构及使用

TX PRBS(伪随机序列)产生器的使用

1.TX Buffer

1.1 TX Buffer结构介绍

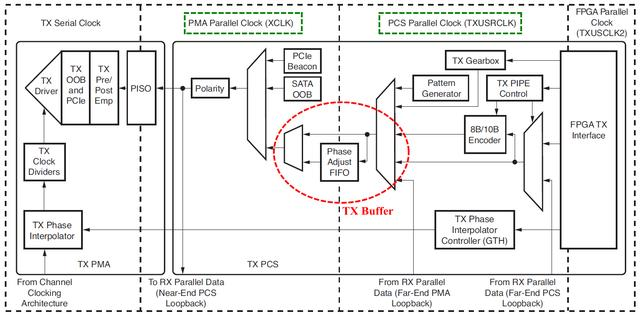

图1显示了TX Buffer处于收发器TX结构的位置。

图1、收发器TX时钟域

GTX/GTH收发器TX数据路径内有两个内部并行时钟域用于PCS组件:PMA组件并行时钟XCLK时钟域和TXUSRCLK时钟域,如图1所示。为了正确发送数据,XCLK速率必须匹配TXUSRCLK速率,同时,这两个时钟域之间的相位误差必须解决。

GTX/GTH收发器提供两种方法解决XCLK和TXUSRCLK跨时钟域问题:

TX Bufffer

TX相位对齐电路

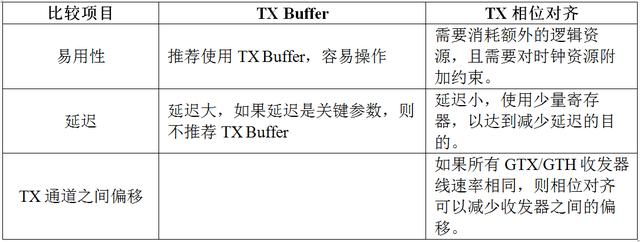

当TX Buffer旁路时,TX相位对齐电路被使用解决跨时钟域问题。也就是说,所有的TX数据路径必须要么使用TX Bufffer,要么使用TX相位对齐电路。图2给出了这两种方法在选取时的权衡。

图2、TX Buffer VS TX相位对齐

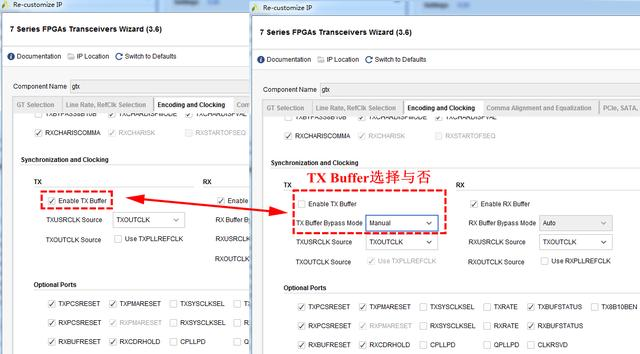

1.2 TX Buffer使用方法

当TXBUFSTATUS指示溢出时应该复位TX Buffer。GTTXRESET、TXPCSRESET或者GTX/GTH收发器内部产生的TX Buffer复位都可以复位TX Buffer。为了使能TX Buffer,需要设置以下选项:

TXBUF_EN = TRUE

TX_XCLK_SEL = TXOUT

图3、TX Buffer配置

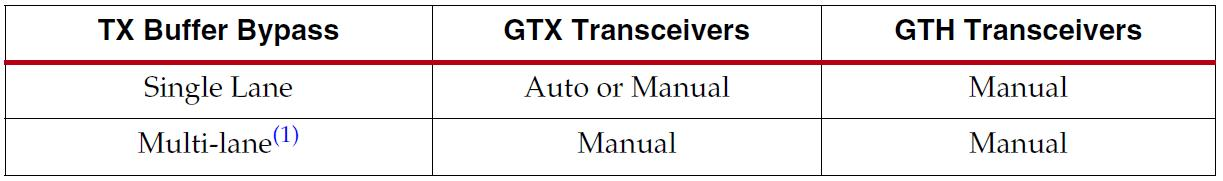

1.3 TX Buffer Bypass使用方法

旁路TX Buffer是7系列GTX/GTH收发器的高级特性,此时TX相位对齐电路用来实现XCLK和TXUSRCLK时钟域之间的相位差异,也可以实现TX延迟对齐调整。对于GTX收发器,这种调整可以自动或者手动,而GTH收发器必须由用户手动控制。图4显示了TX Buffer Bypass使用模式。

图4、TX Buffer Bypass使用模式

2.TX PRBS(伪随机序列)产生器

2.1 TX PRBS功能

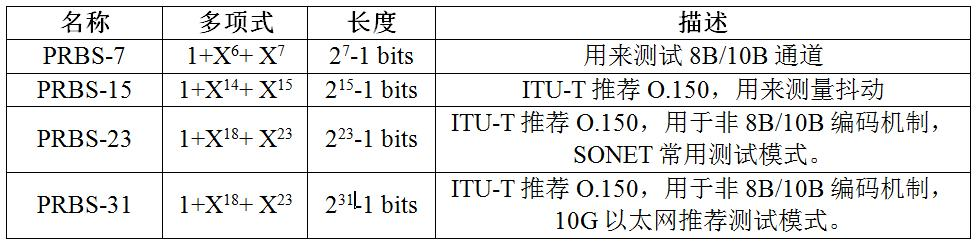

TX PRBS通常用来测试高速链路的信号完整性。GTX/GTH收发器可以产生几种工业级PRBS,如图5所示。

图5、GTX/GTH收发器TX支持的PRBS模式

图6显示了TX PRBS序列产生器模块图。图中,错误插入模块用于检测链路连通性和抖动容限性测试,采用TXPOLARITY信号支持PRBS翻转。

图6、TX PRBS序列产生器模块图

2.2 TX PRBS使用模式

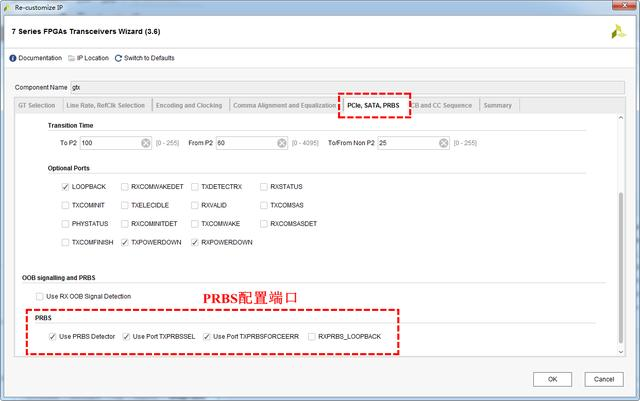

图7显示了GTX/GTH IP核TX PRBS配置端口。

图7、GTX/GTH IP核TX PRBS配置端口

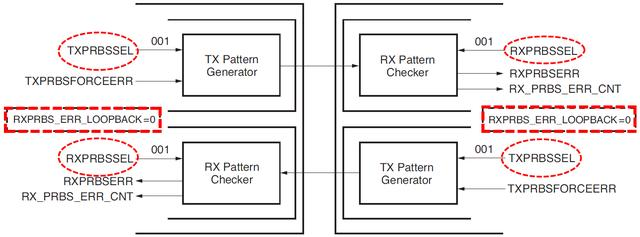

1)链路测试模式

图7显示了使用PRBS-7进行链路测试的示意图。该模式下配置如图中红色虚线标记。输入的数据流只有PRBS模式的数据流才能被RX接收端的PRBS检测器接收。

图7、使用PRBS-7进行链路测试的示意图

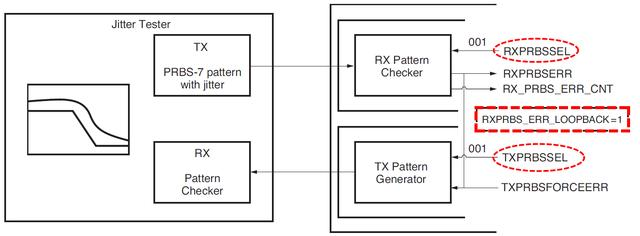

2)抖动容忍测试

图8显示了使用PRBS-7模式进行抖动容忍测试。为了精确的计算器接收器的BER(比特错误率),可以采用外部抖动容忍检测器。该模式下配置如图中红色虚线标记。

图8、使用PRBS-7模式进行抖动容忍测试