版权声明:本文为CSDN博主「ZYNQRFSOC」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/zhu41/article/details/123624007

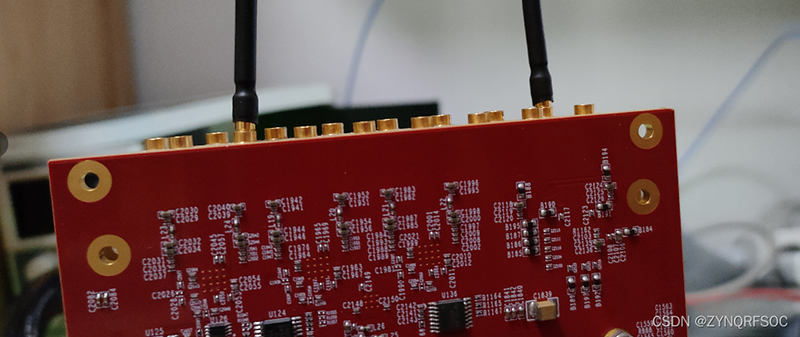

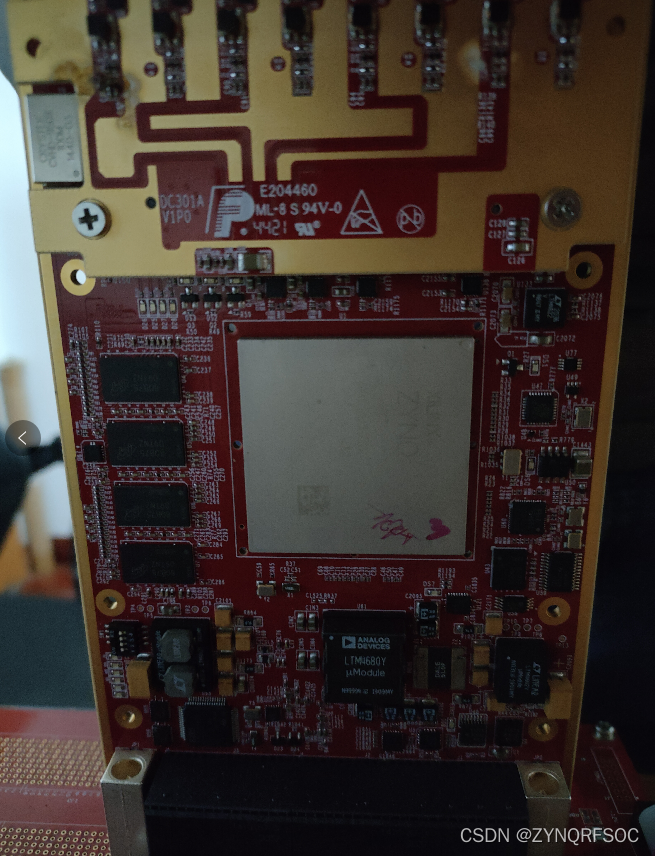

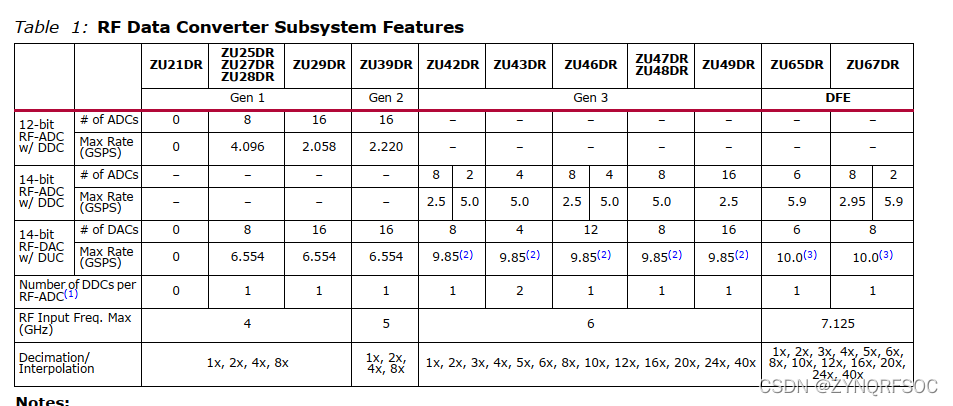

RFSOC-27DR产品是基于Zynq UltraScale + RFSoC ZU27DR主芯片(IC内部已集成高速ADC和DAC)的VPX平台评估板,支持多板级联,该产品支持8路12位ADC 4.096 GSPS , 8路14位DAC 6.4 GSPS。可以降低 RF信号处理链的复杂性,最大化输入/输出通道密度,而不会牺牲宽带宽并利用异构处理能力 ,并且拥有更低的功耗(取消了 ADC/DAC 组件,消除了 FPGA至模拟的接口功耗)。Zynq UltraScale+ 器件中提供 ARM Cortex-A53 处理子系统、UltraScale+ 可编程逻辑和最高信号处理带宽,能够提供综合 RF 信号链,满足无线、有线电视接入、测试测量、早期预警/雷达以及其它高性能 RF 应用需求。

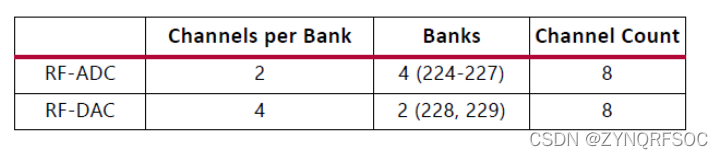

RFSOC8x8 3U算法评估模块化系统设计用 于集成到需要小尺寸,低功耗和实时处理的已部署RF系统中。 RFSOC8x8 XilinxZynq®UltraScale+™RFSoC Gen 1,具有8个RF-ADC和8个RF-DAC通。

XCZU27DR-2FFVG1157芯片有8路4.096G采样12位ADC,8路6.551G采样14位DAC

可以看出27DR具有8路瞬时2G带宽的高速ADC和DAC,这样一个片子可以具有8路,可以大大减少电路设计及PCB面积过大。

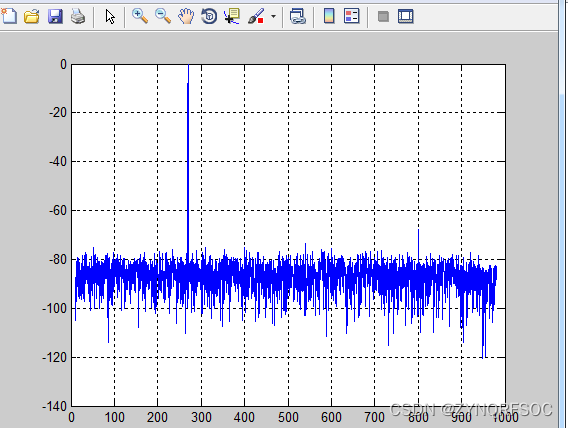

这里将ADC和DAC采样率设置4G,通过LMX2594进行配置,通过DDS给DA,然后通过射频连接线接到AD进行测试