本文转载自:FPGA技术实战的CSDN博客

引言:本文我们继续介绍7系列FPGA收发器架构的RX部分内容:

RX时钟输出控制结构

RX PRBS检查器

RX 8B/10B解码器

1.RX时钟输出控制结构

1.1 RX输出时钟结构概述

RX时钟分频器控制模块包括两个主要组件:串行时钟分频器和并行时钟分频器及其选择器控制。该RX时钟输出控制结构详细框图如图1所示。

图1、GTX/GTH收发器RX输出时钟结构

在图1中注意(图中绿色虚线内结构已经详细介绍过):

1.RXOUTCLKPCS和RXOUTCLKFABRIC为冗余时钟输出。RXOUTCLK推荐用于FPGA逻辑设计。

2.REFCLK_CTRL选项由软件自动控制,无需用户选择。用户只能使用IBUFDS_GTE2O输出端口或者ODIV2端口通过CMT或者BUFH,BUFG送入FPGA逻辑。

3.IBUFDS_GTE2是一个冗余时钟输出,它增加了时钟设计的灵活性。

4.每个GTX/GTH收发器的RX部分只有一个CPLL锁相环,QPLL输出时钟也可以用于GTX/GTH的RX接收部分。

5./4或者/5分频器由

GTXE2_CHANNEL/GTHE2_CHANNEL原句的RX_DATA_WIDTH属性控制。当RX_DATA_WIDTH = 16,32或者64时,选择/4分频器;当RX_DATA_WIDTH = 20,40或者80时,选择/5分频器。

6./2或者/4分频器由

GTXE2_CHANNEL/GTHE2_CHANNEL原句的RX_INT_DATAWIDTH属性控制。当RX_INT_DATAWIDTH= 0时(2字节内部数据路径),选择/2分频器;当RX_INT_DATAWIDTH= 1时(4字节内部数据路径),选择/4分频器。

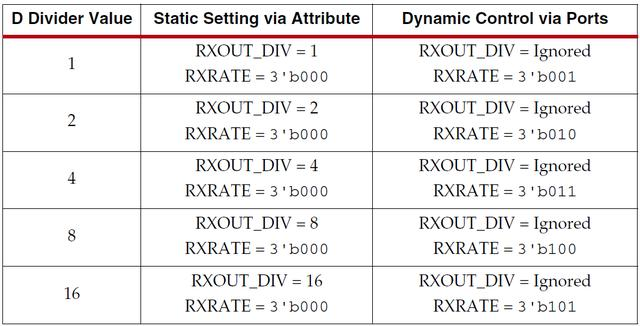

1.2 串行时钟分频器

每个发送器的PMA模块有一个D分频器用来分频来自PLL的时钟,以产生所需的线速率时钟。该D分频器可以设置为用于固定线速率的静态配置或者用于变化线速率的动态配置。图2显示了RX PLL D分频器输出配置。

图2、RX PLL输出分频器配置

1.3 并行时钟分频器和选择器

来自RX时钟输出模块的并行时钟可以用于FPGA逻辑设计,推荐RXOUTCLK用于FPGA内部逻辑设计,该时钟输出延迟可控。也可以将MGT管脚MGTREFCLK时钟直接输到FPGA内部作为逻辑时钟。

1.4 端口定义

图3显示了RX输出时钟模块端口定义。

图3、RX输出时钟模块端口定义

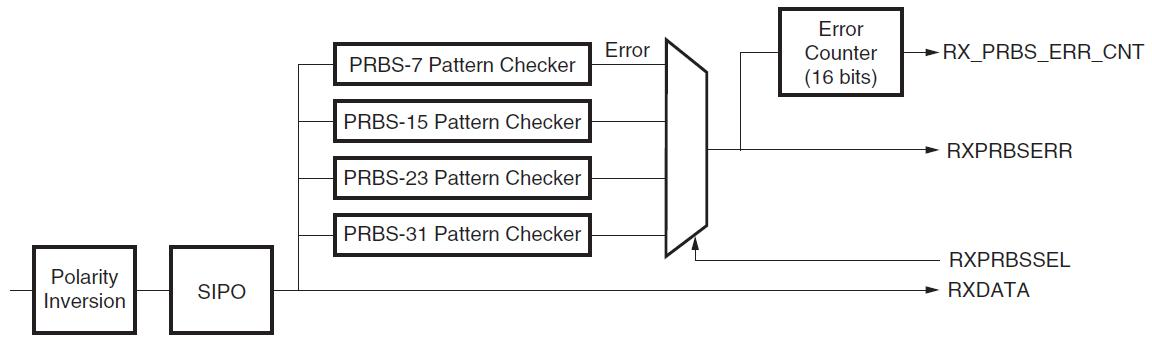

GTX/GTH收发器内置一个PRBS检查器,用来测试通道信号完整性。该检查器的结构如图4所示。

图4、RX PRBS检查器结构

3.RX 8B/10B解码器

3.1功能描述

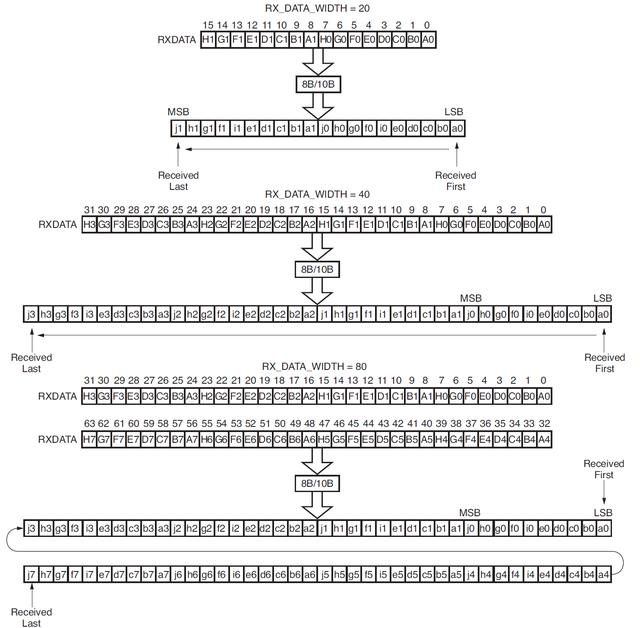

如果GTX/GTH收发器接收到的数据是8B/10B编码的,它必须在接收时解码。GTX/GTH收发器内置解码器,该解码支持2字节、4字节和8字节数据路径操作,产生K码字符和状态信息输出。如果接收数据没有进行8B/10B编码,则可以旁路该解码器。8B/10B解码器Bit和Byte顺序如图5所示。

图5、8B/10B解码器Bit和Byte顺序

3.2 RX运行不一致

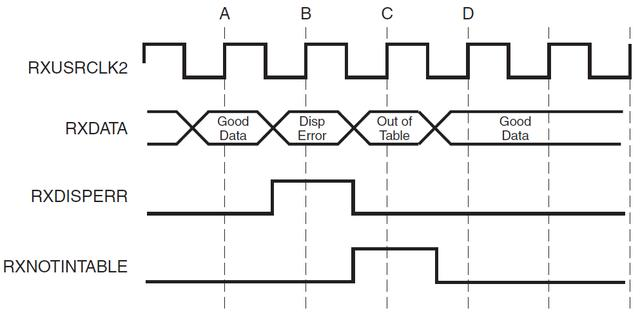

当检测到RXDATA出现运行不一致错误时,RXDISPERR为高电平;当检测到非法的8B/10B字符时,RXNOTINTABLE端口输出为高电平。图6显示了RX数据接口解码数据波形,图中A和D数据为正确数据,B和C为错误数据。

图6、RX数据8B/10B解码错误

3.3特殊字符

8B/10B解码器包括特殊字符(K字符)经常用于控制功能。当RXDATA检测到位K字符时,解码器驱动RXCHARISK为高电平。

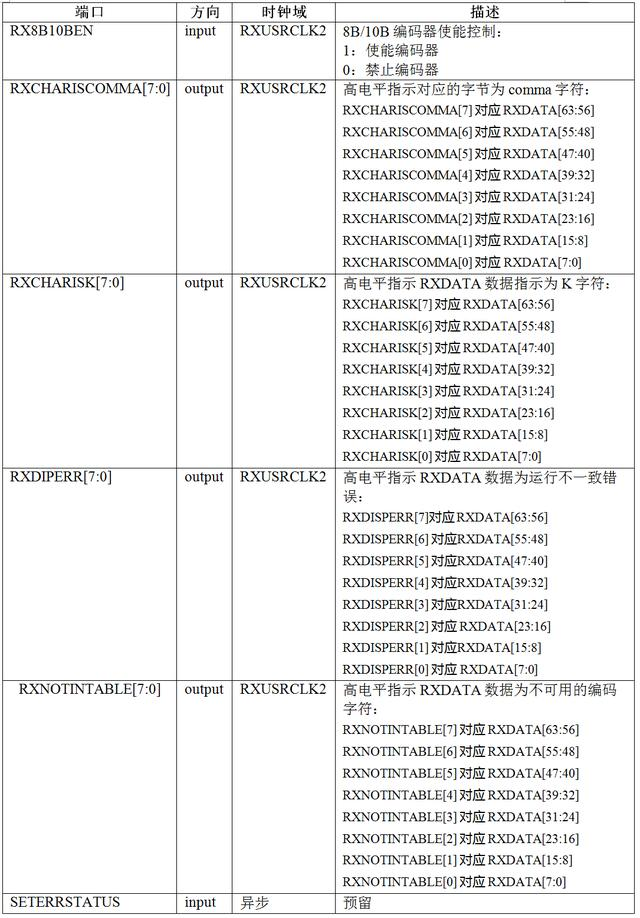

3.4 RX 8B/10B解码器端口

RX 8B/10B解码器端口定义如图7所示。

图7、RX 8B/10B解码器端口定义