本文转载自:FPGA技术实战的CSDN博客

引言:本文我们介绍FPGA SelectIO信号设计。本章提供了选择I/O标准、拓扑结构和终端的一些策略,并为更详细的决策和验证提供了仿真和测量方面的指导。在许多情况下,系统的高级方面(其他设备选择或标准支持)定义了要使用的I/O接口。在没有定义这些约束的情况下,由系统设计者选择I/O接口标准,并根据设计的目的对其进行优化系统。文章包含以下部分:

接口类型

单端信号

1.接口类型

为了更好地处理各种接口类型的细节,有必要首先将接口划分为多个类别。分为两个相关部分:

单端接口与差分接口

单数据速率(SDR)接口与双数据速率(DDR)接口

1.1 单端信号VS差分接口

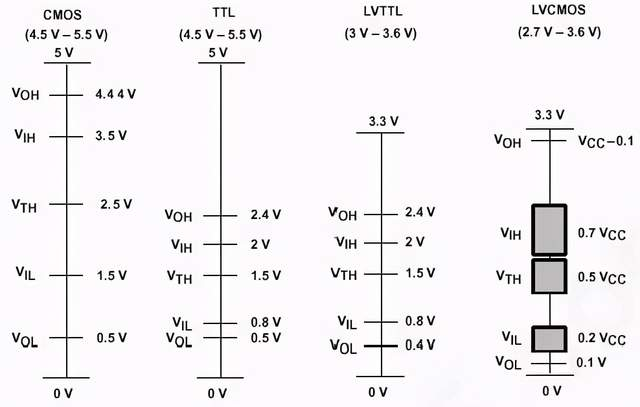

传统的数字逻辑使用单端信令——一种传输信号并假定驱动器和接收器共用GND的约定。在单端接口中,信号的断言(无论是高还是低)是基于其相对于固定电压阈值的电压电平,该阈值参考GND。当信号电压高于VIH阈值时,该状态被视为高。当信号的电压低于VIL阈值时,该状态被认为是低的。TTL是单端I/O标准的一个常见示例。

为了达到更高的接口速度和增加噪声容限,一些单端I/O标准依赖于精确的专用本地参考电压而不是GND。HSTL和SSTL是依赖VREF来解析逻辑电平的I/O标准的例子。VREF可以看作是一个固定的比较器输入。

高性能接口通常利用差分信号——一种传输两个相互引用的互补信号的约定。在差分接口中,信号的断言(无论是高还是低)是基于两个互补信号的相对电压电平。当P信号的电压高于N信号的电压时,该状态被认为是高的。当N信号的电压高于P信号的电压时,该状态被认为是低的。通常P和N信号具有相似的摆动,并且具有高于GND的共模电压(尽管情况并非总是如此)。LVDS是差分I/O标准的一个常见示例。

1.2 SDR VS DDR接口

单数据速率(SDR)和双数据速率(DDR)接口之间的区别与总线的数据信号与该总线的时钟信号之间的关系有关。在软件无线电系统中,数据只记录在接收设备的输入触发器上,在时钟的上升沿或下降沿。一个完整的时钟周期相当于一个位时间。在DDR系统中,数据在时钟上升沿和下降沿的接收设备的输入触发器上记录。一个完整的时钟周期相当于两位时间。SDR和DDR的区别与携带信号的I/O标准是单端还是差分无关。单端接口可以是SDR或DDR,差分接口也可以是SDR或DDR。

图1、SDR VS DDR接口

2.单端信号

7系列FPGA I/O中提供了多种单端I/O标准。有关支持的I/O标准的完整列表以及每种标准的详细信息,请参阅UG471:7系列FPGA SelectIO资源用户指南的“SelectIO资源”一章。该章末尾的表格总结了每个支持的I/O标准,哪些标准支持DRIVE和SLEW属性、双向缓冲区以及DCI选项。它还描述了高性能(HP)和高范围(HR)I/O组支持哪些I/O标准。

2.1 模式和属性

有些I/O标准只能在单向模式下使用,有些则可以在双向模式或单向模式下使用。

一些I/O标准具有控制驱动器强度和转换速率的属性,以及弱上拉或下拉和弱保持电路(不打算用作并行终端)的存在。驱动强度和转换率可用于调整接口以获得足够的速度,同时不过度驱动信号。弱上拉、弱下拉和弱保持器可用于确保浮动或3状态信号的已知或稳定水平。

《UG471,7系列FPGA选择资源用户指南》的“选择资源”一章介绍了哪些标准支持这些属性。有关详细信息,请参阅本用户指南信息。

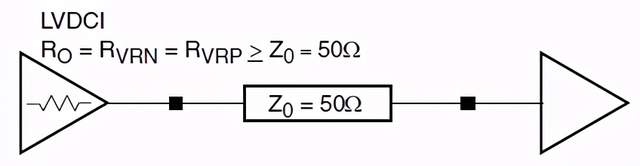

LVCMOS,当设置为6mA驱动和快速转换时,具有接近50Ω的近似输出阻抗,可以用作受控阻抗驱动器的粗略近似值。弱驱动器与传输线的阻抗匹配是近似的,并且随电压和温度的变化而变化。LVDCI和HSLVDCI,真正的控制阻抗驱动器,是自适应的,保持更接近的阻抗匹配,并保持恒定的过电压和温度。

2.2 输入阈值

单端标准的输入电路分为两类:具有固定输入阈值的电路和具有由VREF电压设置的输入阈值的电路。使用VREF有三个优点:

允许更严格地控制输入阈值水平

它消除了阈值参考对GND的依赖

它允许输入阈值更接近,从而减少了输入接收器处信号电压大幅度摆动的需要

图2、常用电平标准阈值

举例两个1.8V I/O标准:LVCMOS18和SSTL18 Class 1。1.8V LVCMOS的阈值设置为0.63V和1.17V(需要接收器处的信号至少摆动540mV以进行逻辑转换)。SSTL18等级1的阈值设置为VREF–0.125V和VREF+0.125V,或标称VREF为0.9V,设置为0.775V和1.025V(要求接收器处的信号至少摆动250 mV,以进行逻辑转换)。所需的较小摆动允许在整个链路中进行更高频率的操作。驱动器的较小摆幅意味着需要较少的瞬态电流来降低直流功率。使用VREF的缺陷是,只要在需要VREF电源的Bank中使用I/O标准,Bank的多功能VREF引脚就不能用作I/O。但是,对于7系列器件,可以使用多功能VREF引脚提供参考电压,也可以选择使用内部VREF功能在内部生成参考电压。有关内部VREF的更多详细信息,请参阅UG471,7系列FPGA选择用户指南。有关VREF去耦和所有其他电源去耦的更多信息,请参阅第2部分配电系统。

2.3 拓扑和端接

拓扑通常指接口中驱动器、接收器、互连和终端的布置。在单向拓扑中使用的技术不同于在双向拓扑中使用的技术,因此对它们进行分开介绍。选择符合标准(SSTL、LVCMOS等等)可以根据标准的字母(由EIA/TIA或JEDEC等标准机构发布)使用,也可以与来自另一标准或混合I/O的驱动程序或接收器混合和匹配。I/O标准规范可以定义接收器的VIL和VIH等限制,也可以定义每个方面包括驱动器阻抗和转换速率、PCB走线长度和拓扑结构、无源终端的值和位置、接收设备的最大输入电容,甚至最大输入电容数接收器。有许多关于拓扑和终端的设计策略,这些策略影响了接口的信号完整性。通过仿真和测量验证每个接口的信号完整性是非常重要的。端接通常指用于保持接口中信号完整性的阻抗匹配或阻抗补偿装置。虽然许多类型的元件可用作终端(如电阻器、电容器、二极管),但本讨论仅限于电阻终端。一般来说,电容器和二极管端接技术更为复杂。

2.3.1 单端拓扑和端接

单向拓扑的包括点到点和多点拓扑。点对点拓扑有一个驱动器和一个接收器,而多点拓扑有一个驱动器和多个接收器。拓扑是点对点还是多点定义了接口的重要方面,这些方面决定了哪些终止策略是合适的,哪些是不合适的。

1.单端点对点拓扑

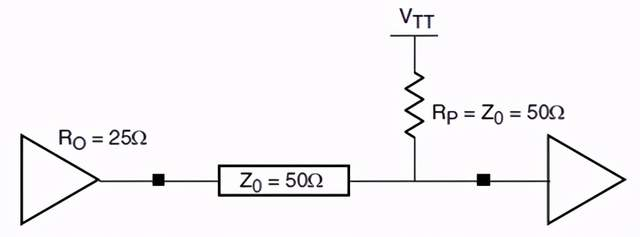

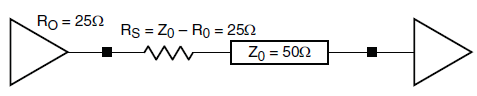

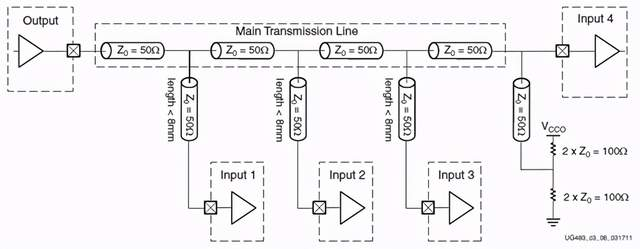

最简单的单向拓扑是点对点形式。也就是说,有一个驱动器和一个接收器。终端(如有)可包括接收器处的并联终端(图1)、驱动器处的串联终端(图2)或受控阻抗驱动器(图3和图4)。始终使用IBIS模拟来确定这些终端的最佳电阻值、VTT电压电平和VRN/VRP参考电阻。

图3、并行端接单向点对点拓扑

图4、串联端接单向点对点拓扑

图5、DCI控制阻抗驱动器单向点对点拓扑

图6、 弱驱动,单向点对点拓扑

通常,并联电阻终端(RP)的值等于其终端传输线的特性阻抗(Z0)。串联电阻终端(RS)的值等于传输线(Z0)的特性阻抗减去它们所连接的驱动器(RO)的输出阻抗。对受控阻抗驱动器进行调谐,以使驱动器输出阻抗(RO)等于其终端传输线的特性阻抗(Z0)。

假设传输线的特性阻抗为50Ω,驱动器输出阻抗(RO)为25Ω,则25Ω串联终端(图4)或50Ω并联终端(图3)是合适的。受控阻抗驱动器,无论是用DCI还是用弱LVCMOS驱动器实现,其大小应为50Ω的输出阻抗(RO,图5)。对于DCI,这对应于等于50Ω的VRN和VRP电阻器。6 mA至8 mA驱动强度的弱LVCMOS驱动器的输出阻抗约等于50Ω(图6)。

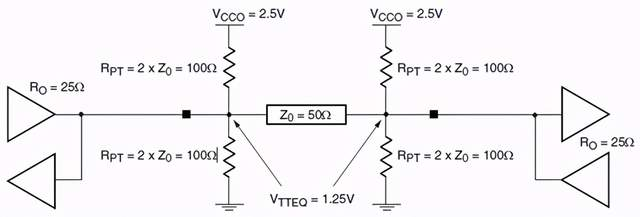

通常,当VTT(连接到并联端接电阻器的电压源)等于信号电压的一半时,并联端接具有最佳性能。对于2.5V信号(VCCO=2.5V),VTT理想情况下为1.25V。在该电压不可用的情况下,可以使用戴维南并联终端。戴维南并联终端由一个分压器组成,其并联等效电阻(RPEQ)等于传输线的特性阻抗(大多数情况下为50Ω)。分压点设计为VTT。图7显示了由2.5V VCCO供电的戴维南并联终端,由两个100Ω电阻器组成,产生1.25V的VTT和50Ω的并联等效电阻(RPEQ)。

并联端接可能不如串联端接或受控阻抗驱动器理想,因为它会消耗更多的功率。这种权衡必须与其他权衡权衡,以确定接口的最佳终端拓扑。

图7、戴维南并联终端

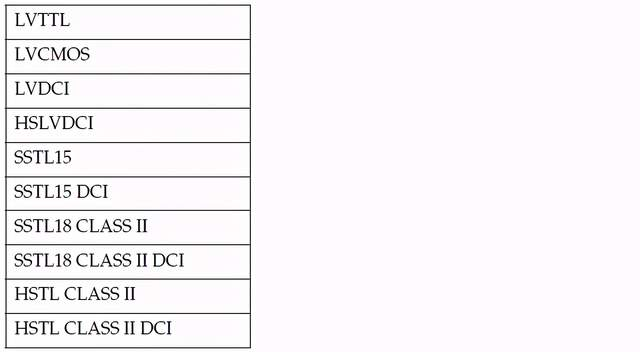

表1列出了可用于单向点到点拓扑的I/O接口类型示例。

表1、可用于单向点到点拓扑的I/O接口类型示例

LVTTL和LVCMOS没有明确任何规范的端接方法。驱动器处的串联端接或接收器处的并联端接都是合适。

LVDCI隐式使用受控阻抗驱动器端接,在接收器不需要任何形式的端接。

每I/O标准对终端技术有不同的要求。在某些情况下,I/O标准的规范可以严格定义终端拓扑。具有特定终端要求的标准示例是HSTL。HSTL I类是一种单向I/O标准,建议在接收器处进行并行端接。在HSTL I级的情况下,终端电压VTT定义为电源电压VCC的一半。设计人员最终可以选择完全不使用终端,或者使用不同的终端,例如驱动程序处的串联终端。在给定的系统中,这种选择可能是有利的,原因有很多。由设计人员通过模拟和测量验证接收器处的信号完整性是否足够。

SSTL标准对终端拓扑没有严格的要求。相反,JEDEC规范提供了通常使用的拓扑图的示例端接技术。UG471,7系列FPGA SelectIO Resources用户指南的“SelectIO Resources”一章为每个I/O标准(包括SSTL标准)提供了示例终止技术,目的是为考虑提供一个良好的起点。与HSTL类似,最终由设计者通过模拟和测量来验证接收器处的信号完整性是否足够。

2.单向多点拓扑

在更复杂的拓扑中,一个驱动器可以驱动多个接收器。接收器代表必须由单个传输线短接线馈电的负载。从信号完整性的角度来看,在这种情况下使用的最佳拓扑是一条长传输线,驱动器在一端,平行终端在另一端,接收器通过中间的短线连接到主记录道。这种拓扑通常被称为飞越多点拓扑(flyby multi-drop)。

这种拓扑有两个关键方面。第一种是在传输线的远端存在一个并联终端端接。不得在驱动器或受控阻抗驱动器处使用串联终端。并行端接是该拓扑唯一适用的端接类型。第二个关键方面是每个接收器的连接短截线的长度。这些必须保持短:长度不超过信号上升时间的一小部分。当典型信号上升时间为600 ps时,应使用长度不超过700 ps/4=150 ps或0.9英寸(22.86 mm)的短截线。随着短截线变长,它们对沿传输线传输的信号呈现较大的阻抗不连续性,并且可以支持显著的反射。这些阻抗的不连续性破坏了信号。随着负载数量的增加和存根长度的增加,信号已损坏到不再可用的程度。

不建议使用星形拓扑图。设计具有良好信号完整性的星状拓扑所涉及的限制超出了本文件的范围。

如单向点对点拓扑图所述,理想的并联电阻终端的值等于其终端传输线的特性阻抗。当VTT等于信号电压的一半时,可获得最佳性能,当此电压不可用时,建议使用戴维南并联终端,如前一节所述。

图8显示了由VCCO供电的戴维南并联终端,由两个100Ω电阻器组成,产生VCCO/2的VTT和50Ω的并联等效电阻。该图显示了一个驱动器(LVCMOS驱动器)和四个驱动器的拓扑结构接受者司机在左边,接收器间隔在50Ω传输线的中间点,两个100Ω电阻器的戴维南并联终端位于右侧。

图8、基本多点拓扑

主传输线应尽可能短。对于大多数I/O标准,只要保持精确的跟踪阻抗并避免串扰源,最长可达20英寸或以上的长度是可行的。主传输线路中间段的长度不必相等。它们的相对长度可以是任意的。沿着主传输线的不同点的接收器接收具有不同延迟量的信号,但是所有信号上升时间都是相似的。

从主传输线延伸到各个接收器的短截线必须尽可能短。这些存根越长,接收到的波形就越损坏。需要仿真和测量来评估各个接收机的信号完整性。

表2列出了可用于单向多点拓扑的I/O接口类型示例。

表2、可用于单向多点拓扑的I/O接口类型示例

LVTTL和LVCMOS没有指定明确的端接方法。在长T型线末端并联端接是一种合适的端接方法。

2.3.2 双向拓扑和端接

双向拓扑包括点到点和多点拓扑。点对点拓扑结构有两个收发器(驱动器和接收器共用一个设备管脚),而多点拓扑结构可以有多个收发器。拓扑是点对点还是多点定义了接口的重要方面,这些方面决定了哪些终止策略是合适的,哪些是不合适的。

1.双向点对点拓扑

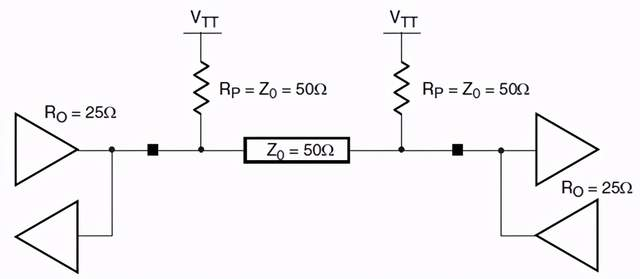

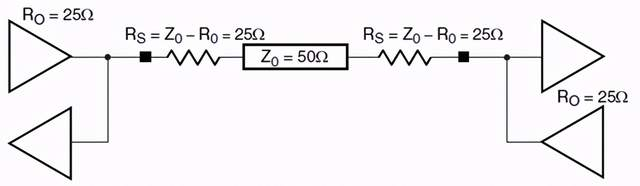

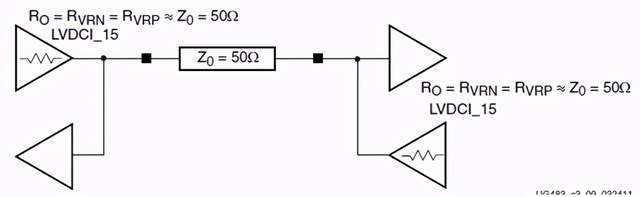

最简单的双向拓扑是点对点拓扑。也就是说,有两个收发器通过传输线连接。因为双向接口需要在两个方向上都同样良好地工作,所以拓扑的对称性是可取的。虽然非对称拓扑可以设计为具有相当好的信号完整性,但确保良好信号完整性的最简单方法是保持拓扑对称。因此,链路一侧使用的任何终端也应在链路的另一侧使用。串联终端(图10)很少适用于双向接口,因为接收收发器的串联电阻器会衰减输入信号。并行端接(图9)几乎总是在两种情况下都能获得更好的信号电平接收器。受控-阻抗驱动器,无论是以弱LVCMOS驱动器的形式粗略地控制,还是以LVDCI或HSLVDCI的形式自适应地控制,都可以获得如图11、图12所示的良好效果,以及图13(使用低驱动强度LVCMOS驱动器实现)。始终使用IBIS模拟来确定这些终端的最佳终端电阻值、VTT电压电平和VRN/VRP参考电阻值。

图9、并行端接双向点到点拓扑

图10、串联端接双向点到点T拓扑:不推荐

图11、DCI控制阻抗双向点到点拓扑

图12、HSLVDCI控制阻抗驱动器双向点到点拓扑

图13、“弱驱动”双向点对点拓扑

通常,并联电阻终端(RP)的值等于其终端传输线的特性阻抗Z0。有些接口,如DDR2内存接口,使用75Ω终端电阻而不是50Ω,以打开数据眼图。在这种情况下,取舍是眼睛高度与阻抗不连续的少量信号反射。受控阻抗驱动器通常进行调谐,以便驱动器输出阻抗(RO)等于其端接传输线的特性阻抗(Z0)。

假设传输线的特性阻抗为50Ω,驱动器输出阻抗为25Ω,50Ω并联终端是合适的(图9)。无论是使用DCI还是使用弱LVCMOS驱动器实现的可控阻抗驱动器,其大小应为50Ω的输出阻抗(RO)。使用受控阻抗驱动器的一个例子是LVDCI15 I/O标准。通过使用50Ω外部精密电阻器放置在该组的VRN和VRP引脚上,该组的受控输出阻抗将为50Ω。如果VRN和VRP引脚上已经需要100Ω电阻器(用于创建等于50Ω的戴维南等效分裂终端电路),并且同一组中需要50Ω受控阻抗驱动器,则可以使用“DIV2”版本的驱动器来实现,如LVDCI_15 I/O(图11和图3-12)。6 mA至8 mA驱动强度的弱LVCMOS驱动器的输出阻抗约等于50Ω(图13)。

当VTT(连接到并联端接电阻器的电压源)等于信号电压的一半时,并联端接具有最佳性能,因为这通常是数据眼的中心电压。对于2.5V信号(VCCO=2.5V),VTT理想情况下为1.25V。在该电压不可用的情况下,建议使用戴维南并联终端。戴维南并联终端由一个分压器组成,其并联电阻等于传输线的特性阻抗(大多数情况下为50Ω)。分压点设计为VTT。图14说明了由2.5V VCCO供电的戴维南并联终端,由两个100Ω电阻器组成,产生1.25V的VTT和50Ω的并联等效电阻(RPEQ)。

并联端接可能不如串联端接或受控阻抗驱动器理想,因为它会消耗更多的功率。这种权衡必须与其他权衡权衡,以确定接口的最佳终止拓扑。

图14、戴维南并联终端(双向点对点拓扑)

表3列出了可用于双向点拓扑的I/O接口类型示例。

表3、双向点对点I/O拓扑的I/O接口类型示例

LVTTL和LVCMOS没有指定任何规范的终止方法。对于双向接口,不建议使用串联端接。然而,并行终止和弱驱动都是合适的。

LVDCI和HSLVDCI都隐式地使用受控阻抗驱动端接。

HSTL Class II规定了两个收发器的并行终端。终端电压VTT定义为电源电压VCCO的一半。设计者可以选择完全不使用终端或使用不同的终端。由设计人员通过模拟和测量验证接收器处的信号完整性是否足够。

STL的JEDEC规范提供了串联端接和并联端接的示例。终端电压VTT定义为电源电压VCCO的一半。虽然规范文件提供了描述驱动器串联端接的示例,但需要注意的是,这样做的目的是试图使驱动器的阻抗与传输线的阻抗相匹配。由于7系列FPGA SSTL驱动器的目标输出阻抗接近40–50Ω,因此无需任何外部源串联终端即可实现更好的信号完整性。在可能的情况下,考虑使用3态DCI I/O标准(“T_DCI”)是一个更好的起点,该标准提供仅当输出缓冲器处于3态时才存在的内部并行终端电阻器。设计者应通过仔细的模拟和测量,在接口(通常为DRAM ICs)和终端拓扑中,仔细选择7系列设备的I/O标准、驱动器强度和其他设备的模上终端(ODT)选项。有关可用I/O标准和选项的更多详细信息,请参阅UG471,7系列FPGA SelectIO用户指南。

2.双向多点拓扑

在更复杂的拓扑中,多点总线中的任何收发器都可以发送到所有其他收发器。通常这些拓扑只能以非常慢的时钟速率运行,因为它们只支持非常慢的信号上升时间(10 ns到50 ns)。虽然在某些情况下有用,但缺点通常大于好处。设计这些具有良好信号完整性的拓扑所涉及的限制超出了本文件的范围。