本文转载自:FPGA技术实战的CSDN博客

引言:传输线沿其长度定义并控制特性阻抗。然而,它们接口的三维结构在信号路径上没有容易定义的或恒定的阻抗。计算10Gb/s信号通过这些结构时所看到的阻抗,需要3D场解算器等软件工具,而2D场解算器足以计算传输线特性阻抗。PCB设计人员可以使用本章中的分析和示例来辅助此类通道的设计。本章未涉及的案例可能需要进一步仿真和分析。

1.冗余电容和电感

大多数差分跃迁都是通过电容。P和N路径相互耦合,增加了电容。许多跃迁在宽频带上具有与集总电容相同的频率响应。通过设计,增加电感可以抵消这种过剩。

通过设计,除了受到密度和物理限制的影响外,在许多情况下,增加电感可以消除这种过剩电容。虽然盲孔、较大间距的焊球和非常小的通孔焊盘等技术降低了电容,但它们在设计中并不总是可行的。

时域反射(TDR)技术,无论是通过仿真还是测量,都允许设计者识别过渡过程中的冗余电容或电感。

2.时域反射法(TDR)

为了进行TDR测量,将阶跃输入应用于互连。通过观察反射信号,可以确定电压阶跃穿过互连时所经历的冗余电容或电感的位置和大小。

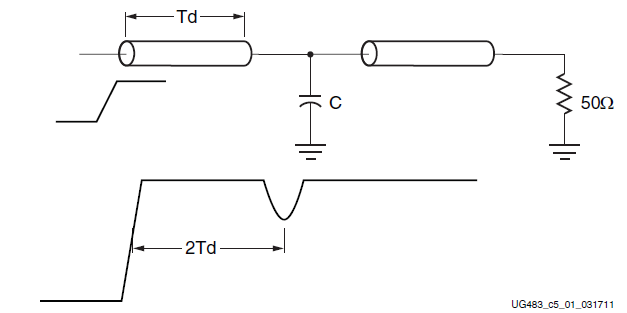

并联电容(见图1)会导致阻抗的瞬时下降,而串联电感(见图2)则会导致相反方向的阻抗不连续。Td是通过左侧第一个传输线段的传播延迟。由于阻抗不连续而产生的反射波需要2*Td才能返回TDR端口。如果信号通过传输线的传播速度已知,则可以计算出沿通道的冗余电容或电感的位置。

图1、并联电容的TDR特征

图2、串联电感的TDR特征

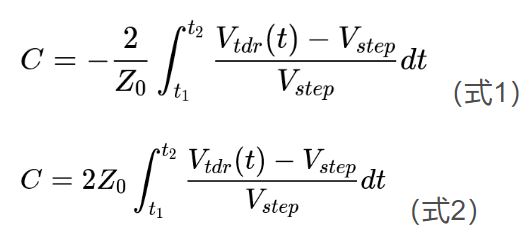

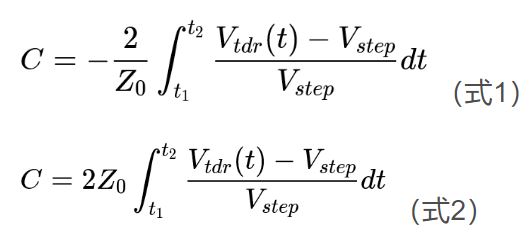

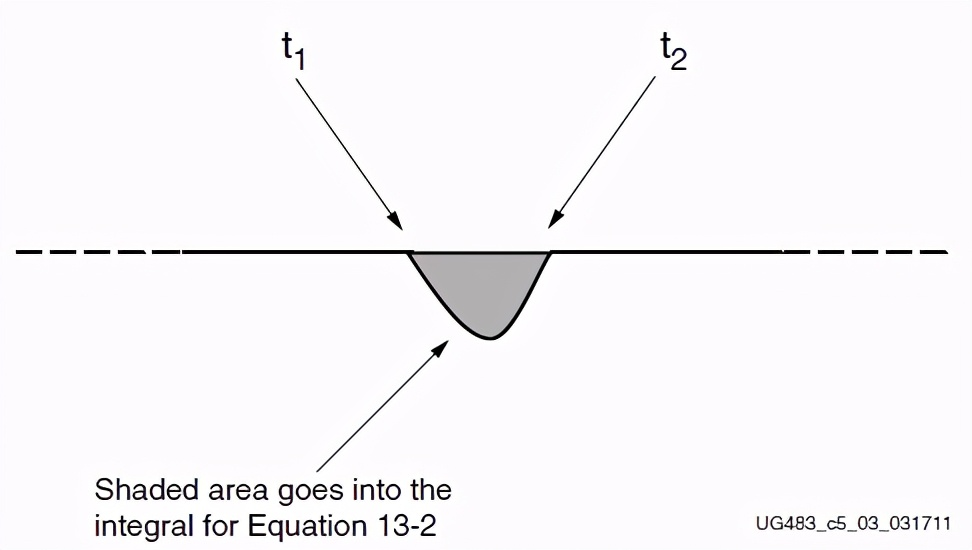

这种冗余电容(C)或电感(L)的大小也可以通过积分跃迁的TDR的归一化面积从TDR波形中提取反应。反应电容和电感的相应方程式为:

图3显示了归一化TDR区域的积分。

图3、归一化TDR面积的积分

利用这些方程得到的结果对上升时间变化不敏感,并且对于仿真TDR测量是有效的,前提是前后传输线非常接近50Ω。然而,对于实际测量,精度非常依赖于Z0。

3.BGA封装

BGA封装中的每个信号路径都经过精心设计,以优化信号完整性。支持单端I/O的走线通常设计为50Ω的阻抗。支持高速SERDES I/O的走线设计为标称100Ω差分阻抗。在设计信号路径时要特别小心,以优化不连续性,如焊球和基板过孔,以尽量减少它们对信号完整性的影响。采用三维全波电磁解算器和矢量网络分析仪对封装性能进行建模和测量。

4.SMT焊盘

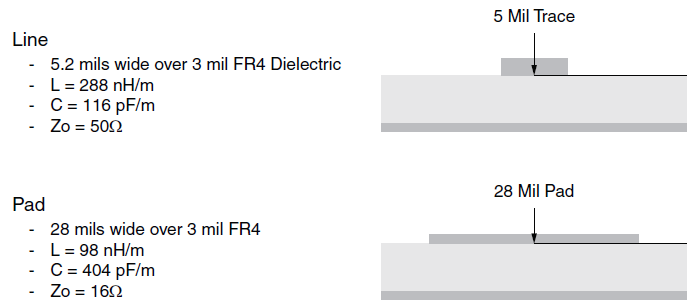

对于需要在发送器和接收器之间进行交流耦合的应用,在通道中引入SMT焊盘以允许安装耦合电容器。标准SMT焊盘由于对附近基准面的板电容而具有冗余电容。在图4示例中,一个5 mil的走线(Z0为50Ω)过渡到一个0402 SMT焊盘,其宽度为28 mils,全部超过3 mils的FR4。

图4、5 Mil走线和28 Mil焊盘的2D场解算器分析

在这些尺寸上使用2D场解算器,5mil走线的Z0为50Ω。0402焊盘的Z0为16Ω,因为焊盘的电容太大,电感太小,导致阻抗小于50Ω。此转换的性能可以通过以下两种方式之一进行优化。

第一种方法使走线与焊盘的宽度相同,并将接地层移到层叠中更深的位置,以将过渡段的Z0保持在50Ω。这种方法不需要任何特殊的分析,但由于贴片电容器体的边缘电容会产生一定的误差。走线密度是有限的,因为走线现在是28mil宽。

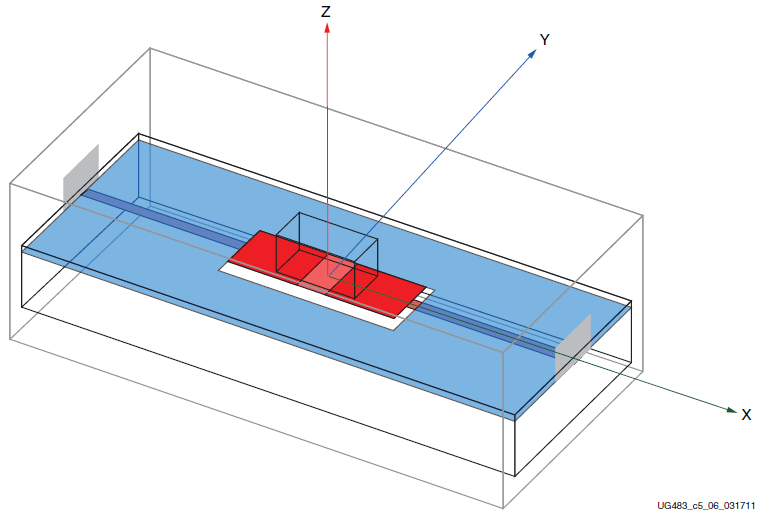

第二种方法,如图5所示,清除焊盘下方的接地层,从而消除焊盘和接地层之间的板电容引起的大量多余电容。这种技术允许比第一种方法更大的走线密度,但需要三维场解算器分析或测量以及几个电路板迭代来获得所需的性能。

图5、传输优化

二维场解算器的例子表明,如果清除焊盘走线下的地平面,可以获得接近50Ω的电阻。然后使用三维场解算器在更大程度上验证该结果准确。图6所示的地平面与二维模拟时完全相同。在HFSS中使用频域分析,使用这种技术可以使回波损耗提高20dB(10x)。

图6、Pad清除的Ansoft HFSS模型

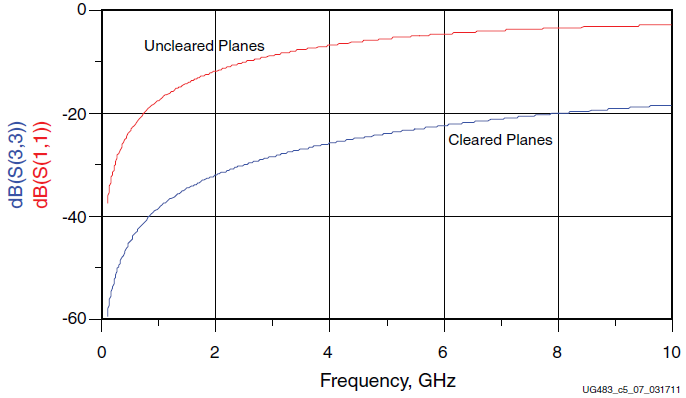

图7显示了0402焊盘结构与线性比例之间的回波损耗比较。

图7、0402焊盘结构的回波损耗比较

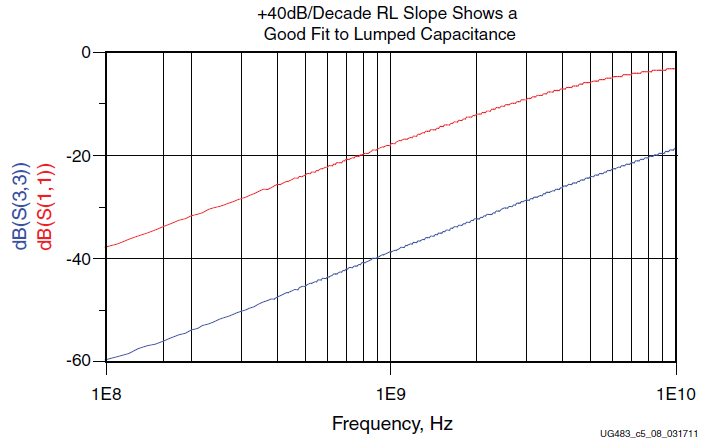

图8中约-40 dB/decade的斜率与集总电容器的频率响应非常吻合。

图8、0402焊盘结构在对数(频率)尺度上的回波损耗比较

接下来,使用HFSS中模拟的同一跃迁的仿真测量,可以通过对早期频域分析的S参数结果进行TDR来测量该跃迁的时域性能。

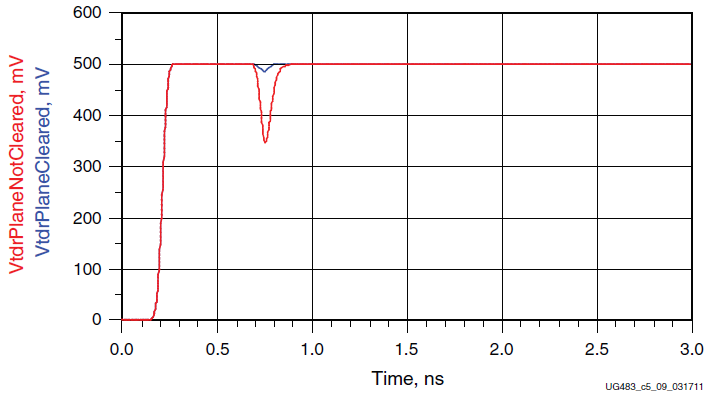

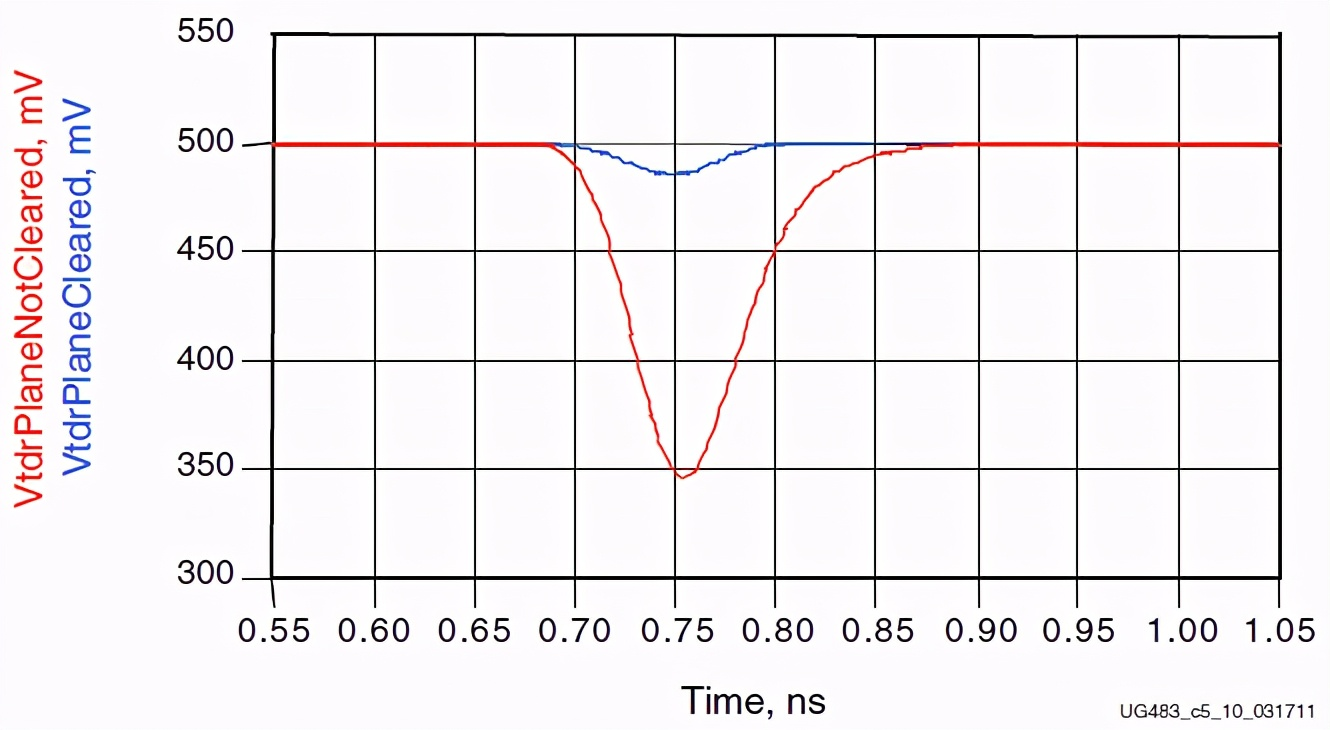

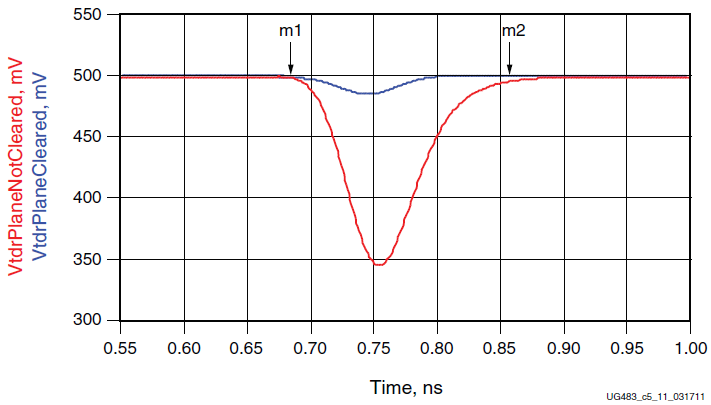

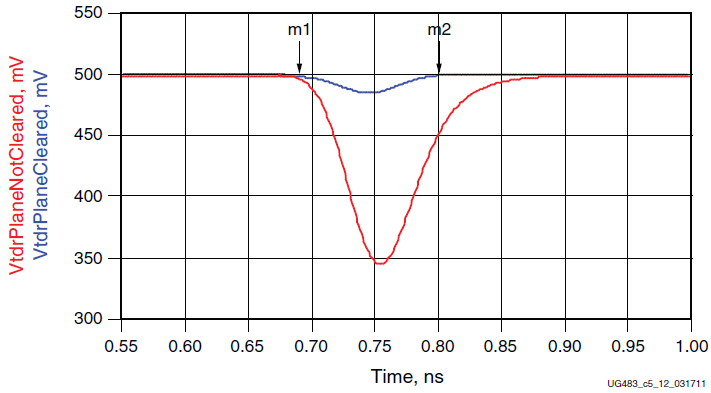

在图9和图10中,具有大电容倾角的红色曲线对应于SMT焊盘,而没有从下面清除接地层。蓝色曲线显示,清除接地层可以去除大部分多余的电容。这种改进可以用等式1和等式2进行量化。

图9、0402焊盘结构的TDR结果对比

图10、0402焊盘结构的TDR结果对比

图11、接地层完好时840 fF的过剩电容

图12、57 fF接地层完整时的过剩电容

最常见的传输是差分过孔,其中信号对必须从上带状线层或顶部微带过渡到下带状线层或底部微带。

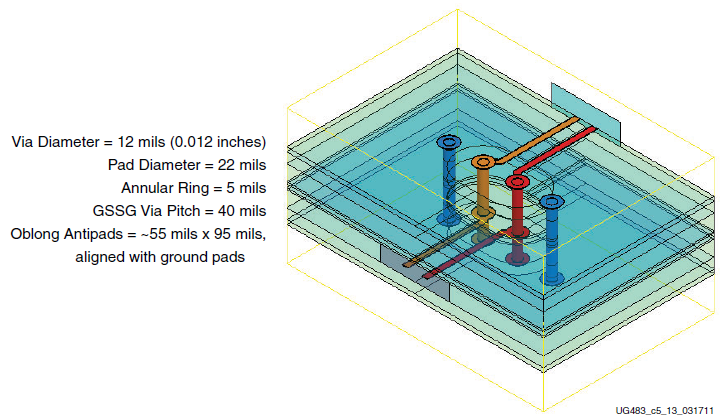

图13所示为接地信号接地(GSSG)型差分通孔。接地过孔连接到层叠中的每个接地层,而信号层仅包含入口层和出口层的焊盘。

图13、差分通孔设计示例

GSSG通孔的一个关键优点是,它允许信号的返回电流在相应信号通孔附近的接地过孔中流动,从而减少过大的电感。信号路径在差分信号的P和N半部分之间也是对称的,这对于控制由于P/N不平衡引起的共模伪影是至关重要的。

较大的长方形反焊盘减少过孔体和周围平面边缘之间的多余边缘电容。未使用的焊盘也会被移除。

一个好的起点是使用图13所示的尺寸作为80mil的差分过孔设计示例。为了适应密度约束或缺乏密度约束,可以相应地缩放尺寸,以保持每个尺寸相对于其他尺寸的比率。这种缩放保持了差分过孔的阻抗性能,同时允许总尺寸的变化以更好地适应特定应用。这些最终尺寸受到可制造性和密度约束的限制。

虽然通孔长度可以少量改变,以适应比80mil更厚或更薄的板示例,但是改变过孔长度相对于其他尺寸的比率会影响过孔的阻抗。对于差分过孔的这种和其他配置,最好使用三维场解算器工具模拟模型,以确保达到性能目标。

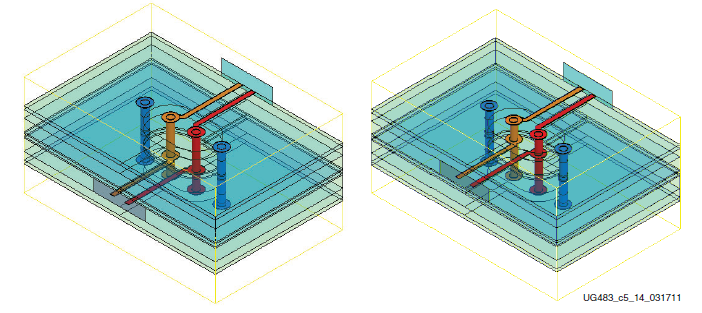

图14、引脚L11和L6的16层PCB中的差分GSSG过孔

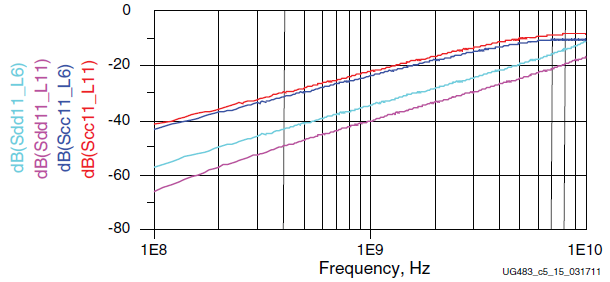

作为一般规则,P和N路径在传输过程中需要保持相等的长度。在可能的情况下,通过将信号穿过过孔的整个长度,应将通孔存根(sub)长度保持在最小值。图5-15所示的分析比较了共模(SCC11)和差分(SDD11)响应的S参数回波损耗。

图15、比较L11和L6 GSSG过孔的差模和共模损耗的模拟回波损耗

从图15中的图表来看,共模响应在回波损耗方面差20 dB。与差分响应相比,共模响应差得多,这就是为什么在进入传输之前尽可能减少P/N偏差是一个好主意的原因。60/40的经验法则是1 GHz时40 dB的回波损耗,这意味着60 fF的过剩电容。因为过剩电容是单极响应,所以可以使用简单的外推规则。例如,如果返回损耗移到34 dB,则多余电容将增加一倍。由于GSSG通孔的优异性能,即使是长通孔存根也最多只能使差分通孔的电容增加一倍。

6. P/N交叉过孔

一些收发器提供独立切换发送和接收信号对极性的能力。此功能消除了在板级交叉P/N信号的需要,从而显著增强了信号完整性。如果可能,应避免P/N交叉过孔,并应使用收发器的极性开关。

7. SMA连接器

设计良好的SMA连接器可以减少调试时间,并允许在第一次通过时正确设计高性能通道。为了达到这一性能目标,需要对10Gb/s下性能良好的形状记忆合金连接器进行模拟、设计和制造。供应商还可以提供设计服务,确保连接器在特定板上正常工作。装配指南对于确保连接器与电路板的匹配过程得到良好控制以提供指定的性能至关重要。

Xilinx使用Rosenberger和其他精密连接器制造商生产的精密SMA连接器,因为它们具有优异的性能和上一段中列出的要点。

8. 背板连接器

背板连接器存在许多信号完整性问题,包括:

P/N信号偏差

串扰

连接器引脚导致的短截线

一些连接器制造商不仅提供连接器的参数、模型和布局指南,还提供设计支持、研讨会和教程。

9. 微带/带状线弯曲

当差分走线通过90°角时,外部走线比内部走线长,这会导致P/N不平衡。即使在一个单一的走线内,信号电流也有拥抱拐角内侧走线的趋势,从而进一步减少通过弯道的实际延迟。

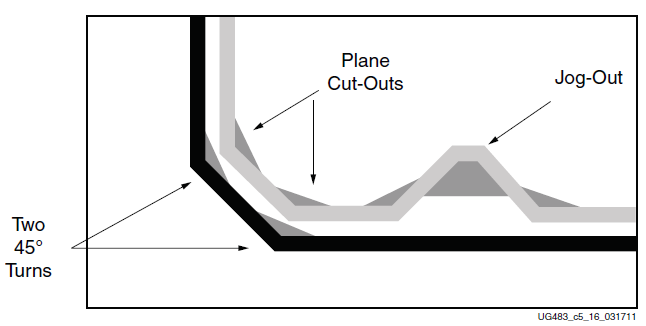

为了使P和N路径之间的倾斜最小化,微带线或带状线中的90°匝被布置为两个45°弯曲以提供斜角。添加一个jog out还允许跟踪长度匹配。图16显示了走线中的弯曲示例。

图16、走线中90度转弯的设计示例

匝数增加了电容,因为90°角处的走线宽41%。45°转弯时,差值减小到8%。在30mil的深度上增加平面开孔可以减少多余的电容量。

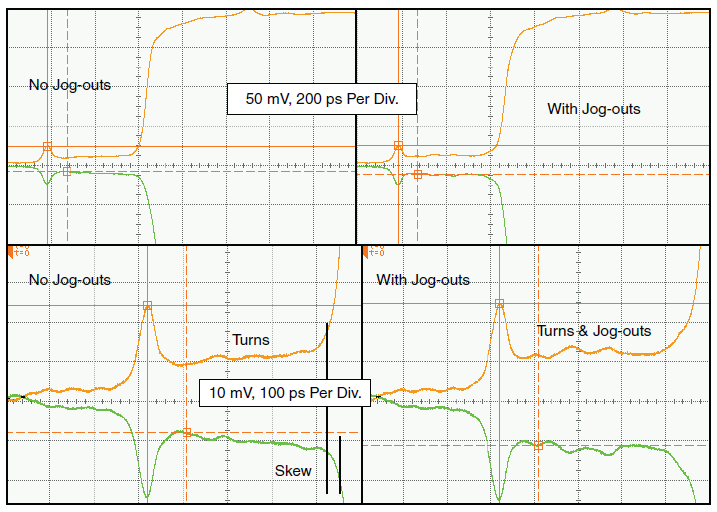

当用缓动切口和平面切口仿真这种斜接弯曲时,减少了多余电容,改善了P/N长度和相位匹配。如果没有Jog-out,P/N长度不匹配为16mil。给定FR4材料,16mil的差异转化为5Ghz下有4.8°的相位失配,或10Gb/s下2.68ps(0.0268ui)。

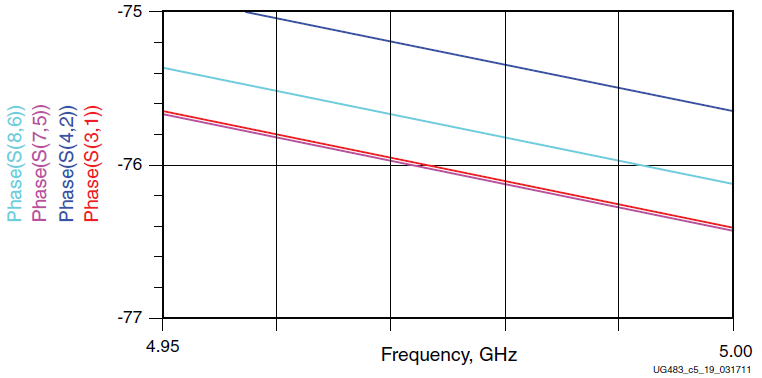

图17至图19显示,相位失配减少到0.75°,使用缓动器和Jog-out,相位失配减少到0.3°。结合缓动和Jog-out的仿真结果表明,该结构的剩余电容减小到65fF。

设计人员试图加宽线路,以补偿由于线路分离和耦合不太强烈而增加的特性阻抗。然而,即使没有加宽线路,转角和Jog-out的组合电容仍然是过电容的,因此缓动输出的非耦合部分不能加宽。

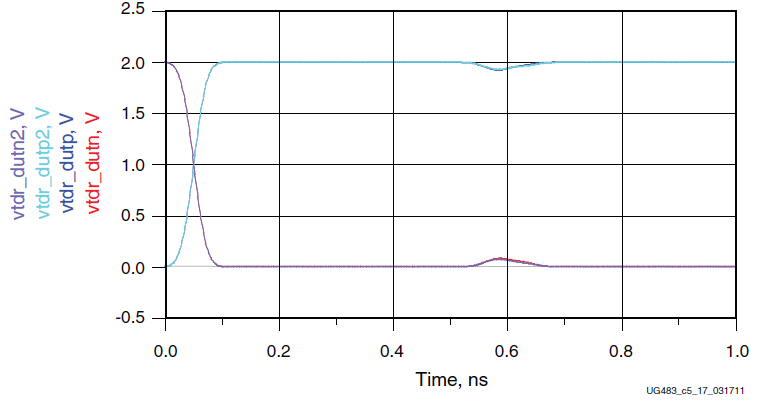

图5-17:带有Jog-out的45度转弯的仿真TDR

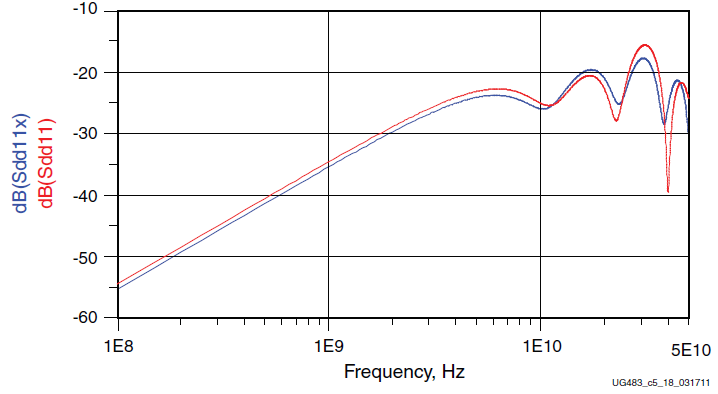

图18、带有Jog-ou的45度转弯的仿真回波损耗

图5-19:带有Jog-out的45度转弯的仿真相位响应

图20、45度转弯的测量TDR,带和不带折弯