本文转载自:FPGA技术实战CSDN博客

引言:从本文开始,我们介绍下项目中设计的并行LVDS高速DAC接口设计,包括DAC与FPGA硬件接口设计、软件设计等。项目设计高速DAC采用了ADI公司的AD9129,该芯片最大更新速率5.7Gsps,该芯片在宽带通信应用、LTE、雷达信号产生、干扰机等领域有广泛应用。

1. AD9129概述

AD9129是高性能14位RF数模转换器(DAC),支持最高达2.85GSPS的数据速率。DAC内核基于一个四通道开关结构,使双边沿时钟能够有效运行,配置为混频模式(Mix-Mode™)或2倍插值时,能将DAC更新速率提高至5.7GSPS。在混频模式中,AD9129可在二阶和三阶奈奎斯特区内重构RF载波,同时仍保持高达4.2GHz的出色动态范围。其高性NMOS DAC内核具有四通道开关结构,能以最小输出功耗实现业界领先的直接RF频率合成性能。输出电流可以在9.5mA至34.4mA范围内进行编程。

图1:AD9129系统框图

2.AD9129接口描述

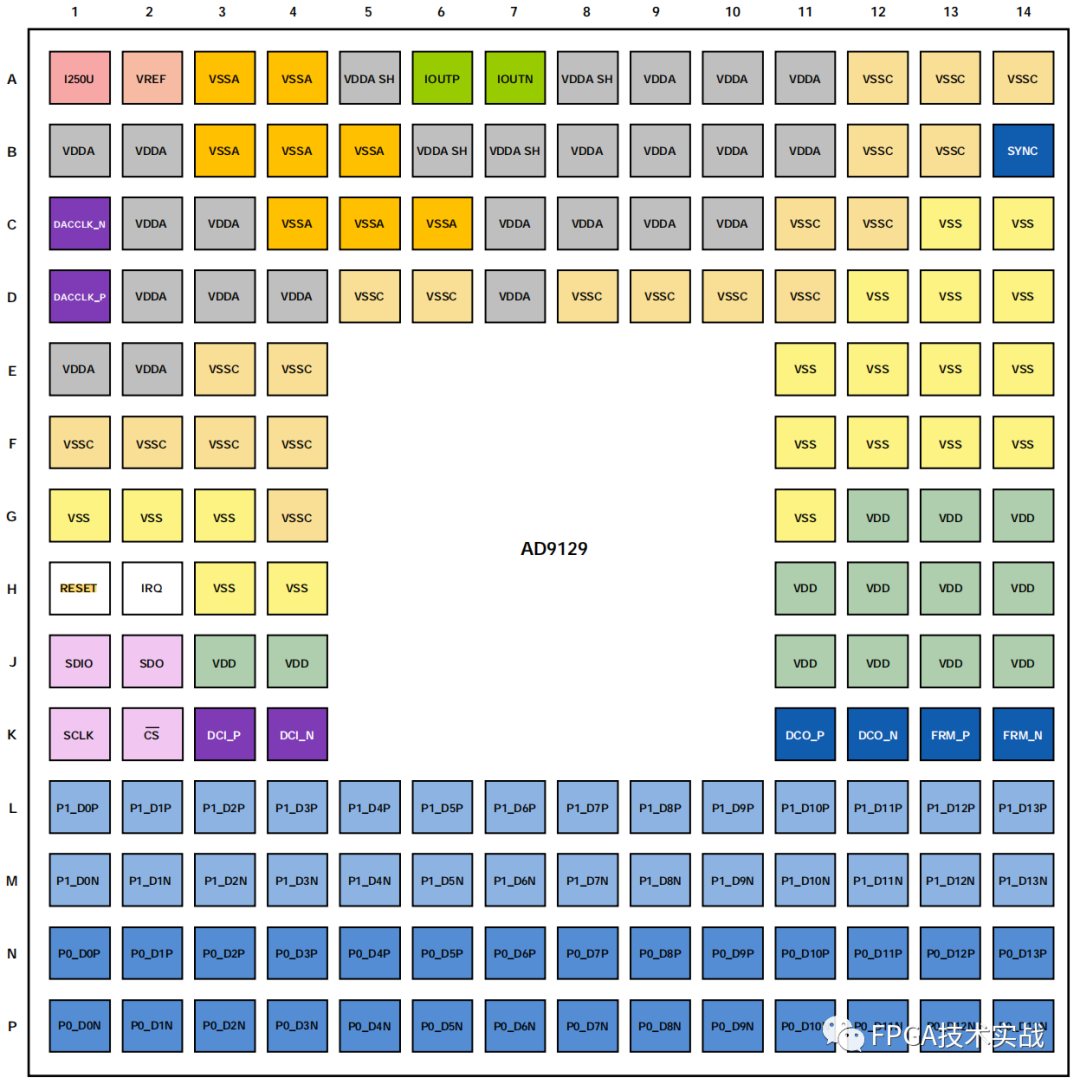

图2:AD9129管脚分布

如图1所示,AD9129接口主要分为与主机FPGA互联的控制接口(包括SPI接口、复位等)和LVDS源同步数据接口,参考电压接口,DAC时钟接口(包括DCO_x、DACCLK_x)以,DAC模拟输出接口以及供电接口(图1中未标出)。

2.1控制接口

AD9129控制接口包括SPI接口、复位接口。SPI接口包括四个信号:SCLK、CSn、SDO、SDIO,通过该接口可以实现DAC内部寄存器的配置。SPI接口支持MSB(最高有效位)优先和LSB(最低有效位)优先传输格式。AD9129串行接口端口可以配置为单I/O引脚(SDIO),或者配置为两个单向输入/输出引脚(SDIO和SDO)。SCLK最大工作时钟为20MHz。

复位信号RESET为高电平复位,如果未使用此管脚,需接地处理。SPI及RESET接口电平为1.8V IO。

2.2 LVDS源同步数据接口

AD9129数据输入接口为LVDS源同步数据接口,包含源同步时钟DCI、两组数据接口P0_D和P1_D,分辨率为14bits。LVDS接口电平为1.8V,典型输入阻抗为100Ω。

AD9129与FPGA之间的接口关系如下图所示。

图3:AD9129与FPGA之间的接口关系

2.3参考电压VREF接口

AD9129输出电流由数字控制位和I250U基准电流共同设置,如图下图所示。

图4:基准电压源电路

将VREF施加于I250U(引脚A1)与VSSA之间的4.0 kΩ外部电阻,便可获得基准电流。1.0 V标称参考电压(VREF)在4.0 kΩ电阻中产生250 µA基准电流。配置基准电压电路应注意以下几点限制:

• 为使器件正常工作,4.0 kΩ电阻和1 nF旁路电容均是必需的。

• 将DAC输出满量程电流IOUTFS调整为默认设置20 mA以外的值时,应以数字方式执行。

• AD9129不是乘法DAC,不支持用交流信号对基准电流I250U进行调制。

• VREF引脚上的带隙电压必须缓冲才能用于外部电路,因为其输出阻抗约为7.5 kΩ。

• 可以将一个外部基准源连接到VREF引脚,以过载内部基准源。

2.4时钟接口

DAC时钟接口包括DAC工作时钟DACCLK_x和DCO_x时钟。DACCLK_x时钟用于设置DAC的更新速率,还路由至时钟分配模块以产生所有关键的内部和外部时钟DCO_x。DCO_x=1/4*DACCLK_x。DCO时钟与DCI时钟频率相同,以建立同步操作,如图3所示。

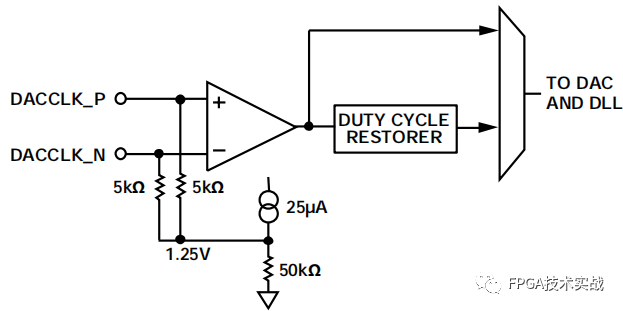

图5:DACCLK_x时钟输入

DACCLK_x输入连接到一个高频PLL以确保DAC采样时钟可靠地锁定输入时钟。PLL默认使能,上电后即锁定。

图6:DACCLK_x输入的可能信号链

DACCLK_x输入的峰峰值电压为0.25~2V,典型值为1V,共模电压为1.25V。DACCLK_x输入时钟频率范围为1.4G~2.85GHz。

DCO_x时钟输出时钟阻抗100Ω,最大时钟712.5MHz,输出电压为1.025~1.375V,共模电压为1.25V。

DACCLK_x差分时钟可以接受正弦信号;如果输入信号电平保持在0dBm以上,则NSD(噪声谱密度)性能降低可忽略不计。−5dBm输入时,性能降低+1dB;当信号接近−10dBm时,性能进一步降低,达到+2dB。时钟接收器之后有一个占空比恢复器(DCR),用于确保后续电路的占空比接近50%。DCR的输出用作主时钟,直接路由至DAC。此外时钟源的质量是保持最佳交流性能的重要考虑因素,可从三方面来定义:相位噪声特性、抖动和驱动能力。

2.5模拟输出接口

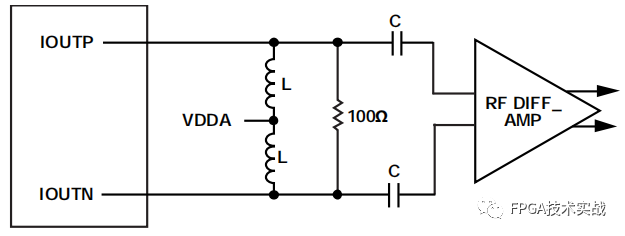

AD9129提供互补电流输出IOUTP和IOUTN,吸收外部负载的电流,外部负载由1.8 V VDDA电源供电。

2.5.1峰值DAC输出功率能力

差分电流输出DAC的最大峰值功率能力取决于峰值差分交流电流IPEAK和等效负载电阻。对于具有50 Ω源端接电阻的1:1巴伦,DAC交流电流源的等效负载为25 Ω。如果AD9129设置IOUTFS = 20 mA,则其峰值交流电流为9.375 mA,提供给等效负载的峰值功率为2.2 mW(即P = I2R)。由于1:1巴伦的源电阻和负载电阻相等,因而此功率由二者均分。所以,输出负载获得1.1 mW或0.4 dBm的峰值功率。

要计算提供给负载的均方根功率,需考虑以下事项:

• 数字波形的峰值与均方根之比

• 相对于数字满量程的任何数字倒退

• DAC sinc响应和外部网络中的非理想损耗

2.5.2输出级配置

AD9129设计用于需要宽信号重构带宽或高IF/RF信号产生的高动态范围系统。最佳交流性能只有在以下情况下才能实现:DAC输出配置为差分(即平衡)工作模式,输出共模电压偏置到稳定的低噪声1.8 V标称模拟电源(VDDA)。用于与DAC接口的输出网络应提供接近0 Ω的直流偏置路径以连接到VDDA。在整个频率范围内,IOUTP和IOUTN引脚之间的任何输出阻抗不平衡都会降低失真性能(主要是偶数阶失真)和噪声性能。元件选择和布局对于实现AD9129的潜在性能至关重要。大多数要求平衡到不平衡转换且工作频率为10 MHz到1 GHz的应用,都可以利用Mini-Circuits JTX系列变压器,它可提供2:1和1:1的阻抗比。

图7:宽带应用的推荐变压器,带宽上限高达2.2 GHz

图7显示AD9129与JTX-2-10T变压器接口。此变压器可提供出色的幅度/相位平衡(<1 dB/1°,最高1 GHz),通过提供0 Ω直流偏置路径以连接VDDA。如果需要滤除DAC镜像和时钟成分,可在单端侧应用一个模拟LC滤波器,其好处是可以保持变压器的平衡。

图8:DAC输出与自偏置差分增益级接

图8显示了将DAC输出与自偏置差分增益模块接口时可以考虑的接口。电感(L)用作RF扼流圈,提供直流偏置路径以连接到VDDA。其值与隔直电容一起决定复合通带响应的截止频率下限。(隔直电容与RF差分增益级的输入电阻一起形成高通响应。)

许多RF差分放大器由两个增益匹配的单端放大器组成,因而无法提供共模抑制,而且由于匹配不佳,还可能降低平衡。此外,由于元件容差,差分LC滤波器可能会进一步降低差分信号路径的平衡。两种情况下,使用巴伦均非常有利,可在滤波或进一步放大之前,抑制RF DAC的共模失真和噪声成分。

图9:建议混频模式配置,提供扩展的RF带宽,采用TC1-1-13M+巴伦

对于在混频模式下使用AD9129且输出频率超过2.2 GHz的应用,用户可以考虑图9所示的电路。此电路采用宽带巴伦(例如4.0 GHz时为−3 dB)来为DAC输出提供直流偏置路径,其配置与图7所示范例相似。此电路是在评估板上实现,结果如图10所示。

图10:实测与理想DAC输出响应,fDAC = 2.6 GSPS

2.6电源接口

AD9129电源分为模拟电源和数字电源,整个芯片最大功耗在1.1W左右。

模拟电源VSSA=-1.5V,Imax=54mA;

模拟电源VDDA=1.8V,Imax=230mA;

数字电源VDD=1.8V,Imax=336mA。

3.小结

本文简单介绍了AD9129的基础知识,包括芯片的重要特性,外部接口相关的信号特性等。下一篇我们重点介绍下项目中FPGA与AD9129互联的原理图设计,包括LVDS IO接口设计、时钟电路以及供电设计。