本文转载自: FPGA的现今未微信公众号

通过前面的文章(基于FPGA的RGMII接口设计(一)——GMII到RGMII的转换),了解了接口转换模块实现双沿采样数据到单沿采样数据的转换,同时提供时钟、数据相位的调整,来确保数据的正确采样。采样回来后的数据,要通过解析,数据校验等功能后,最后得到正确的报文,实现这个过程的模块就是MAC(Media Access Control),它属于数据链路层的介质访问控制子层。本文主要是记录MAC在RGMII接口中的设计。

总计介绍

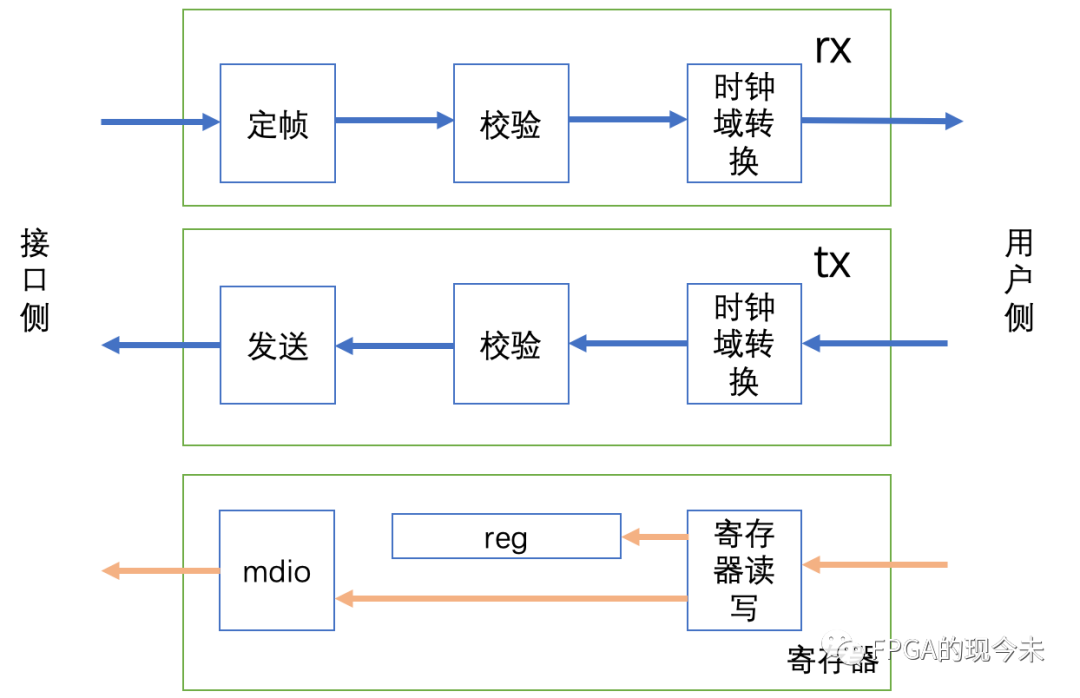

要实现这个设计,我们就要知道为了实现双方的通信,MAC的基本功能有哪些?那肯定就有报文的发送和接收,在接收的过程中,先要定帧才能找到报文的开始,找到报文后,要进行一系列的校验,比如CRC、超长报文、超短报文检测等。在发送的过程中,也要对报文继续长度检测,同时要计算CRC,方便对端校验。因此一个MAC的基本设计框图就如下所示:

接受RX方向

1、定帧

先看下物理层的数据格式:

每个报文前面有preamble(前导码)和sfd(帧起始定界符),其中前导码是7个或者以上的8'h55组成,帧起始定界符固定为8‘hd5,后来才是真正的报文和CRC,其中报文和CRC的长度为64——1518之间。

在RX方向,定帧就是要找到报文中的SFD,一般采用状态机,当报文到来后,先确实是否有7+个的8'h55,然后再等待一个8'hd5,如果找到就定帧成功,否则就要重新定帧。

2、校验

定帧后得到报文+CRC,校验主要做3件事情,判断CRC是否正确,判断报文是否超长,判断报文是否超短。如果上述3个判断都OK,则表示为一个合法的报文,否则就是非法报文,对于非法报文有2种处理方式,第一就是丢弃,第二就是打上错误标记后给到后续用户逻辑。考虑到通用性,应该采用寄存器可配置的方式给用户选择是丢弃还是打上错误标记后给用户逻辑。

3、时钟域转换

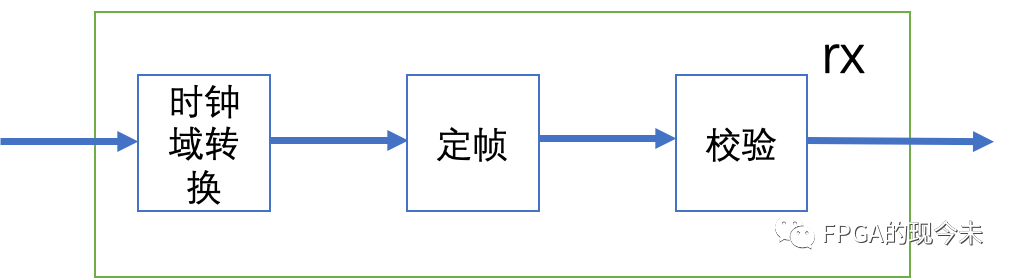

我们知道,在RX方向,有数据和随路时钟,整个系统的系统时钟一般不会用这个随路时钟。当收到数据后,送给用户的时候,就会出现随路时钟到系统时钟的转换。比如随路时钟是125M,系统时钟是100M或者200M。这里想说明的是,究竟应该在哪里做时钟域转换?这里有2种方案,第一种如上图所示,整个rx工作在随路时钟,第二种就是收到数据后,先从随路时钟转到系统时钟,然后再定帧。如下图所示:

从功能上讲,两者之间没有差异,当随路时钟不是很好的时候,采用第二种方案就更好一些。

发送TX方向

1、时钟域转换

这里的时钟域转换是把系统时钟转换成125M的发送时钟,和RX方向的的时钟域转换类似,需要注意的是,如果系统时钟也是125M,那就可以直接用系统时钟作为TX方向的发送时钟;如果不是,就需要做时钟域转换。

2、校验

发送部分的校验主要也是干3件事情,第一是检测用户发来的数据是否超长,第二是检测用户发来的数据是否超短,如果是的话,要么丢弃,要么就将超长报文截短、超短报文补齐到最小包长后再发送。第三个事情就是计算CRC,将计算得到的CRC添加到报文的尾部。

3、发送

发送部分将校验后得到的报文,按照报文格式发送,主要是添加7个byte的8‘h55和1个Byte的8’hd5.

寄存器

作为一个通用的MAC模块,需要有一些基本的统计,最常见的统计有如下几类:

1、输入输出报文个数的统计、报文字节数统计;

2、每秒钟输入输出报文个数的统计、报文字节数统计;

3、超长、超短报统计、CRC错误报文统计、丢弃报文统计;

4、超短、超长报文长度的值可读写、丢包使能可读写、

除了上述统计外,对于外部PHY芯片的寄存器(通常是MDIO接口),也需要可读写,如上述方案图所示,寄存器读写接口译码后分成2个通道,一个是访问MAC本身的寄存器,一个是访问PHY芯片的寄存器,这里需要做一个接口转换,即寄存器接口(可以是localbus或者axilite接口)到MDIO接口的转换。

总结

FPGA供应商一般都会提供MAC的IP(比如Xilinx的Tri Mode Ethernet MAC),那到底什么时候用厂商的?什么时候用自己写的呢?其实能用IP的尽量用IP,当然前提是该IP的使用被验证是可行的。当我们对资源非常敏感,或者使用的低端器件不支持该IP,或者需要有一些定制化的需求时,当然是自己开发比较好。