文章来源:硬件设计与测试微信公众号

XILINX高速收发器GTX/GTH高速串行通信的收发器,它可以支持多种协议,如PCIe Gen1/2/3,SATA 1.5/3/6 Gbps,Ethernet 1/10/40 Gbps, Fibre Channel等。

GTX的组成主要包括以下几个模块:

- GTXE2_CHANNEL:包含一个PLL和一个TX/RX对,可以独立配置和使用。它是一个独立的模块,它包含了收发器的核心逻辑,如编码/解码,序列化/反序列化,对齐,锁相环等功能。

- GTXE2_COMMON:包含一个PLL和四个TX/RX对,可以共享一个参考时钟和一个恢复时钟。它是一个共享的模块,它包含了时钟管理,参考时钟缓冲,电源管理等功能。

- GTXE2_INT:包含一个PLL和八个TX/RX对,可以共享一个参考时钟和两个恢复时钟。

- GTXE2_TOP:包含四个GTXE2_INT模块,可以实现32个收发器通道。

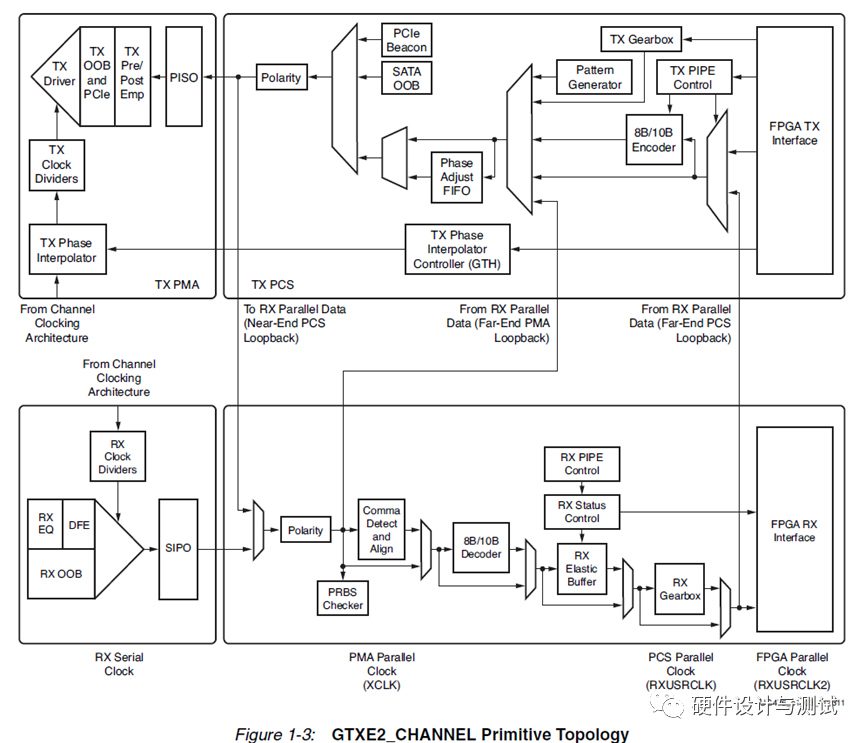

GTXE2_CHANNEL Primitive由以下几个主要部分组成:

- PMA(Physical Medium Attachment):负责实现收发器的物理层功能,包括编码/解码,串行/并行转换,时钟恢复,电平转换等。

- PCS(Physical Coding Sublayer):负责实现收发器的链路层功能,包括对齐,同步,8B/10B或64B/66B编码/解码,信号检测等。

- TX Buffer:负责缓存发送数据,并提供时钟域转换和数据宽度转换功能。

- RX Buffer:负责缓存接收数据,并提供时钟域转换和数据宽度转换功能。

- TX Reset Controller:负责控制发送端的复位和初始化过程。

- RX Reset Controller:负责控制接收端的复位和初始化过程。

- TX Config Controller:负责控制发送端的配置参数,如预加重,摆幅,极性等。

- RX Config Controller:负责控制接收端的配置参数,如均衡器,采样相位,极性等。

- TX PLL:负责提供发送端所需的时钟信号。

- RX PLL:负责提供接收端所需的时钟信号。

以下主要介绍PMA和PCS:

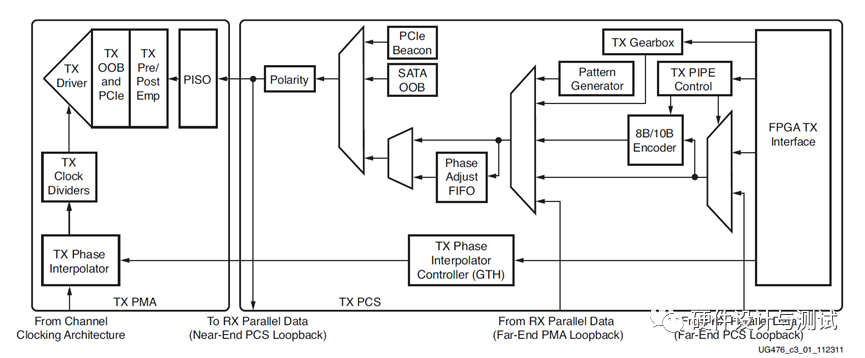

TX PMA

TX PMA是GTXE2_CHANNEL Primitive的发送端的最底层模块,它负责将并行数据转换为高速差分信号,并通过输出缓冲驱动器(OBUFDS)发送到外部接口。

TX PMA由以下几个子模块组成:

- TX PLL:用于产生发送端所需的时钟信号,包括参考时钟(REFCLK)、反馈时钟(FBCLK)、输出时钟(OUTCLK)和字节时钟(BYTECLK)。TX PLL可以根据不同的协议和数据速率进行配置,支持动态重配置(DRP)和动态相位调整(DPA)功能。

- TX 8B/10B 编码器:用于将8位并行数据转换为10位编码数据,以提高信号完整性和可靠性。编码器可以根据不同的协议选择不同的编码方式,如K28.5、D10.2等。编码器还可以插入特殊字符,如逗号、对齐字符等,以实现帧同步和数据对齐。

- TX 数据对齐器:用于将10位编码数据按照字节边界进行对齐,并根据输出时钟的相位进行调整,以保证数据在输出缓冲驱动器之前达到稳定状态。数据对齐器还可以根据不同的协议选择不同的对齐方式,如无对齐、逗号对齐、K28.5对齐等。

- TX 预加重器:用于对输出信号进行预加重处理,以补偿传输线路上的信号衰减和失真。预加重器可以根据不同的线路特性和数据速率进行配置,支持线性预加重和指数预加重两种方式。

- TX 输出缓冲驱动器:用于将差分信号从内部电平转换为外部电平,并提供足够的驱动能力和阻抗匹配。输出缓冲驱动器可以根据不同的协议和数据速率进行配置,支持LVDS、LVPECL、CML等多种输出模式。

RX PMA

RX PMA是GTXE2_CHANNEL Primitive的发送端的最底层模块,它负责将差分信号转换为单端信号,并进行相应的处理的部分。

RX PMA由以下几个部分组成:

- RXBUF:接收缓冲器,用于提供一定的缓冲能力,以适应不同的数据速率和时钟域。

- RXCDR:接收时钟数据恢复器,用于从接收到的数据中提取时钟,并根据时钟对数据进行采样和对齐。

- RXDFE:接收数字前馈均衡器,用于补偿信道损耗和干扰,提高信号质量。

- RXPCS:接收物理编码子层,用于对接收到的数据进行解码、去除填充字符、检测错误和生成状态信号。

- RXPMACLK_SEL:接收PMA时钟选择器,用于选择合适的时钟源,以驱动RX PMA的各个部分。

TX PCS

TX PCS是一种用于编码和解码数据的物理层功能,它可以提高数据的可靠性和效率。

TX PCS的功能包括:

- 8B/10B编码:将8位的数据转换为10位的代码,以减少直流分量和提高时钟恢复能力。

- 帧同步:在每个GTXE2_CHANNEL Primitive的开头添加一个特殊的字符,以便接收端识别数据的边界。

- 帧校验序列(FCS):在每个GTXE2_CHANNEL Primitive的末尾添加一个校验值,以便接收端检测数据的完整性和正确性。

- 异步对齐标记(AAM):在每个GTXE2_CHANNEL Primitive之间添加一个空闲字符,以便接收端调整数据的对齐方式。

- 异常处理:在发生错误或异常情况时,发送端可以发送一些特殊的字符,以通知接收端采取相应的措施。

GTXE2_CHANNEL Primitive的TX PCS组成可以根据不同的应用场景进行配置,例如:

- 单PCS模式:每个GTXE2_CHANNEL Primitive只包含一个TX PCS,适用于低速或简单的数据传输。

- 多PCS模式:每个GTXE2_CHANNEL Primitive包含多个TX PCS,适用于高速或复杂的数据传输。

- 混合PCS模式:每个GTXE2_CHANNEL Primitive包含不同数量或类型的TX PCS,适用于灵活或定制的数据传输。

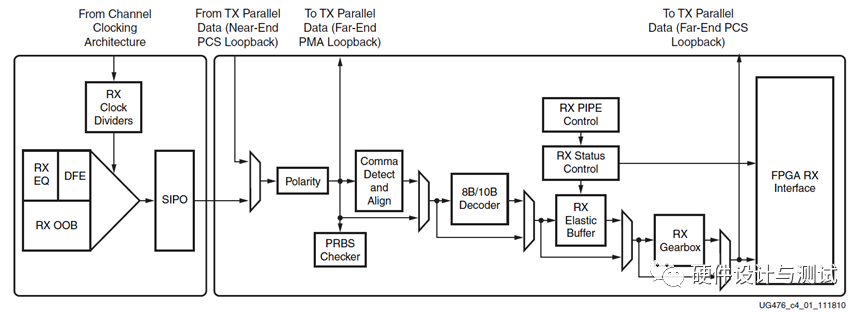

RX PCS

RX PCS(Physical Coding Sublayer)模块用于实现数据的解码、对齐、解扰和错误检测等功能。接收器的物理编码子层,它负责将串行数据流转换为并行数据,并进行必要的同步和校验。

RX PCS的功能包括:

- 串行数据恢复器(SDR):它使用一个相位锁定环(PLL)来恢复串行数据的时钟,并对齐数据的边沿,以便正确地采样和解码。

- 8B/10B解码器:它将每10位的串行数据转换为8位的并行数据,并检测是否有任何编码错误或不平衡的信号。

- 弹性缓冲器(EB):它是一个先进先出(FIFO)缓冲区,用于吸收时钟域之间的频率差异,并保持数据的完整性。

- 字节对齐器(BA):它是一个状态机,用于检测特殊的对齐字符(K28.5),并将数据流划分为字节边界,以便后续的处理。

- 帧对齐器(FA):它是另一个状态机,用于检测特殊的帧开始字符(K28.1),并将数据流划分为帧边界,以便后续的处理。

- 帧校验器(FC):它是一个逻辑模块,用于计算每个帧的循环冗余校验(CRC)值,并与接收到的CRC值进行比较,以检测是否有任何传输错误或数据损坏。

RX PCS由以下几个部分组成:

- RXDATA:这是一个32位的数据总线,用于传输从物理层接收到的原始数据。

- RXCOMMADET:这是一个逗号检测器,用于识别物理层协议中定义的特殊字符,如K28.5、K30.7等。这些特殊字符用于实现数据的对齐、同步和控制等功能。

- RXSLIDE:这是一个滑动缓冲区,用于存储从RXDATA接收到的数据,并根据RXCOMMADET的输出进行数据的移位和对齐。RXSLIDE可以配置为8位或10位模式,以适应不同的物理层协议。

- RXCHARISCOMMA:这是一个逻辑判断器,用于判断从RXSLIDE输出的数据是否为特殊字符。如果是,则输出一个高电平信号。

- RXBUF:这是一个缓冲区,用于存储从RXSLIDE输出的数据,并根据RXCHARISCOMMA的输出进行数据的分组和解扰。RXBUF可以配置为8B/10B或64B/66B模式,以适应不同的物理层协议。

- RXNOTINTABLE:这是一个错误检测器,用于判断从RXBUF输出的数据是否符合物理层协议中定义的编码规则。如果不符合,则输出一个高电平信号,表示发生了编码错误。

- RXDATAOUT:这是一个32位的数据总线,用于传输从RXBUF输出的解扰后的数据。

- RXBYTEISALIGNED:这是一个逻辑判断器,用于判断从RXBUF输出的数据是否已经正确对齐。如果是,则输出一个高电平信号,表示数据已经对齐。

- RXBYTEREALIGN:这是一个字节重对齐器,用于根据RXBYTEISALIGNED的输出进行数据的重排和对齐。RXBYTEREALIGN可以配置为8位或32位模式,以适应不同的用户接口需求。

- RXUSRCLK:这是一个用户时钟信号,用于驱动RXBYTEREALIGN和其他用户逻辑。

- RXUSRCLK2:这是另一个用户时钟信号,用于驱动其他用户逻辑。它可以与RXUSRCLK相同,也可以不同。

- RXOUTCLK:这是一个输出时钟信号,用于驱动其他用户逻辑。它可以与RXUSRCLK或RXUSRCLK2相同,也可以不同。

GTX的结构与组成使得它具有高灵活性,高性能和高集成度的特点,可以满足不同应用场景的需求。

个人观点,仅供参考