本文转载自:孤独的单刀的CSDN博客

前言

众所周知,Verilog是作为一种HDL(Hardware Description Language,硬件描述语言)出现的,它的主要功能是在不同的抽象层级上描述电路,从而实现电路设计。那么到底该如何描述电路?Verilog提供了3种不同的方式:

结构化描述方式(结构模型,Structural Modeling)

数据流描述方式(数据模型,Dataflow modeling)

行为级描述方式(行为模型,Behavior Modeling)

结构化描述方式

结构化描述方式是抽象级别最低的描述方式,但它也最接近底层电路的具体实现。先来看一个例子:

输入信号分别为1bit的信号A和信号B,输出信号为1bit的信号C。只有当A和B同时为逻辑1时,输出C才为逻辑1,其他情况输出C为逻辑0。

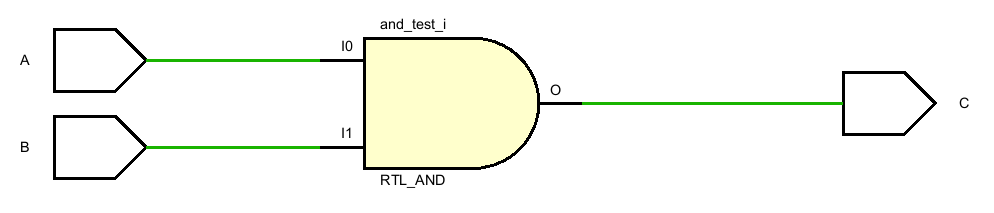

这个例子是要实现一个与门,抽象出的电路结构应该是这样的:

如果采用结构化描述方式来实现这个功能,那么就是调用一个与门:

module test(

input A,B,

output C

);

and and_test(C,A,B); //与门实现,这是与门的原语

endmodule

这种实现方式其实就是在直接用门电路来搭建电路,电路规模小的时候还好,一旦要设计的电路变大、变复杂后,再用这种方式显然就非常低效了,同时这种方式对设计人员也是一种考验与折磨。

目前,这种搭建式的方法在FPGA设计中已经不常使用了。首先,它难以描述复杂的电路;其次这种方法需要抽象出电路的具体实现,相当于本该综合工具干的活被你自己给干了,那你觉得这种工作你能干得比综合工具快?比综合工具好?

但是,结构化描述方法在日常设计中仍然以一种特殊的形式而存在–实例化(Instantiation)。由于当前的FPGA设计大多采用模块化的设计方法,所以实例化仍然必不可少。

数据流描述方式

数据流描述方式比结构化描述方式的抽象级别高一些,因为它不需要直接描述出电路的底层实现方式,而只需要对数据是如何流动的这一现象进行描述,从而实现电路功能。

仍然采用上面的例子,看看数据流描述方式是如何描述电路的:

module test(

input A,B,

output C

);

assign C = A & B;

endmodule

这种方式清晰地描述了数据从输入到输出的流动情况,即从A\B输入,彼此相与后再从C输出。

这种方法比上一种方法简单不少,原本需要用门电路搭建的电路只需要用一个 与运算符(&) 即可实现,而具体的实现方式就交给了综合工具。

行为级描述方式

行为级描述方式是抽象级别最高的描述方式,多用于大型设计。同样的例子,它是这样描述电路的:

module test(

input A,B,

output reg C

);

always@(*)begin

if(A == 1'b1 && B == 1'b1)

C = 1'b1;

else

C = 1'b0;

end

endmodule

重点在这一句“ if(A == 1’b1 && B == 1’b1) C = 1’b1;”,即描述电路的行为:只有当A和B同时为逻辑1时,输出C才为逻辑1,其他情况输出C为逻辑0。

行为级描述方式不需要抽象出电路的具体实现,也不需要管数据的流动方式,只需要对电路的外在表现,即电路的具体行为进行描述。这种方法最符合人类的直观思维,抽象级别最高,概括能力最强。

但这种方式也是有缺点的,缺点也恰恰是因为它太抽象了!所以很多时候设计人员根本就不知道底层电路是什么样子的,这使得有时候做FPGA设计,不像是在设计硬件,反而像是在设计软件!

因此在实践中,往往都是三种描述方式混用,这样既保证了一定的抽象程度,使得大规模的电路设计成为现实,同时也能让设计人员对底层电路保持一定的了解,以便对电路进行面积与速度上的优化。

半加器实例

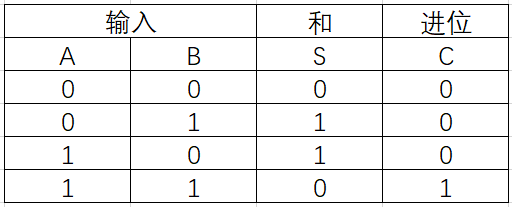

如果觉得上面的例子不够直观,那么再来看一个半加器的例子。下面是半加器的真值表:

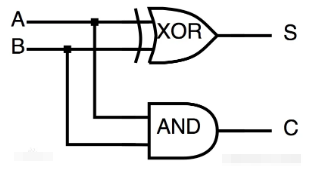

从真值表可以很快地推断出其电路的实现形式:

所以采用结构化描述方式来对半加器进行描述,是这样的:

module half_adder(

input A,B,

output S,C

);

xor xor_test(S,A,B); //异或门,底层原语

and and_test(C,A,B); //与门,底层原语

endmodule

这种方式直接描述出了电路的底层实现(用门电路实现),抽象级别很低,不适用于大规模的设计。

同样从真值表,可以推断出数据的流动方式:S = A ^ B; C = A & B; 所以用数据流描述方式来描述电路,是这样的:

module half_adder(

input A,B,

output S,C

);

assign S = A ^ B;

assign C = A & B;

endmodule

这种方式隐式地描述了电路的实现方式,同时也具备一定的抽象层级。

半加器要实现的功能就是没有进位输入、但有进位输出的两个1bit数的加法(电路行为),即 {C,S} = A + B; 所以用行为级描述方式来描述电路,是这样的:

module half_adder(

input A,B,

output S,C

);

assign {C,S} = A + B;

endmodule

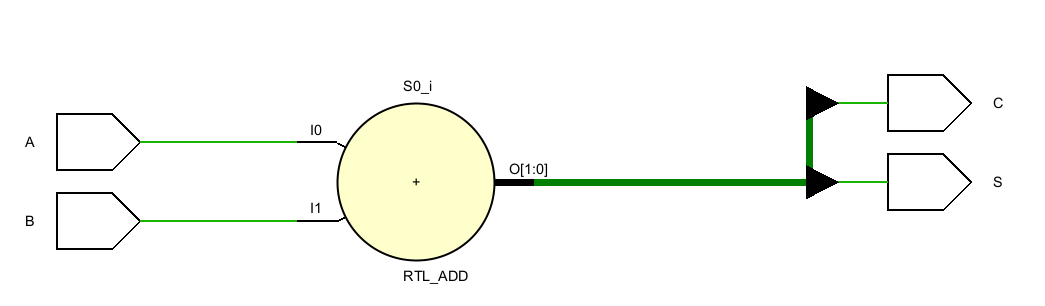

这是用vivado生成的电路:

就是个半加器,具体怎么实现的不知道(抽象级别很高),因为电路的具体实现工作被交给了综合工具。

总结

结构化描述方式抽象层级最低,但也最接近底层电路;描述大型电路时效率低,所以在当前设计中较少见,但作为其另一形式存在的实例化在实践中仍然比不可少

数据流描述方式抽象层级居中,但需要设计人员对电路有较深的理解,与行为级描述方式并称为RTL级描述

行为级描述方式抽象层级最高,不需要对底层电路有过多的理解,最符合人类大脑直觉,开发效率最高