作者:硬码农二毛哥

MRS命令

ddr在上电初始化后通过发送MRS命令配置模式寄存器。ddr上电后处于空闲状态时(所有bank完成预充电,所有突发读写完成,CKE为高),可以发送MRS命令,重新设置模式寄存器。该命令不会影响内存中的数据。

与MRS命令相关的参数有两个tMRD和tMOD,连续两个MRS命令之间要间隔tMRD,当发送完MRS命令后,要经过tMOD后才能发送其它命令。

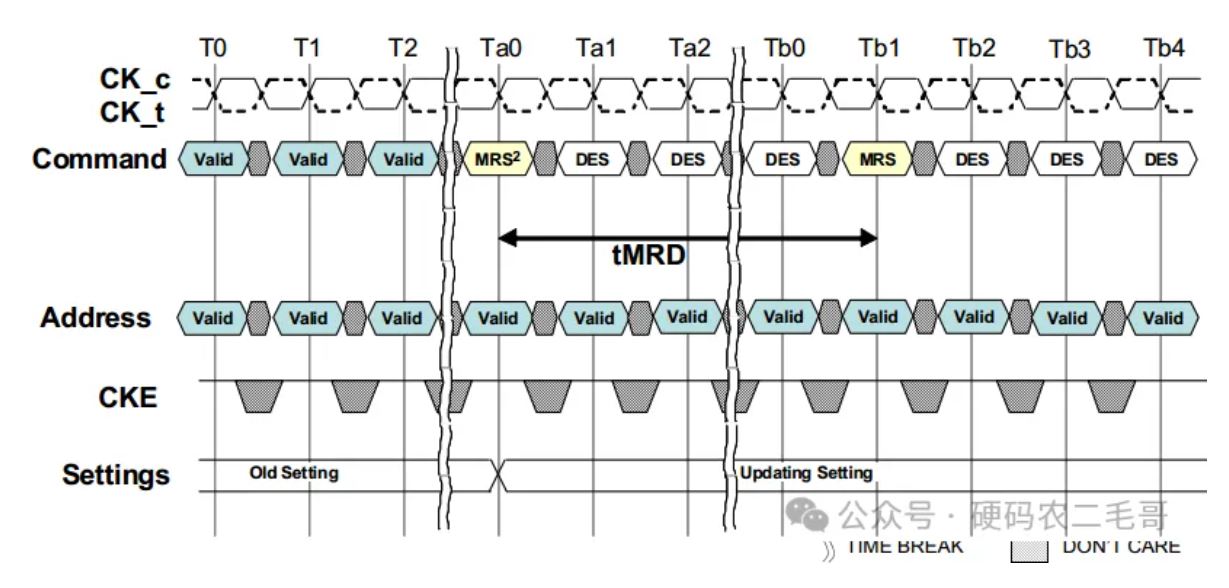

tMRD

两个MRS命令之间最小间隔是tMRD。

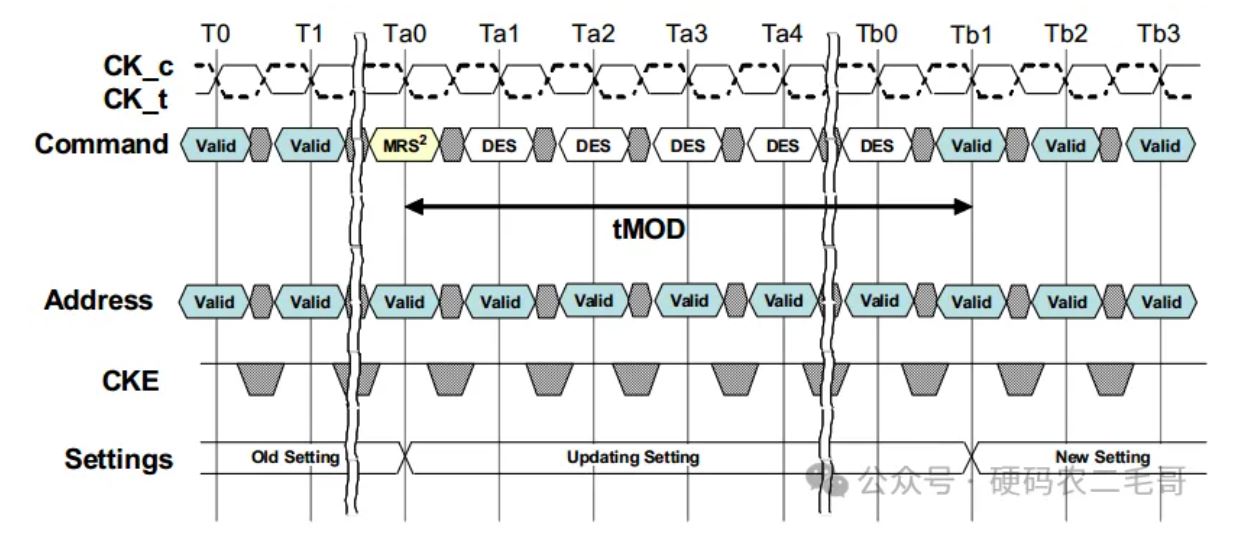

tMOD

发送MRS命令和其它命令之间最小间隔是tMOD。

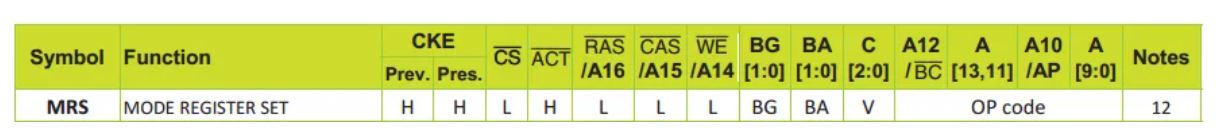

MRS命令

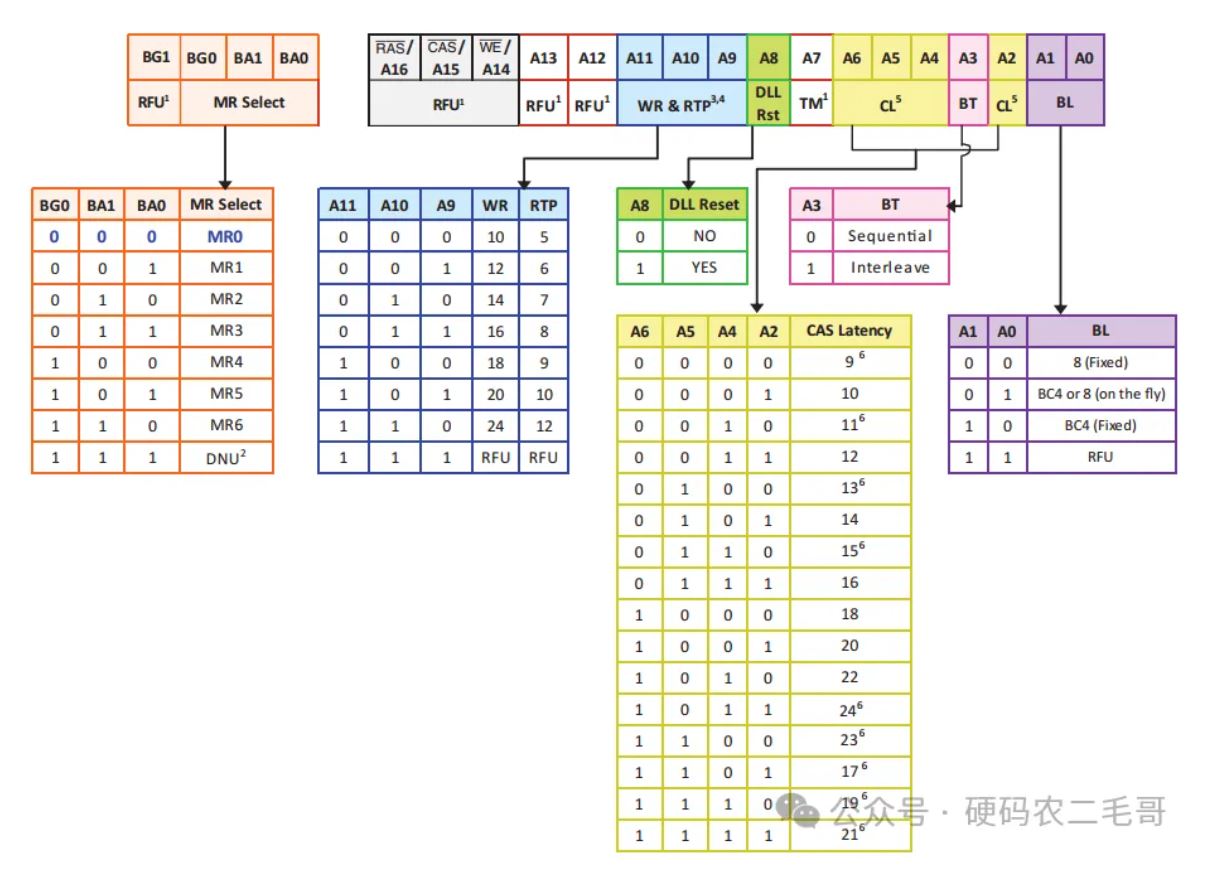

发送MRS命令时,CS为低,ACT为高,A16、A15和A14为低,BG0、BA1和BA0用来选择模式寄存器MR0-MR7。A0-A13的值设置寄存器中的参数。

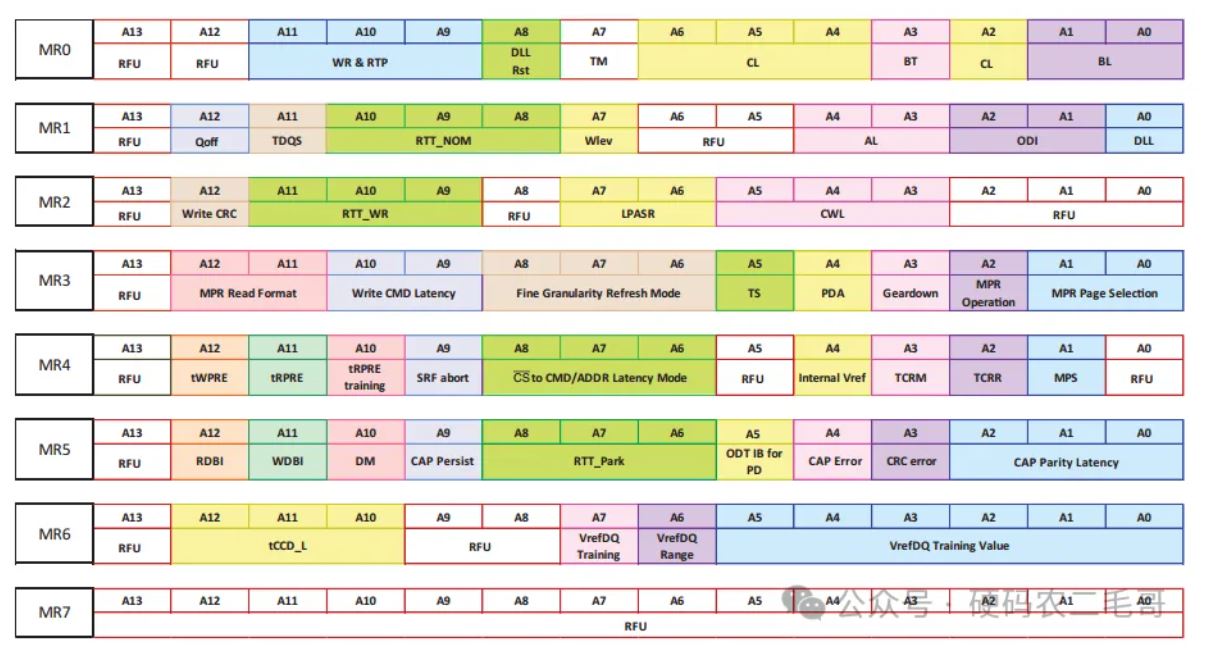

Mode Register

ddr中有7个模式寄存器(Mode Register)。

MR0

MR0

在MR0寄存器中设置BL和CL。

BL

BL

A1A0用来设置BL,设置ddr突发长度。突发长度又分为BC4和BL8。

CAS Latency(CL)

CL表示读命令发出到到第1bit数据输出的延时。

read latency(RL) = additive latency(AL) + CAS latency(CL)

AL在 MR1寄存器中设置。

MR1

在MR1寄存器中设置DLL、AL、Output Disable和TDQS。

DLL

ddr正常运行时,必须将DLL使能。A0为1使能DLL。

Output Disable

A12设置1,Output Disable使能,所有输出引脚(DQ、DQS)与ddr断开连接,正常工作时A12设置成0。

Termination Data Strobe (TDQS)

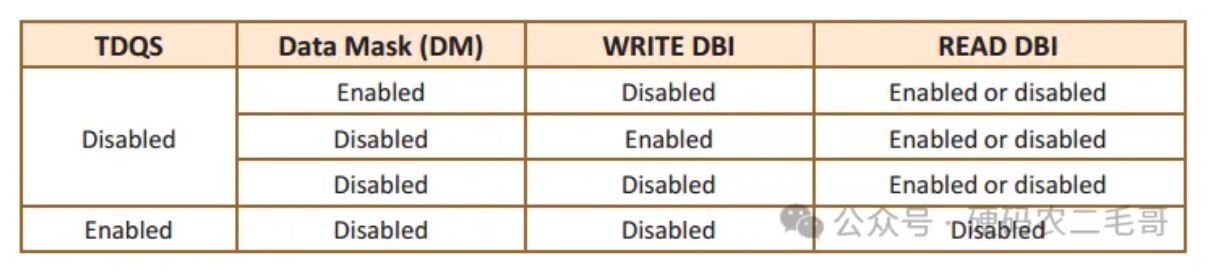

该功能在x8模式时使用,不支持x4和x16模式,不使能TDQS,将A11置0。当TDQS功能不使能时,data mask和DBI功能可以各自使能。

MR2

在MR2寄存器中设置CRC和CWL。

CAS Write Latency (CWL)

CWL表示写命令到第1bit数据输入的时间间隔。通过A5A4A3设置。

write latency (WL) = addŝƟve latency (AL) + CAS write latency

Write cyclic redundancy check (CRC)

A12置1时,使能CRC。在BL8模式数据从8bit变成10bit,多出的2bit是CRC信息。

MR3

在MR3寄存器中设置Refresh Mode和MPR。

Refresh Mode

A8A7A6设置ddr刷新模式x1、x2或x4。

MPR

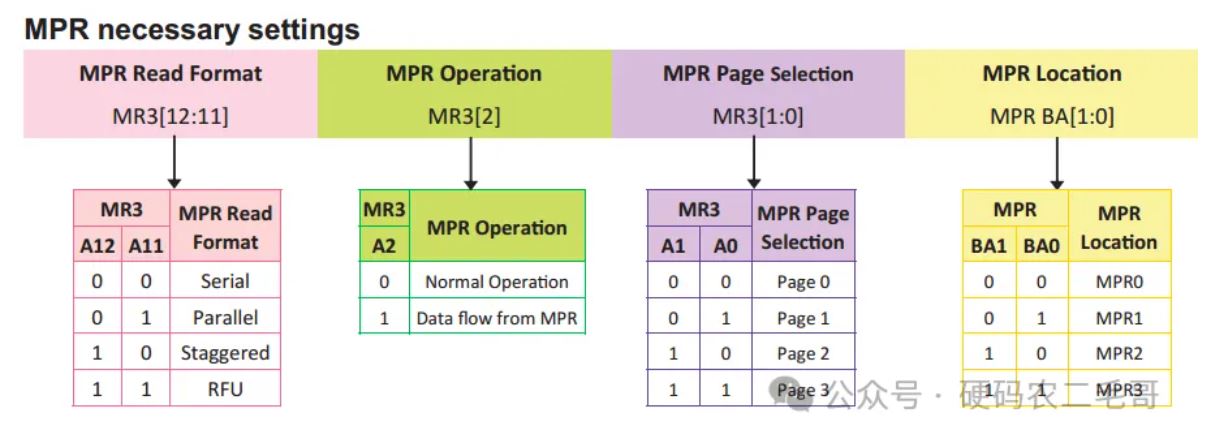

multipurpose register (MPR) ,MPR用来读写特定数据到DRAM。MPR包含4个page,从page0到page3。每页有4个8bit寄存器,MPR0到MPR3。

通过MR3寄存器可以设置MPR Read Format、MPR Operation、MPR Page Selection、MPR Location。

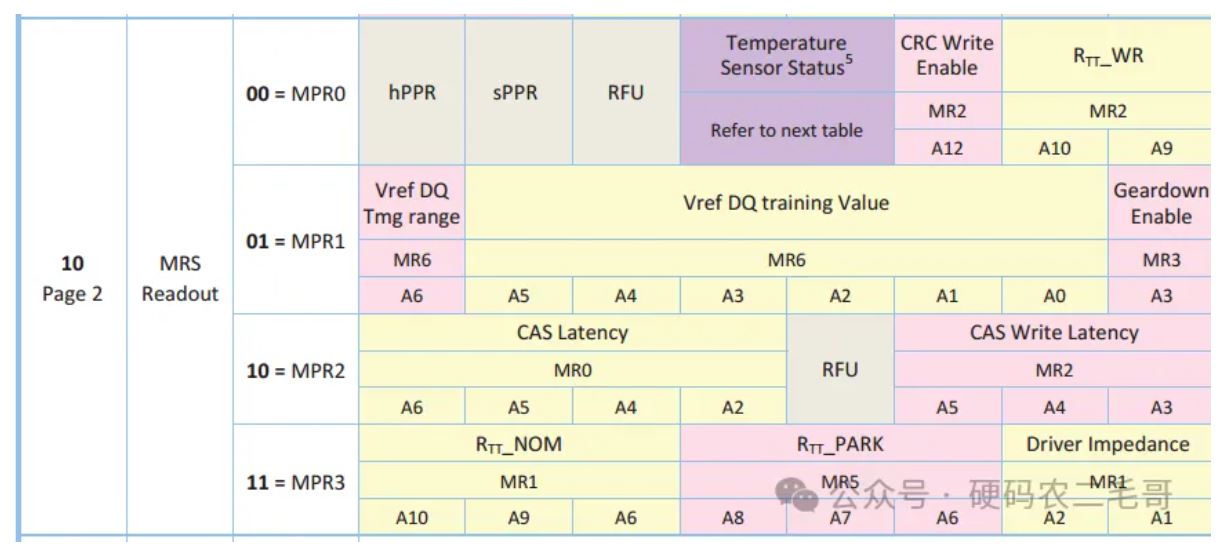

MPR Page and MPRx Definitions

通过MPR的page2可以模式寄存器中写入的数据,验证模式寄存器写入是否正常。

MR4

MR4

在MR4寄存器中设置WRITE Preamble 、READ Preamble和Maximum Power Savings Mode

WRITE Preamble

A12为0时,设置为1ck,A12为1时,设置为2ck。

READ Preamble

A11为0时,设置为1ck,A11为1时,设置为2ck。

Maximum Power Savings Mode

当A1为0时为正常运行模式,A1为1时使能maximum power saving mode 。

MR5

在MR5寄存器中设置DBI、DM和C/A Parity Latency Mode 。

READ DBI

A12为0时不使能READ DBI,A12为1时使能READ DBI。

WRITE DBI

A11为0时不使能WRITE DBI,A11为1时使能WRITE DBI。

Data mask (DM)

A10为0时不使能Data mask,A10为1时使能Data mask。

C/A Parity Latency Mode

正常运行时不是能C/A Parity Latency,A2A1A0都为0。

MR6

在MR6寄存器中设置tCCD_L、 VREFDQ Training Enable 。

tCCD_L

通过A12A11A10设置tCCD_L。

VREFDQ Training Enable

A7为0时不使能VREFDQ Training,A7为1时使能VREFDQ Training。

MR7

MR7不进行设置。