本文转载自:数字站

JESD204B延迟的定义及影响因素

延迟(Latency) 通常定义为信号从A点到B点所需要的总时长,单位通常是多少个时钟周期。

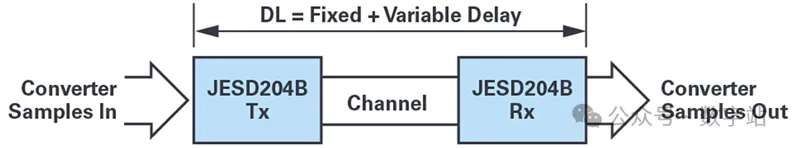

在一个JESD204B系统链路中,A点通常是发送端(TX)的输入,B点通常是接收端(RX)的弹性buffer输出,A点和B点各个节点的延时定义模型如下图所示。

图1 204B中各个节点的延迟 (Latency)定义

在JESD204B中Latency 和Delay 定义是不一样的,Latency 更偏向于具体运用中的一个广泛定义,delay是一个更具体的物理延迟。JESD204B中两个的定义如下:

1、Link Latency:从采样的并行数据被输入到发送器(ADC/FPGA),到相同的数据以并行形式出现在接收器(FPGA/DAC)的弹性buffer输出处的延迟时间。

2、Link Delay:从采样的并行数据被输入到发送器(ADC/FGPA),到相同的数据被呈现到接收器(FPGA/DAC)的弹性buffer的输入延迟时间。

延迟通常会被这些因素影响:TX/RX器件相关的因素(Serdes的串行/解串延时、SYSREF内部延迟、AD/DA内部延迟等等)、时钟相关因素(锁存Device clock并对齐的延迟、锁存SYSREF并对齐的延迟等)、时钟和SYSREF信号在PCB上的传输延迟等。

JESD204B确定性延迟的实现

JESD204B标准将确定性延迟定义为基于帧的样本到达串行发射器的时间与基于帧的样本从串行接收器输出的时间之差,核心是无论何时延迟都是恒定的。

图2 确定性延迟示意图

JESD204系统中的确定性延迟由固定延迟和可变延迟组成。可变延迟是由数字处理模块中因跨越不同时钟域导致的相位改变, 且每次上电都有可能不同。

子类一实现确定性延时的过程如下图所示,通过三个特征确保发送端的数据到接收端输出数据的延迟是恒定的。

首先使用SYSREF同步所有器件的本地多帧Local Multi-Frame Clock (LMFC)时钟,且LMFC边沿与SYSREF之间的延迟是可以设置的。其次所有发送器件(TX)在LMFC同一边沿发送ILAS序列,保证所有通道同时发送数据。

最后所有接收端(RX)通过ILAS来判断输出数据的开始和结束并和LMFC对齐,通过调整弹性缓冲器(elastic buffer:RBD)来补偿各通道上的延迟,使得接收端(RX)各通道的数据对齐输出。

图3 JESD204B中确定性延迟实现过程

参考上图,JESD204B实现确定性延迟的过程就是通道对齐的过程:

1、SYSREF用于同步TX/RX的本地多帧时钟LMFC。

2、TX当SYNC变高后,所有通道在下一个LMFC边沿开始发送ILAS序列,标注数据的开始和结束。

3、RX的各通道(有早有晚)在接收到ILAS系列中的开始字符/R/后,按照RBD开设的缓冲器的大小缓存数据。

4、RX的所有通道在下一个LMFC的上升沿(RBD=K)开始释放所有的缓冲数据,实现所有通道上的数据对齐。

经过上述过程后,发送端与接收端的数据传输延迟为LMFC周期整数倍加上接收端弹性buffer延时(RBD),其中前者为固定延时,后者为可以设置的可变延时。

SYSREF可以是单脉冲、周期方波或者带隙周期方波信号,SYREF的周期必须为LMFC周期的整数倍。

实现确定性延迟的关键-设置RBD

接收端将ILAS序列存入弹性buffer中,在LMFC边沿时,如果所有通道的弹性buffer中均有有效数据,则所有通道经过RBD延时后同时从弹性buffer中读出数据给用户。

因此设置RBD的值可以调节弹性buffer数据释放点相对于LMFC上升沿的位置,RBD的取值范围[1,K],其中K表示每个多帧包含的帧数,通常取值为32。

例如RBD=K表示在下一个LMFC的上升沿读出接收端(RX)所有通道弹性buffer的数据,与图3一致。如果RBD=K-5,则表示在下一个LMFC上升沿之前的5个帧周期读出接收端(RX)所有通道弹性buffer的数据。

设置RBD可能引发的问题

在实际使用时往往将RBD设置为K=32最大值,这样的设置实际运用存在风险,当链路的延迟发生变化时很可能导致不确定性延迟的产生。

设置K=32仅仅能应对的是在各种情况下(如高低温)最短和最长lane之间的延迟在一个多帧的范围内,如果lane的最长和最短的延迟超过一个多帧,那么当链路延迟发生变化时会导致延迟也产生了变化。

如下图所示,设置RBD=K,假设LMFC周期为50ns,链路延时的范围是100ns±10ns。

下图中左边是假设链路延时为最小的90ns的情况,右图是链路延时为110ns的情况,当RBD设置为32时,两种情况下会导致延时从100ns变为150ns,多了一个LMFC的时间,从而导致延时不确定。发生延迟不确定的原因是lane上的最短和最长延迟跨越了一个多帧的边缘。

图4 JESD204B中RBD设置不恰当导致延迟不确定

可以将RBD设置为K的一半来解决上述问题,在延时125ns处可以保证所有通道的弹性buffer均有有效数据,保证每次均会在同一个时间点释放数据。

图5 JESD204B中恰当的设置RBD值确保延迟的确定性

搜索RBD最优值

在实际开发中,可以使用如下方法获取RBD最优值。

把RBD的值从K逐渐减小,直到观察到延迟有一个LMFC周期跳动为止。

下图中蓝色所示RBD的值从大(Max)到小(Min),那么延迟(total latency)的值也将从大到小变化,但当RBD变为Min时,发现延迟(total latency)并不是最小,而是跳到了最大处(图中绿色箭头所示)。

图6 JESD204B中最优的RBD值搜索示意图

将上述过程的Min设置为RBD的边界值,再将(Max-Min)/2的值加上边界值作为最优RBD值,如上图的最优RBD箭头所示。